[RISC-V]移植rtthread nano到risc-v芯片

本文由RT-Thread论坛用户@DENGCHOW原创发布:https://club.rt-thread.org/ask/article/3187.html

“这么说吧,就是为了这口醋,我才包的这顿饺子。”

仓库地址:https://gitee.com/dengchow/yuheng-riscv-soc.git

〇、前言

本文记录的是在 risc-v 芯片上移植 rt-thread nano 的过程。

使用到的 risc-v 芯片是玉衡(YuHeng,yuheng-riscv),一款并不存在于现实世界的芯片,同 picorv32 和 darkriscv 一样,仅存在与仿真环境中。

一、硬件平台

玉衡(YuHeng,yuheng-riscv)基于开源 RISC-V 指令集架构,是一款极简的 32 位 RISC-V 处理器核。仅用于检测和实验。

玉衡不具备任何商用价值,但可以作为很好的学习平台。

使用玉衡,能够很好的了解计算机体系结构、操作系统、通信协议、编译原理等相关知识。

另外,所有的运行环境均为精简搭建,因此还可以很轻易的熟悉搭建过程。

不仅会用,还要知道为什么会用。是当初设计的初衷。

特点与功能

-

支持 RV32IMFD 扩展指令集,通过RISC-V指令兼容性测试

-

采用五级流水线设计:IF、ID、EX、MEM、WB

-

采用自定义的总线设计:RBM(RISC-V Bus Matrix)

-

支持中断:矢量中断和非矢量中断

-

支持多种外设: UART、TIMER 等

-

支持 C 程序运行

-

支持 RT-Thread Nano 3.1.5

-

支持 UART 模拟器,可在仿真环境中进行调试

-

…

二、软件平台

rtthread nano 的版本是 3.1.5,直接从官网上下载的。

之所以不使用完整版 rt-thread,是因为我个人认为 rt-thread 的精华是 kernel 和 FinSH。

因此 rtthread nano 足够了。

其实根本的原因是 YuHeng 上只有最最基本的外设,除了 UART 就是 TIMER。惭愧。

三、移植过程

移植过程比较特殊,因为是先有的 rtthread nano,然后才去改造的 yuheng-riscv。

最终效果

-

使用项目中给出的运行脚本,可以直接创建出 Vivado 工程。

-

为了方便 Simulation,设计一个 uart_monitor,有了它之后,就可以直接在 testbench 中捕捉 UART 的输出。

- 仿真是比较慢的。

- 由于是在 Vivado 上进行 Simulation,可以监视任何一个信号。

- 从 wave 和 log 两个角度进行结果输出。

接下来,介绍一下移植过程。

移植过程

rtthread 调度线程的时候使用到 rt_hw_context_switch 和 rt_hw_context_switch_to 两个函数。

而这两个函数实际并没有真的去切换线程,在 ARM Cortex 中会触发 PendSV 中断,在 PendSV 中完成的线程切换。

在中科蓝讯的 ab32vg1 中,是有一个 low_prio_irq 的,作用和 PendSV 是一样的。

很尴尬, yuheng-riscv 中是没有类似的设置。

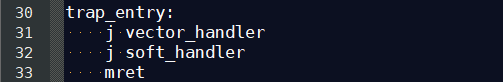

在设计 yuheng-riscv 是只有非矢量中断的,即只有一个固定的中断 trap_handler,然后通过软件来构建中断向量表。

如 sdk\rtthread-nano\interrupt.c 中所示。

本着尽量不改动 rtthread nano 源码的出发点,决定对 yuheng-riscv 的中断机制进行修改。

- 增加硬件中断向量表。

- 增加 soft_handler 中断用于线程切换。

剩余的移植工作如 tick 的添加, UART 的添加,这个就不做介绍了,毕竟 rtthread nano 中通过 TODO 都进行标识了。

一步一步的修改添加即可。

四、总结

总之,rtthread 还是很友好的。

整体来说 yuheng-riscv 还只是一个 demo,功能是有了,性能还是差不少。

“醋还行,饺子差点。”

![[RISC-V]移植rtthread nano到risc-v芯片_第1张图片](http://img.e-com-net.com/image/info8/fcc8a5d5039e44d7a97af0d2caa35f97.jpg)

![[RISC-V]移植rtthread nano到risc-v芯片_第2张图片](http://img.e-com-net.com/image/info8/d7891678b95445aa8d8aec8ab8562678.gif)

![[RISC-V]移植rtthread nano到risc-v芯片_第3张图片](http://img.e-com-net.com/image/info8/40522c11284c4549942f3ddad08e1cf7.gif)

![[RISC-V]移植rtthread nano到risc-v芯片_第4张图片](http://img.e-com-net.com/image/info8/098a54823104493db6a9fca728f81970.gif)

![[RISC-V]移植rtthread nano到risc-v芯片_第5张图片](http://img.e-com-net.com/image/info8/ea7358afbd264e858ffa7693ab96b376.gif)

![[RISC-V]移植rtthread nano到risc-v芯片_第6张图片](http://img.e-com-net.com/image/info8/fd0db0cfcf9d45bba030d590945ba154.png)

![[RISC-V]移植rtthread nano到risc-v芯片_第7张图片](http://img.e-com-net.com/image/info8/a1ccacc2a73a445ab5ea2797ea3f8e5a.png)

![[RISC-V]移植rtthread nano到risc-v芯片_第8张图片](http://img.e-com-net.com/image/info8/66cb893c1e974ba08810201ba2cdae70.png)

![[RISC-V]移植rtthread nano到risc-v芯片_第9张图片](http://img.e-com-net.com/image/info8/f042df2093b541df82ea55f9e9dfe7b4.jpg)