ip打包后如何加入 xilinx_10G以太网接口(三):IP核的配置

感觉IP核的配置还能再水一篇专栏文章

以下诸多内容也将翻译理解自IP核的用户手册,具体参考详见最后的参考文献。

本系列将会分为:基本知识、接口的基本结构、IP核的配置、接口的测试与使用等章节。

前面两篇文章简单介绍了10G以太网和以太网接口的基本结构,如果忘记了的可以回头再去看看⬇️。

十二点过九分:10G以太网接口(一):基本知识zhuanlan.zhihu.com 十二点过九分:10G以太网接口(二):接口的基本结构zhuanlan.zhihu.com本篇文章主要是讲IP核的配置,鉴于Xilinx的7系和UltraScale+系列FPGA在架构上的不同,部分IP核也有所区别,所以本文把这两种FPGA所对应的10G以太网接口的IP核的配置都介绍一遍,以便参考。

需要注意的是:

- 本次实验用板选用的是:搭载7系芯片的VC707评估板、搭载UltraScale+系列芯片的KCU116评估板;

- 两者选用的IP核分别为:10G Ethernet Subsystem(3.1)、10G/25G Ethernet Subsystem(2.5)。

10G Ethernet Subsystem(3.1)

这个IP核支持7系、Zynq和UltraScale的FPGA,详见下图[1]。以下诸多内容主要参考理解自Xilinx的文档PG157。

10G Ethernet Subsystem 所支持的芯片- IP核配置界面

该部分可以参考手册PG157的第156页到172页。

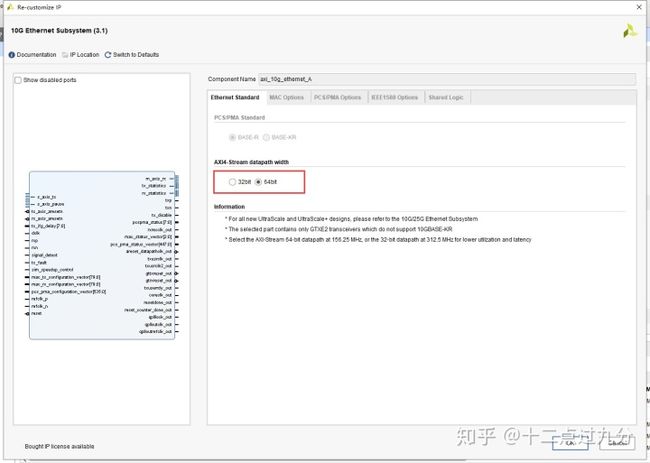

Ethernet Standard 界面如下,能选的只有数据位宽,32 bit位宽对应312.5 MHz时钟频率,64 bit对应156.25 MHz。这里选64 bit。

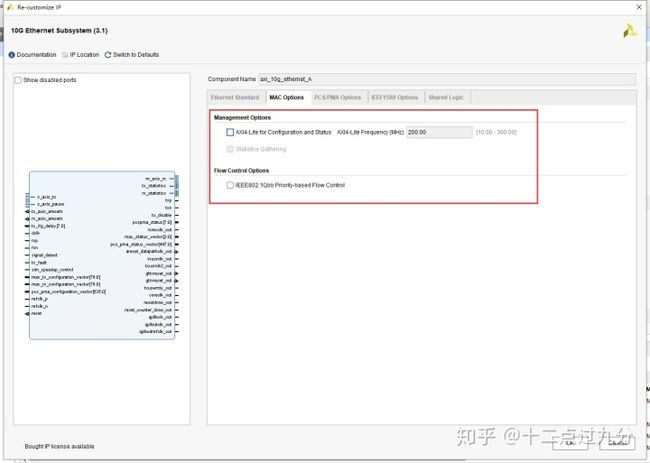

Ethernet Standard 界面MAC options 界面如下,能勾选的只有两个,IP核的配置与流控制。其中配置勾上的话即选用AXI4-Lite作为配置信号接口,不勾的话就是多出很多配置vector自行配置。这里均不勾选。

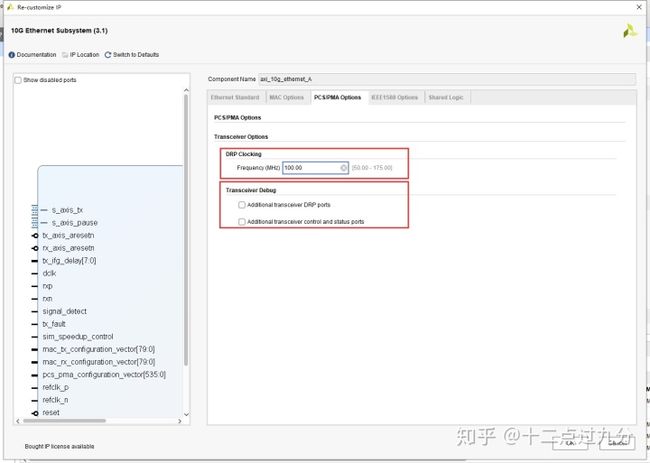

MAC options 界面PCS/PMA options 界面如下图,可选择的是DRP clocking的频率和收发器Debug选项,DRP clocking用于IP核的一些初始化等操作,使用中输入的频率和设置的频率一致。这里选100 MHz、其他不勾选。

PCS/PMA options 界面shared logic 界面如下图所示。在许多IP核中有这个选项,主要用于多个相同IP核使用时可以共用部分资源以达到节省资源的目的,这里所共用的就是一些与时钟相关的资源,在前一篇文章中所有介绍,可以去回顾下。如果该IP核是被分享的即勾选上项(完整的),如果该IP核是节省部分资源要共享自其他的勾选下项(不完整的)。

shared logic 界面- IP核例化

重点来了,在配置好IP核的一些基本内容并生成后,它的例化接口信号特别特别的多,如果不采用在block design中自动连线的方法似乎难以接线,笔者在这里简单的把这些信号线进行分类加注解,以便使用。

当然以下截图的内容仅供参考,不完全对,更详细的解释详见手册PG157的第15页到第49页。

- 其他

如果使用这个IP核去设计多个通道的以太网接口时,若这些通道中以4个为一组在同一Bank中时,可以参考前一篇文章中提到的方法去设计,即使用shared logic功能实现4个通道共用部分资源的设计方法。

10G/25G Ethernet Subsystem(2.5)

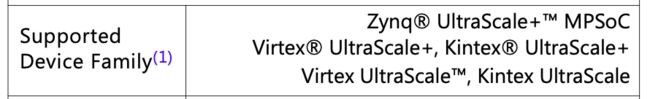

这个IP核仅支持UtlraScale架构的FPGA,详见下图[2]。

10G/25G Ethernet Subsystem所支持的芯片- IP核配置界面

该部分可以参考手册PG210的第183页到191页。

Board界面如下,保持默认就好。

Board 界面Configuration 界面如下,这部分内容较多,需要注意的是:

- General的选项可参考自下面,选择PCS/PMA+MAC 64 bit的、速度选择10.3125 G,数据接口选择AXI-Stream的,具体意思可参见前两篇文章;

- Num of cores根据需求选择,1对应一个10G通道、4对应4个10G通道,就不用与上面那个IP核一样配置4个10G需要1+3操作了;

- R/KR标准选择BASE-R;

- 控制与状态信号选择control and status vectors,当然熟悉AXI-Lite的也可以采用这个作为相关配置的总线协议。

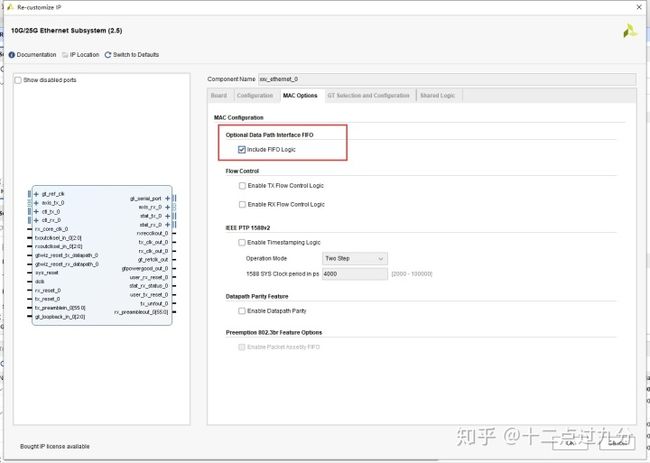

MAC options 界面如下,FIFO logic主要在RX端增加FIFO用于接收的数据缓存和跨时钟处理,如果有低时延的要求的话可以不勾。其他选项可不勾选。

MAC options 界面GT Selection and Configuration 界面如下所示,该界面主要用于选择与高速收发器相关的内容:GT Refclk即收发器的参考时钟,可以选的不多,根据设计中能提供的参考时钟选择,这里选择156.25 MHz;DRP Clocking与前一致,选择100 MHz;GT Type和GT Selection根据板子上提供的收发器的不同进行勾选,例如KCU116是GTY收发器、10G/25G口是在 Quad X0Y2上,如果只选择一个10G通道,可如图勾选。

GT Selection and Configuration 界面shared logic 界面如图所示,可按图勾选。

shared logic 界面- IP核例化

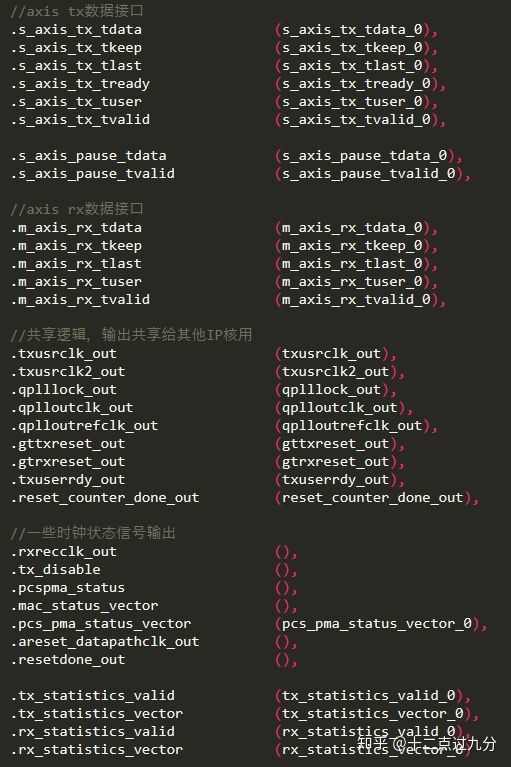

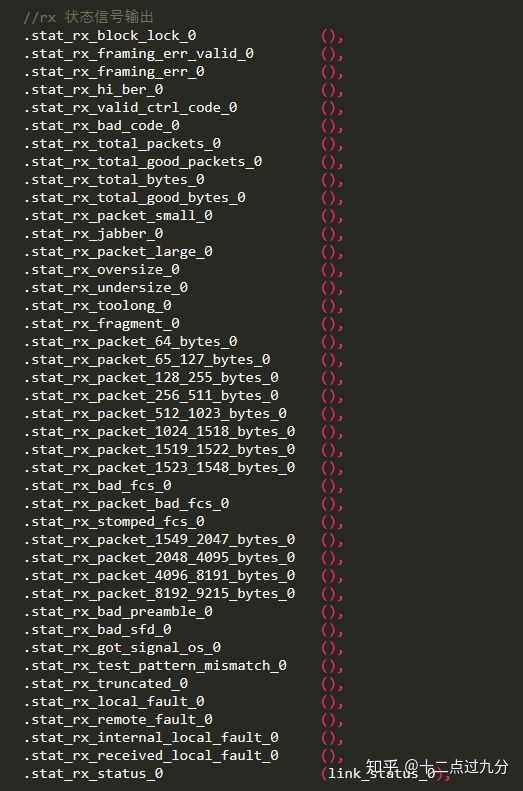

与前一个IP核一样,简单的把诸多的接口信号进行分类注解,以便理解,但仅供参考,具体各信号描述详见手册PG210的第15页到第78页。

以上IP核接口信号仅是勾选一个10G通道对应的内容,如果勾选了n个通道(2-4个)应该信号线会更加的多,大致多出的信号就是后三张图的信号*n。

- 其他

有疑惑的是,笔者没有实际使用过该IP核的shared logic的功能,只用过前一个IP核的该功能,觉得10G/25G IP核已经可以在一个IP核下支持4个10G/25G的通道,就不大清楚它的shared logic功能是用来干嘛的了(当然主要是懒没有详细去参看文档了)。

简单小结

单从IP核的配置而言并不复杂,可以参考上面笔者选项勾选,如果对一些没提到的东西有所疑惑,也可以直接去参考Xilinx提供的IP核手册PG157、PG210。

需要的注意的选项在“其他”中也有所提到,就是当实际使用场景中需要多个10G口的时候,两种IP核配置使用的方式会有所区别。

10G以太网接口(三):IP核的配置 就介绍到这儿,(四)已经补上,如下所示 。

十二点过九分:10G以太网接口(四):测试与使用zhuanlan.zhihu.com写在最后:

以上简单介绍了两个不同10G IP核的简单配置,可能这篇文章是本系列最重要的一部分了,稍微有点长,不过这部分结束,接下来的测试与使用就基本没啥了。

鉴于笔者学习理解程度不够,以上内容仅供参考,如果疑惑之处可以一同讨论,若存在不足之处还望批评指正~

参考

- ^Xilinx文档PG157的第4页

- ^Xilinx文档PG210的第4页