Verilog语法学习(1)

过程语句(initial、always)

在一个模块(module)中initial语句常用于仿真中的初始化,always可用于仿真和可综合电路initial过程块中的语句仅执行一次;always块内的语句则是不断重复执行的。使用initial和always语句的次数是不受限制的。

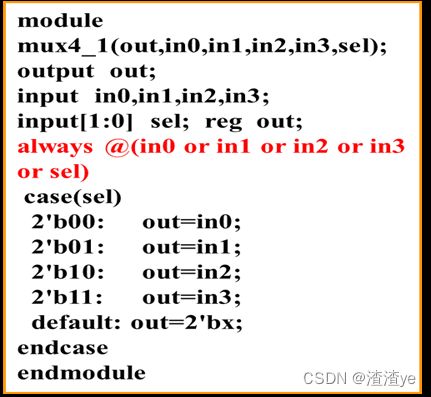

module mux4_1(out,in0,in1,in2,in3,sel);

output out;

input in0,in1,in2,in3;

input[1:0] sel; reg out;

always @(in0 or in1 or in2 or in3 or sel)

case(sel)

2'b00: out=in0;

2'b01: out=in1;

2'b10: out=in2;

2'b11: out=in3;

default: out=2'bx;

endcase

endmodule·timescale 1ns/1ns

module mux4_TB;

reg tin0,tin1,tin2,tin3;

reg[1:0] tsel;

initial

begin

tin0=0; tin1=1;tin2=0;tin3=1;

#5 tsel=0;

#5 tsel=1;

#5 tsel=2;

#5 tsel=3;

$stop;

end

mux4_1 m1(tout,tin0,tin1,tin2,tin3,tsel);

endmodule

always过程语句格式

always @(<敏感信号表达式event-expression>)begin 过程赋值if-else,case,casex,casez选择语句while,repeat,for循环task,function调用end“always”过程语句通常是带有触发条件的,触发条件写在敏感信号表达式中,只有当触发条件满足时, “begin-end”块语句才能被执行。

事件表达式或敏感信号列表

always @(<敏感信号表达式event-expression>)作用:当表达式中变量的值改变,就会引发块内语句的执行。列出影响块内取值的所有信号。用“or”、“,”连接;信号形式要统一(电平信号、边沿信号)。

例如: always@(a) // 当信号 a 的值发生改变always @(a , b) // 当信号 a 或信号 b 的值发生改变always @* 或 @ (* ) // 所有驱动信号always @( posedge clock) // 当 clock 的上升沿到来时always @( negedge clock) // 当 clock 的下降沿到来时always @( posedge clk , negedge reset)当 clk 的上升沿到来或 reset 信号的下降沿 到来

posedge和negedge

对于 时序电路, 事件通常是由 时钟边沿触发 的;【 例 】 同步置数(高电平)、同步清零(低电平)的模 256 的计数器 。

同步/异步、高/低电平有效

时钟 clk 使能信号 reset loadalways@ ( posedge clk ) //reset 、 load 同步信号always@ ( posedge clk , posedge reset ) //reset 异步(高), load 同步always@ ( posedge clk , posedge reset , negedge load )reset异步(高)、load异步(低)

出现 在 敏感列表 中的使能信号,都是异步信号, 不出现 是 同步;异步使能 信号, posedge 对应 高电平 有效, negedge 对应 低电平 有效。

always @(posedge clk) //clk上升沿触发

begin

if(!reset) out=8'h00; //同步清0,低电平有效

else if(load) out=data; //同步预置

else out=out+1; //计数

end

always @(posedge clk,posedge load) //clk上升沿触发

begin

if(!reset) out=8'h00; //同步清0,低电平有效

else if(load) out=data; //异步预置,高电平有效

else out=out+1; //计数

end

always @(posedge clk,negedge reset) //clk上升沿触发

begin

if(!reset) out=8‘h00; //异步清0,低电平有效

else if(load) out=data; //同步预置

else out=out+1; //计数

end