- element实现动态路由+面包屑

软件技术NINI

vue案例vue.js前端

el-breadcrumb是ElementUI组件库中的一个面包屑导航组件,它用于显示当前页面的路径,帮助用户快速理解和导航到应用的各个部分。在Vue.js项目中,如果你已经安装了ElementUI,就可以很方便地使用el-breadcrumb组件。以下是一个基本的使用示例:安装ElementUI(如果你还没有安装的话):你可以通过npm或yarn来安装ElementUI。bash复制代码npmi

- 理解Gunicorn:Python WSGI服务器的基石

范范0825

ipythonlinux运维

理解Gunicorn:PythonWSGI服务器的基石介绍Gunicorn,全称GreenUnicorn,是一个为PythonWSGI(WebServerGatewayInterface)应用设计的高效、轻量级HTTP服务器。作为PythonWeb应用部署的常用工具,Gunicorn以其高性能和易用性著称。本文将介绍Gunicorn的基本概念、安装和配置,帮助初学者快速上手。1.什么是Gunico

- swagger访问路径

igotyback

swagger

Swagger2.x版本访问地址:http://{ip}:{port}/{context-path}/swagger-ui.html{ip}是你的服务器IP地址。{port}是你的应用服务端口,通常为8080。{context-path}是你的应用上下文路径,如果应用部署在根路径下,则为空。Swagger3.x版本对于Swagger3.x版本(也称为OpenAPI3)访问地址:http://{ip

- 如何在 Fork 的 GitHub 项目中保留自己的修改并同步上游更新?github_fork_update

iBaoxing

github

如何在Fork的GitHub项目中保留自己的修改并同步上游更新?在GitHub上Fork了一个项目后,你可能会对项目进行一些修改,同时原作者也在不断更新。如果想要在保留自己修改的基础上,同步原作者的最新更新,很多人会不知所措。本文将详细讲解如何在不丢失自己改动的情况下,将上游仓库的更新合并到自己的仓库中。问题描述假设你在GitHub上Fork了一个项目,并基于该项目做了一些修改,随后你发现原作者对

- 店群合一模式下的社区团购新发展——结合链动 2+1 模式、AI 智能名片与 S2B2C 商城小程序源码

说私域

人工智能小程序

摘要:本文探讨了店群合一的社区团购平台在当今商业环境中的重要性和优势。通过分析店群合一模式如何将互联网社群与线下终端紧密结合,阐述了链动2+1模式、AI智能名片和S2B2C商城小程序源码在这一模式中的应用价值。这些创新元素的结合为社区团购带来了新的机遇,提升了用户信任感、拓展了营销渠道,并实现了线上线下的完美融合。一、引言随着互联网技术的不断发展,社区团购作为一种新兴的商业模式,在满足消费者日常需

- Python数据分析与可视化实战指南

William数据分析

pythonpython数据

在数据驱动的时代,Python因其简洁的语法、强大的库生态系统以及活跃的社区,成为了数据分析与可视化的首选语言。本文将通过一个详细的案例,带领大家学习如何使用Python进行数据分析,并通过可视化来直观呈现分析结果。一、环境准备1.1安装必要库在开始数据分析和可视化之前,我们需要安装一些常用的库。主要包括pandas、numpy、matplotlib和seaborn等。这些库分别用于数据处理、数学

- 腾讯云技术深度探索:构建高效云原生微服务架构

我的运维人生

云原生架构腾讯云运维开发技术共享

腾讯云技术深度探索:构建高效云原生微服务架构在当今快速发展的技术环境中,云原生技术已成为企业数字化转型的关键驱动力。腾讯云作为行业领先的云服务提供商,不断推出创新的产品和技术,助力企业构建高效、可扩展的云原生微服务架构。本文将深入探讨腾讯云在微服务领域的最新进展,并通过一个实际案例展示如何在腾讯云平台上构建云原生应用。腾讯云微服务架构概览腾讯云微服务架构基于云原生理念,旨在帮助企业快速实现应用的容

- Python教程:一文了解使用Python处理XPath

旦莫

Python进阶python开发语言

目录1.环境准备1.1安装lxml1.2验证安装2.XPath基础2.1什么是XPath?2.2XPath语法2.3示例XML文档3.使用lxml解析XML3.1解析XML文档3.2查看解析结果4.XPath查询4.1基本路径查询4.2使用属性查询4.3查询多个节点5.XPath的高级用法5.1使用逻辑运算符5.2使用函数6.实战案例6.1从网页抓取数据6.1.1安装Requests库6.1.2代

- 基于社交网络算法优化的二维最大熵图像分割

智能算法研学社(Jack旭)

智能优化算法应用图像分割算法php开发语言

智能优化算法应用:基于社交网络优化的二维最大熵图像阈值分割-附代码文章目录智能优化算法应用:基于社交网络优化的二维最大熵图像阈值分割-附代码1.前言2.二维最大熵阈值分割原理3.基于社交网络优化的多阈值分割4.算法结果:5.参考文献:6.Matlab代码摘要:本文介绍基于最大熵的图像分割,并且应用社交网络算法进行阈值寻优。1.前言阅读此文章前,请阅读《图像分割:直方图区域划分及信息统计介绍》htt

- 使用 FinalShell 进行远程连接(ssh 远程连接 Linux 服务器)

编程经验分享

开发工具服务器sshlinux

目录前言基本使用教程新建远程连接连接主机自定义命令路由追踪前言后端开发,必然需要和服务器打交道,部署应用,排查问题,查看运行日志等等。一般服务器都是集中部署在机房中,也有一些直接是云服务器,总而言之,程序员不可能直接和服务器直接操作,一般都是通过ssh连接来登录服务器。刚接触远程连接时,使用的是XSHELL来远程连接服务器,连接上就能够操作远程服务器了,但是仅用XSHELL并没有上传下载文件的功能

- 2020-04-12每天三百字之连接与替代

冷眼看潮

不知道是不是好为人师,有时候还真想和别人分享一下我对某些现象的看法或者解释。人类社会不断发展进步的过程,就是不断连接与替代的过程。人类发现了火并应用火以后,告别了茹毛饮血的野兽般的原始生活(火烧、烹饪替代了生食)人类用石器代替了完全手工,工具的使用使人类进步一大步。类似这样的替代还有很多,随着科技的发展,有更多的原始的事物被替代,代之以更高效、更先进的技术。在近现代,汽车替代了马车,高速公路和铁路

- 【加密社】Solidity 中的事件机制及其应用

加密社

闲侃区块链智能合约区块链

加密社引言在Solidity合约开发过程中,事件(Events)是一种非常重要的机制。它们不仅能够让开发者记录智能合约的重要状态变更,还能够让外部系统(如前端应用)监听这些状态的变化。本文将详细介绍Solidity中的事件机制以及如何利用不同的手段来触发、监听和获取这些事件。事件存储的地方当我们在Solidity合约中使用emit关键字触发事件时,该事件会被记录在区块链的交易收据中。具体而言,事件

- 使用Faiss进行高效相似度搜索

llzwxh888

faisspython

在现代AI应用中,快速和高效的相似度搜索是至关重要的。Faiss(FacebookAISimilaritySearch)是一个专门用于快速相似度搜索和聚类的库,特别适用于高维向量。本文将介绍如何使用Faiss来进行相似度搜索,并结合Python代码演示其基本用法。什么是Faiss?Faiss是一个由FacebookAIResearch团队开发的开源库,主要用于高维向量的相似性搜索和聚类。Faiss

- 使用Apify加载Twitter消息以进行微调的完整指南

nseejrukjhad

twittereasyui前端python

#使用Apify加载Twitter消息以进行微调的完整指南##引言在自然语言处理领域,微调模型以适应特定任务是提升模型性能的常见方法。本文将介绍如何使用Apify从Twitter导出聊天信息,以便进一步进行微调。##主要内容###使用Apify导出推文首先,我们需要从Twitter导出推文。Apify可以帮助我们做到这一点。通过Apify的强大功能,我们可以批量抓取和导出数据,适用于各类应用场景。

- 深入理解 MultiQueryRetriever:提升向量数据库检索效果的强大工具

nseejrukjhad

数据库python

深入理解MultiQueryRetriever:提升向量数据库检索效果的强大工具引言在人工智能和自然语言处理领域,高效准确的信息检索一直是一个关键挑战。传统的基于距离的向量数据库检索方法虽然广泛应用,但仍存在一些局限性。本文将介绍一种创新的解决方案:MultiQueryRetriever,它通过自动生成多个查询视角来增强检索效果,提高结果的相关性和多样性。MultiQueryRetriever的工

- 利用LangChain的StackExchange组件实现智能问答系统

nseejrukjhad

langchainmicrosoft数据库python

利用LangChain的StackExchange组件实现智能问答系统引言在当今的软件开发世界中,StackOverflow已经成为程序员解决问题的首选平台之一。而LangChain作为一个强大的AI应用开发框架,提供了StackExchange组件,使我们能够轻松地将StackOverflow的海量知识库集成到我们的应用中。本文将详细介绍如何使用LangChain的StackExchange组件

- 在一台Ubuntu计算机上构建Hyperledger Fabric网络

落叶无声9

区块链超级账本Hyperledgerfabric区块链ubuntu构建hyperledgerfabric

在一台Ubuntu计算机上构建HyperledgerFabric网络Hyperledgerfabric是一个开源的区块链应用程序平台,为开发基于区块链的应用程序提供了一个起点。当我们提到HyperledgerFabric网络时,我们指的是使用HyperledgerFabric的正在运行的系统。即使只使用最少数量的组件,部署Fabric网络也不是一件容易的事。Fabric社区创建了一个名为Cello

- MongoDB Oplog 窗口

喝醉酒的小白

MongoDB运维

在MongoDB中,oplog(操作日志)是一个特殊的日志系统,用于记录对数据库的所有写操作。oplog允许副本集成员(通常是从节点)应用主节点上已经执行的操作,从而保持数据的一致性。它是MongoDB副本集实现数据复制的基础。MongoDBOplog窗口oplog窗口是指在MongoDB副本集中,从节点可以用来同步数据的时间范围。这个窗口通常由以下因素决定:Oplog大小:oplog的大小是有限

- pyecharts——绘制柱形图折线图

2224070247

信息可视化pythonjava数据可视化

一、pyecharts概述自2013年6月百度EFE(ExcellentFrontEnd)数据可视化团队研发的ECharts1.0发布到GitHub网站以来,ECharts一直备受业界权威的关注并获得广泛好评,成为目前成熟且流行的数据可视化图表工具,被应用到诸多数据可视化的开发领域。Python作为数据分析领域最受欢迎的语言,也加入ECharts的使用行列,并研发出方便Python开发者使用的数据

- CX8836:小体积大功率升降压方案推荐(附Demo设计指南)

诚芯微科技

社交电子

CX8836是一颗同步四开关单向升降压控制器,在4.5V-40V宽输入电压范围内稳定工作,持续负载电流10A,能够在输入高于或低于输出电压时稳定调节输出电压,可适用于USBPD快充、车载充电器、HUB、汽车启停系统、工业PC电源等多种升降压应用场合,为大功率TYPE-CPD车载充电器提供最优解决方案。提供CX8836Demo测试、CX8836样品申请及CX8836方案开发技术支持。CX8836同升

- 穷人做什么生意最赚钱?10个适合穷人赚钱的路子?

氧惠爱高省

不管在什么地方,一般都是穷人占大量数,而富人只有少数,但是它们却掌握着大量的财富。对于穷人来说,想要买车、买房等奢侈品就难如登天,因为他们只能通过打工来赚取几千元的月薪。➤推荐网购返利app“氧惠”,一个领隐藏优惠券+现金返利的平台。氧惠只提供领券返利链接,下单全程都在淘宝、京东、拼多多等原平台,更支持抖音、快手电商、外卖红包返利等。(应用市场搜“氧惠”下载,邀请码:521521,全网优惠上氧惠!

- 01-Git初识

Meereen

Gitgit

01-Git初识概念:一个免费开源,分布式的代码版本控制系统,帮助开发团队维护代码作用:记录代码内容。切换代码版本,多人开发时高效合并代码内容如何学:个人本机使用:Git基础命令和概念多人共享使用:团队开发同一个项目的代码版本管理Git配置用户信息配置:用户名和邮箱,应用在每次提交代码版本时表明自己的身份命令:查看git版本号git-v配置用户名gitconfig--globaluser.name

- 2019-05-13

王健_100a

【撒下18:2】大卫打发军兵出战,分为三队:一队在约押手下,一队在洗鲁雅的儿子约押兄弟亚比筛手下,一队在迦特人以太手下。大卫对军兵说:“我必与你们一同出战。”解释:大卫检阅部队,将它分成三队,每队由一位元帅统领;约押与兄弟亚比筛,并迦特人以太共同指挥。大卫想与他们一同出战!应用:作为领袖与军兵一起出战是很重要。领袖在事奉中与信徒一起,领袖在任何的环境里与信徒一起走过。我们要同心协力为主而战。祷告:

- 摩托车加装车载手机充电usb方案/雅马哈USB充电方案开发

诚芯微科技

社交电子

长途骑行需要给手机与行车记录仪等设备供电,那么,加装USB充电器就相继在两轮电动车上应用起来了。摩托车加装usb充电方案主要应用于汽车、电动自行车、摩托车、房车、渡轮、游艇等交通工具。提供电动车USB充电器方案/摩托车加装usb充电方案/渡轮加装usb充电方案/游艇加装usb充电方案开发。摩托车加装车载手机充电usb方案、汽车游艇改装四孔面板装双USB车充点烟器5V/4A电动车USB充电器输入4.

- nosql数据库技术与应用知识点

皆过客,揽星河

NoSQLnosql数据库大数据数据分析数据结构非关系型数据库

Nosql知识回顾大数据处理流程数据采集(flume、爬虫、传感器)数据存储(本门课程NoSQL所处的阶段)Hdfs、MongoDB、HBase等数据清洗(入仓)Hive等数据处理、分析(Spark、Flink等)数据可视化数据挖掘、机器学习应用(Python、SparkMLlib等)大数据时代存储的挑战(三高)高并发(同一时间很多人访问)高扩展(要求随时根据需求扩展存储)高效率(要求读写速度快)

- 广州会刊小程序开发公司哪家好|开发多少钱费用|专业外包服务

红匣子实力推荐

在选择广州会刊小程序开发公司时,有几个关键因素需要考虑。首先,您应该确定自己的需求和目标,以便找到最合适的开发公司。其次,您需要考虑公司的经验和专业知识。最后,您还应该考虑公司的信誉和口碑。开发-联系电话:13642679953(微信同号)首先,您应该明确自己的需求和目标。会刊小程序是一种用于展示会议信息和日程安排的应用程序。在选择开发公司之前,您应该明确自己的需求,包括功能要求、设计风格和用户体

- 简介Shell、zsh、bash

zhaosuningsn

Shellzshbashshelllinuxbash

Shell是Linux和Unix的外壳,类似衣服,负责外界与Linux和Unix内核的交互联系。例如接收终端用户及各种应用程序的命令,把接收的命令翻译成内核能理解的语言,传递给内核,并把内核处理接收的命令的结果返回给外界,即Shell是外界和内核沟通的桥梁或大门。Linux和Unix提供了多种Shell,其中有种bash,当然还有其他好多种。Mac电脑中不但有bash,还有一个zsh,预装的,据说

- 《Python数据分析实战终极指南》

xjt921122

python数据分析开发语言

对于分析师来说,大家在学习Python数据分析的路上,多多少少都遇到过很多大坑**,有关于技能和思维的**:Excel已经没办法处理现有的数据量了,应该学Python吗?找了一大堆Python和Pandas的资料来学习,为什么自己动手就懵了?跟着比赛类公开数据分析案例练了很久,为什么当自己面对数据需求还是只会数据处理而没有分析思路?学了对比、细分、聚类分析,也会用PEST、波特五力这类分析法,为啥

- OPENAIGC开发者大赛企业组AI黑马奖 | AIGC数智传媒解决方案

RPA中国

人工智能AIGC传媒

在第二届拯救者杯OPENAIGC开发者大赛中,涌现出一批技术突出、创意卓越的作品。为了让这些优秀项目被更多人看到,我们特意开设了优秀作品报道专栏,旨在展示其独特之处和开发者的精彩故事。无论您是技术专家还是爱好者,希望能带给您不一样的知识和启发。让我们一起探索AIGC的无限可能,见证科技与创意的完美融合!创未来AI应用赛-企业组AI黑马奖作品名称:AIGC数智传媒解决方案参赛团队:深圳市三象智能技术

- ES聚合分析原理与代码实例讲解

光剑书架上的书

大厂Offer收割机面试题简历程序员读书硅基计算碳基计算认知计算生物计算深度学习神经网络大数据AIGCAGILLMJavaPython架构设计Agent程序员实现财富自由

ES聚合分析原理与代码实例讲解1.背景介绍1.1问题的由来在大规模数据分析场景中,特别是在使用Elasticsearch(ES)进行数据存储和检索时,聚合分析成为了一个至关重要的功能。聚合分析允许用户对数据集进行细分和分组,以便深入探索数据的结构和模式。这在诸如实时监控、日志分析、业务洞察等领域具有广泛的应用。1.2研究现状目前,ES聚合分析已经成为现代大数据平台的核心组件之一。它支持多种类型的聚

- Java开发中,spring mvc 的线程怎么调用?

小麦麦子

springmvc

今天逛知乎,看到最近很多人都在问spring mvc 的线程http://www.maiziedu.com/course/java/ 的启动问题,觉得挺有意思的,那哥们儿问的也听仔细,下面的回答也很详尽,分享出来,希望遇对遇到类似问题的Java开发程序猿有所帮助。

问题:

在用spring mvc架构的网站上,设一线程在虚拟机启动时运行,线程里有一全局

- maven依赖范围

bitcarter

maven

1.test 测试的时候才会依赖,编译和打包不依赖,如junit不被打包

2.compile 只有编译和打包时才会依赖

3.provided 编译和测试的时候依赖,打包不依赖,如:tomcat的一些公用jar包

4.runtime 运行时依赖,编译不依赖

5.默认compile

依赖范围compile是支持传递的,test不支持传递

1.传递的意思是项目A,引用

- Jaxb org.xml.sax.saxparseexception : premature end of file

darrenzhu

xmlprematureJAXB

如果在使用JAXB把xml文件unmarshal成vo(XSD自动生成的vo)时碰到如下错误:

org.xml.sax.saxparseexception : premature end of file

很有可能时你直接读取文件为inputstream,然后将inputstream作为构建unmarshal需要的source参数。InputSource inputSource = new In

- CSS Specificity

周凡杨

html权重Specificitycss

有时候对于页面元素设置了样式,可为什么页面的显示没有匹配上呢? because specificity

CSS 的选择符是有权重的,当不同的选择符的样式设置有冲突时,浏览器会采用权重高的选择符设置的样式。

规则:

HTML标签的权重是1

Class 的权重是10

Id 的权重是100

- java与servlet

g21121

servlet

servlet 搞java web开发的人一定不会陌生,而且大家还会时常用到它。

下面是java官方网站上对servlet的介绍: java官网对于servlet的解释 写道

Java Servlet Technology Overview Servlets are the Java platform technology of choice for extending and enha

- eclipse中安装maven插件

510888780

eclipsemaven

1.首先去官网下载 Maven:

http://www.apache.org/dyn/closer.cgi/maven/binaries/apache-maven-3.2.3-bin.tar.gz

下载完成之后将其解压,

我将解压后的文件夹:apache-maven-3.2.3,

并将它放在 D:\tools目录下,

即 maven 最终的路径是:D:\tools\apache-mave

- jpa@OneToOne关联关系

布衣凌宇

jpa

Nruser里的pruserid关联到Pruser的主键id,实现对一个表的增删改,另一个表的数据随之增删改。

Nruser实体类

//*****************************************************************

@Entity

@Table(name="nruser")

@DynamicInsert @Dynam

- 我的spring学习笔记11-Spring中关于声明式事务的配置

aijuans

spring事务配置

这两天学到事务管理这一块,结合到之前的terasoluna框架,觉得书本上讲的还是简单阿。我就把我从书本上学到的再结合实际的项目以及网上看到的一些内容,对声明式事务管理做个整理吧。我看得Spring in Action第二版中只提到了用TransactionProxyFactoryBean和<tx:advice/>,定义注释驱动这三种,我承认后两种的内容很好,很强大。但是实际的项目当中

- java 动态代理简单实现

antlove

javahandlerproxydynamicservice

dynamicproxy.service.HelloService

package dynamicproxy.service;

public interface HelloService {

public void sayHello();

}

dynamicproxy.service.impl.HelloServiceImpl

package dynamicp

- JDBC连接数据库

百合不是茶

JDBC编程JAVA操作oracle数据库

如果我们要想连接oracle公司的数据库,就要首先下载oralce公司的驱动程序,将这个驱动程序的jar包导入到我们工程中;

JDBC链接数据库的代码和固定写法;

1,加载oracle数据库的驱动;

&nb

- 单例模式中的多线程分析

bijian1013

javathread多线程java多线程

谈到单例模式,我们立马会想到饿汉式和懒汉式加载,所谓饿汉式就是在创建类时就创建好了实例,懒汉式在获取实例时才去创建实例,即延迟加载。

饿汉式:

package com.bijian.study;

public class Singleton {

private Singleton() {

}

// 注意这是private 只供内部调用

private static

- javascript读取和修改原型特别需要注意原型的读写不具有对等性

bijian1013

JavaScriptprototype

对于从原型对象继承而来的成员,其读和写具有内在的不对等性。比如有一个对象A,假设它的原型对象是B,B的原型对象是null。如果我们需要读取A对象的name属性值,那么JS会优先在A中查找,如果找到了name属性那么就返回;如果A中没有name属性,那么就到原型B中查找name,如果找到了就返回;如果原型B中也没有

- 【持久化框架MyBatis3六】MyBatis3集成第三方DataSource

bit1129

dataSource

MyBatis内置了数据源的支持,如:

<environments default="development">

<environment id="development">

<transactionManager type="JDBC" />

<data

- 我程序中用到的urldecode和base64decode,MD5

bitcarter

cMD5base64decodeurldecode

这里是base64decode和urldecode,Md5在附件中。因为我是在后台所以需要解码:

string Base64Decode(const char* Data,int DataByte,int& OutByte)

{

//解码表

const char DecodeTable[] =

{

0, 0, 0, 0, 0, 0

- 腾讯资深运维专家周小军:QQ与微信架构的惊天秘密

ronin47

社交领域一直是互联网创业的大热门,从PC到移动端,从OICQ、MSN到QQ。到了移动互联网时代,社交领域应用开始彻底爆发,直奔黄金期。腾讯在过去几年里,社交平台更是火到爆,QQ和微信坐拥几亿的粉丝,QQ空间和朋友圈各种刷屏,写心得,晒照片,秀视频,那么谁来为企鹅保驾护航呢?支撑QQ和微信海量数据背后的架构又有哪些惊天内幕呢?本期大讲堂的内容来自今年2月份ChinaUnix对腾讯社交网络运营服务中心

- java-69-旋转数组的最小元素。把一个数组最开始的若干个元素搬到数组的末尾,我们称之为数组的旋转。输入一个排好序的数组的一个旋转,输出旋转数组的最小元素

bylijinnan

java

public class MinOfShiftedArray {

/**

* Q69 旋转数组的最小元素

* 把一个数组最开始的若干个元素搬到数组的末尾,我们称之为数组的旋转。输入一个排好序的数组的一个旋转,输出旋转数组的最小元素。

* 例如数组{3, 4, 5, 1, 2}为{1, 2, 3, 4, 5}的一个旋转,该数组的最小值为1。

*/

publ

- 看博客,应该是有方向的

Cb123456

反省看博客

看博客,应该是有方向的:

我现在就复习以前的,在补补以前不会的,现在还不会的,同时完善完善项目,也看看别人的博客.

我刚突然想到的:

1.应该看计算机组成原理,数据结构,一些算法,还有关于android,java的。

2.对于我,也快大四了,看一些职业规划的,以及一些学习的经验,看看别人的工作总结的.

为什么要写

- [开源与商业]做开源项目的人生活上一定要朴素,尽量减少对官方和商业体系的依赖

comsci

开源项目

为什么这样说呢? 因为科学和技术的发展有时候需要一个平缓和长期的积累过程,但是行政和商业体系本身充满各种不稳定性和不确定性,如果你希望长期从事某个科研项目,但是却又必须依赖于某种行政和商业体系,那其中的过程必定充满各种风险。。。

所以,为避免这种不确定性风险,我

- 一个 sql优化 ([精华] 一个查询优化的分析调整全过程!很值得一看 )

cwqcwqmax9

sql

见 http://www.itpub.net/forum.php?mod=viewthread&tid=239011

Web翻页优化实例

提交时间: 2004-6-18 15:37:49 回复 发消息

环境:

Linux ve

- Hibernat and Ibatis

dashuaifu

Hibernateibatis

Hibernate VS iBATIS 简介 Hibernate 是当前最流行的O/R mapping框架,当前版本是3.05。它出身于sf.net,现在已经成为Jboss的一部分了 iBATIS 是另外一种优秀的O/R mapping框架,当前版本是2.0。目前属于apache的一个子项目了。 相对Hibernate“O/R”而言,iBATIS 是一种“Sql Mappi

- 备份MYSQL脚本

dcj3sjt126com

mysql

#!/bin/sh

# this shell to backup mysql

#

[email protected] (QQ:1413161683 DuChengJiu)

_dbDir=/var/lib/mysql/

_today=`date +%w`

_bakDir=/usr/backup/$_today

[ ! -d $_bakDir ] && mkdir -p

- iOS第三方开源库的吐槽和备忘

dcj3sjt126com

ios

转自

ibireme的博客 做iOS开发总会接触到一些第三方库,这里整理一下,做一些吐槽。 目前比较活跃的社区仍旧是Github,除此以外也有一些不错的库散落在Google Code、SourceForge等地方。由于Github社区太过主流,这里主要介绍一下Github里面流行的iOS库。 首先整理了一份

Github上排名靠

- html wlwmanifest.xml

eoems

htmlxml

所谓优化wp_head()就是把从wp_head中移除不需要元素,同时也可以加快速度。

步骤:

加入到function.php

remove_action('wp_head', 'wp_generator');

//wp-generator移除wordpress的版本号,本身blog的版本号没什么意义,但是如果让恶意玩家看到,可能会用官网公布的漏洞攻击blog

remov

- 浅谈Java定时器发展

hacksin

java并发timer定时器

java在jdk1.3中推出了定时器类Timer,而后在jdk1.5后由Dou Lea从新开发出了支持多线程的ScheduleThreadPoolExecutor,从后者的表现来看,可以考虑完全替代Timer了。

Timer与ScheduleThreadPoolExecutor对比:

1.

Timer始于jdk1.3,其原理是利用一个TimerTask数组当作队列

- 移动端页面侧边导航滑入效果

ini

jqueryWebhtml5cssjavascirpt

效果体验:http://hovertree.com/texiao/mobile/2.htm可以使用移动设备浏览器查看效果。效果使用到jquery-2.1.4.min.js,该版本的jQuery库是用于支持HTML5的浏览器上,不再兼容IE8以前的浏览器,现在移动端浏览器一般都支持HTML5,所以使用该jQuery没问题。HTML文件代码:

<!DOCTYPE html>

<h

- AspectJ+Javasist记录日志

kane_xie

aspectjjavasist

在项目中碰到这样一个需求,对一个服务类的每一个方法,在方法开始和结束的时候分别记录一条日志,内容包括方法名,参数名+参数值以及方法执行的时间。

@Override

public String get(String key) {

// long start = System.currentTimeMillis();

// System.out.println("Be

- redis学习笔记

MJC410621

redisNoSQL

1)nosql数据库主要由以下特点:非关系型的、分布式的、开源的、水平可扩展的。

1,处理超大量的数据

2,运行在便宜的PC服务器集群上,

3,击碎了性能瓶颈。

1)对数据高并发读写。

2)对海量数据的高效率存储和访问。

3)对数据的高扩展性和高可用性。

redis支持的类型:

Sring 类型

set name lijie

get name lijie

set na

- 使用redis实现分布式锁

qifeifei

在多节点的系统中,如何实现分布式锁机制,其中用redis来实现是很好的方法之一,我们先来看一下jedis包中,有个类名BinaryJedis,它有个方法如下:

public Long setnx(final byte[] key, final byte[] value) {

checkIsInMulti();

client.setnx(key, value);

ret

- BI并非万能,中层业务管理报表要另辟蹊径

张老师的菜

大数据BI商业智能信息化

BI是商业智能的缩写,是可以帮助企业做出明智的业务经营决策的工具,其数据来源于各个业务系统,如ERP、CRM、SCM、进销存、HER、OA等。

BI系统不同于传统的管理信息系统,他号称是一个整体应用的解决方案,是融入管理思想的强大系统:有着系统整体的设计思想,支持对所有

- 安装rvm后出现rvm not a function 或者ruby -v后提示没安装ruby的问题

wudixiaotie

function

1.在~/.bashrc最后加入

[[ -s "$HOME/.rvm/scripts/rvm" ]] && source "$HOME/.rvm/scripts/rvm"

2.重新启动terminal输入:

rvm use ruby-2.2.1 --default

把当前安装的ruby版本设为默

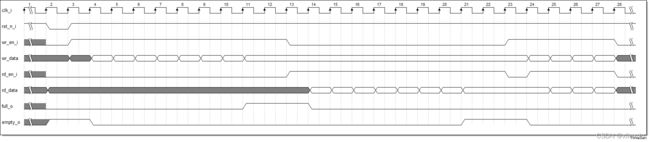

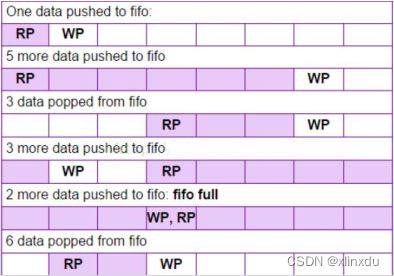

模块主要分为读/写接口、读/写指针、读写指针的比较逻辑和array存储阵列四部分。

模块主要分为读/写接口、读/写指针、读写指针的比较逻辑和array存储阵列四部分。

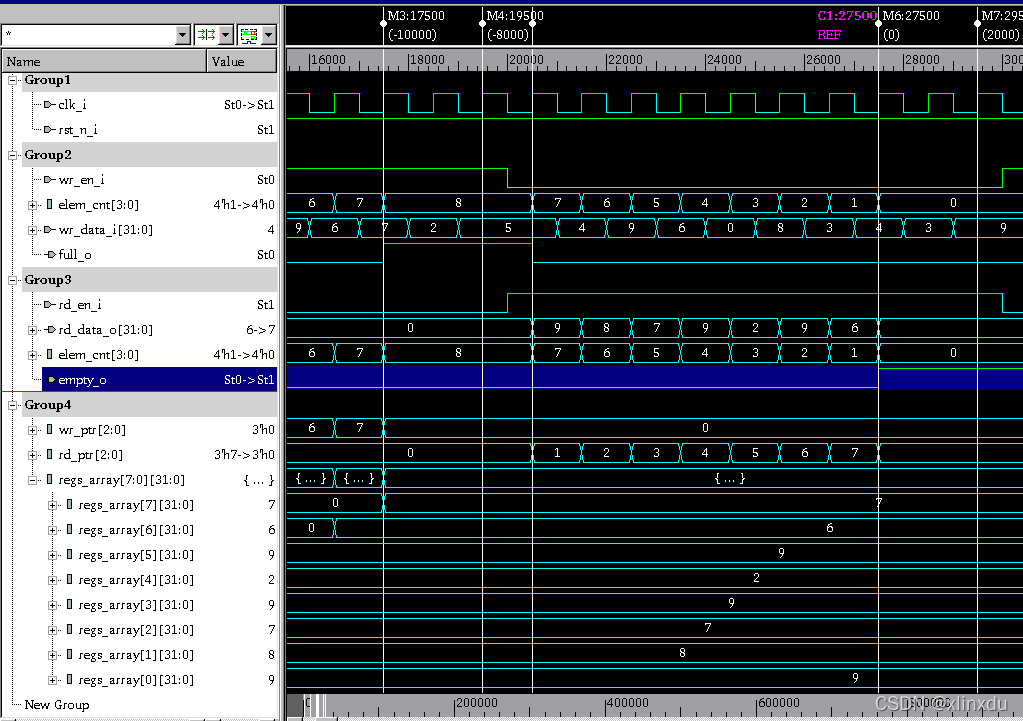

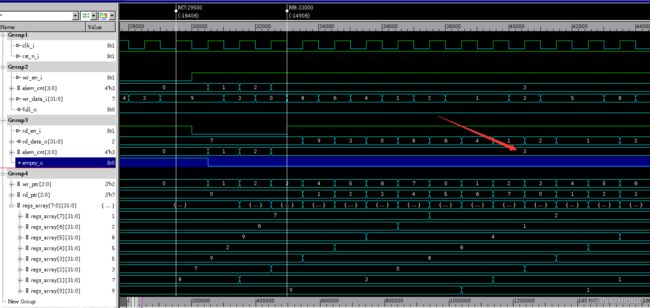

先进行写操作,写入三个新数据之后,同时进行读写操作,期间写入新数据和读出数据,但是elem_cnt计数器不再变化,动态平衡。

先进行写操作,写入三个新数据之后,同时进行读写操作,期间写入新数据和读出数据,但是elem_cnt计数器不再变化,动态平衡。