Quartus II实验一 运算部件实验:加法器

可以参考以下链接并结合我的文章步骤学习(我的详细点哈哈~)

零、Quartus II基本使用(计组实验)![]() https://blog.csdn.net/qq_40925617/article/details/121171310?spm=1001.2014.3001.5502

https://blog.csdn.net/qq_40925617/article/details/121171310?spm=1001.2014.3001.5502

一、建立一个工程,设计全加器,并加以仿真

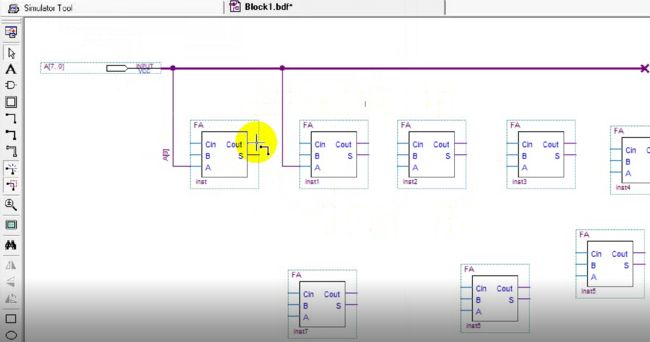

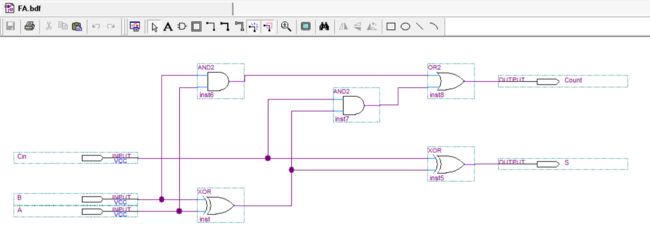

图形设计电路图:全加器

能对两个1 位二进制数相加并考虑低位来的进位(即相当于3 个1 位二进制数的相加)得到“和”及“进位”的逻辑电路,称之为全加器,其中A和B分别为两个1 位二进制数的输入;Cin 为低位来的进位输入;S 和Cout 分别为相加后形成的“和”及向高位的“进位”输出。

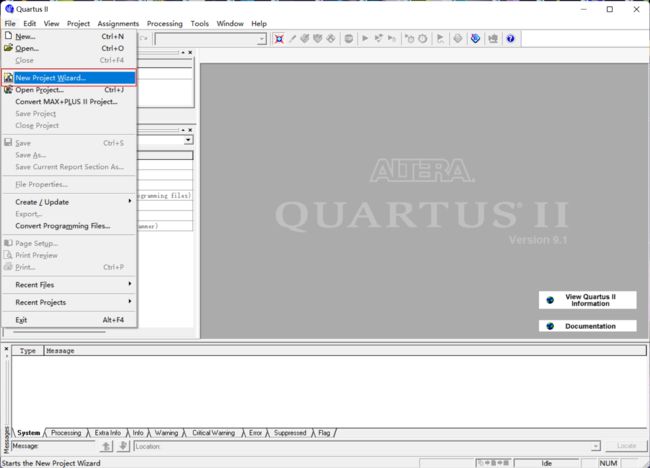

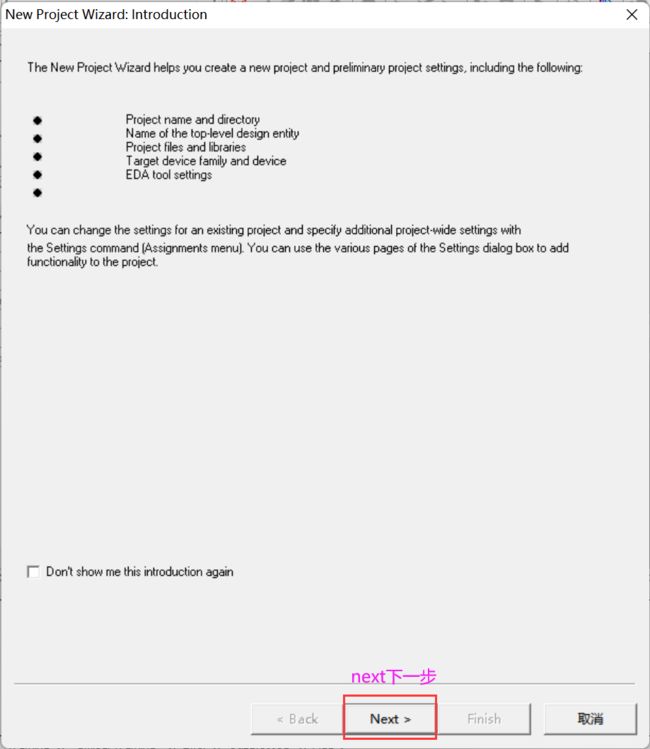

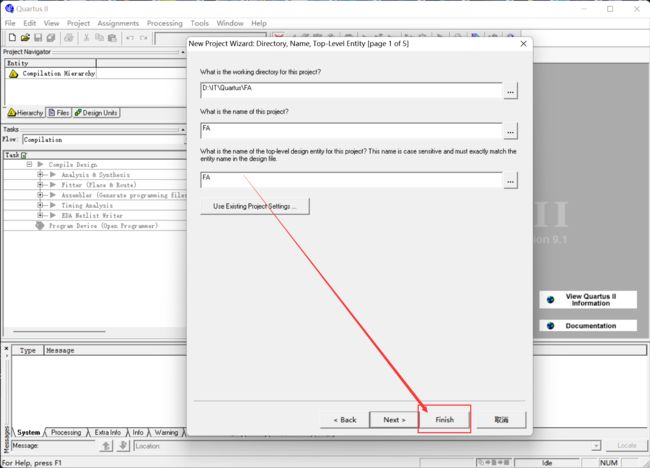

1.新建工程FA

2. 保存位置 D:\IT\Quartus\FA

工程名称 FA

主文件(top-level design entity)FA

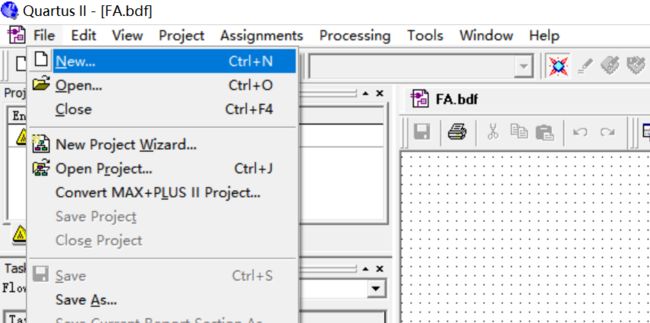

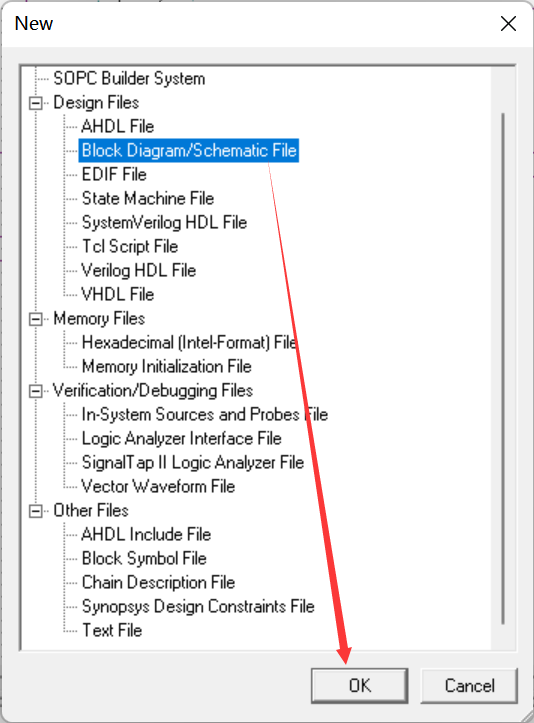

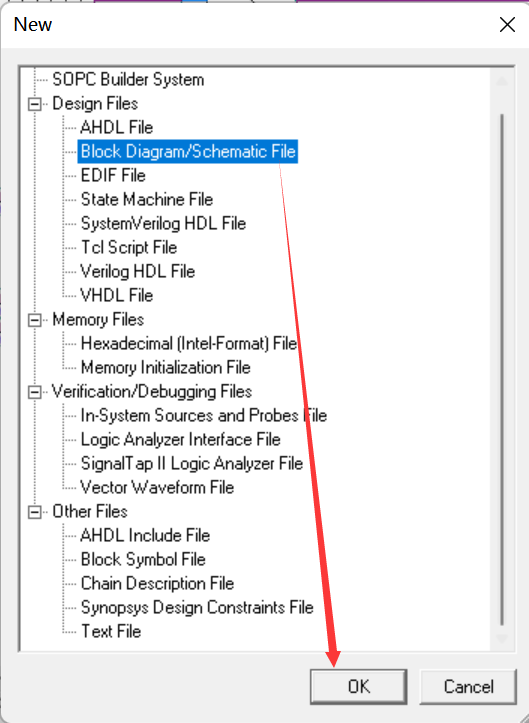

3. 新建——Block Diagram,保存为FA

设计原理图文件保存为FA.BDF

4. 设计原理图文件保存为FA.BDF

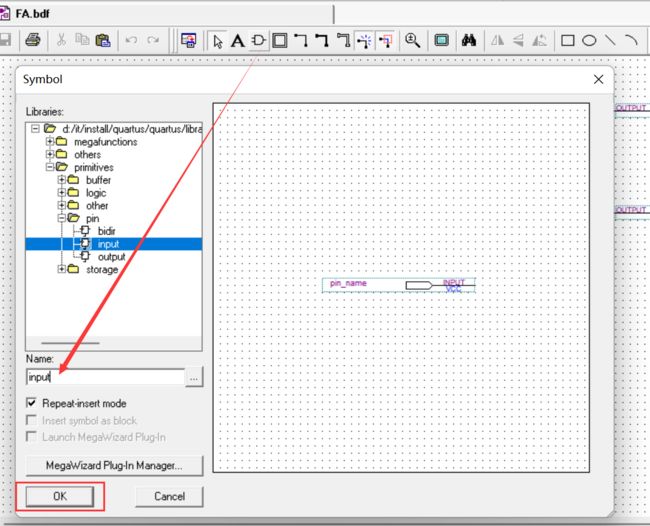

(1)添加元件:

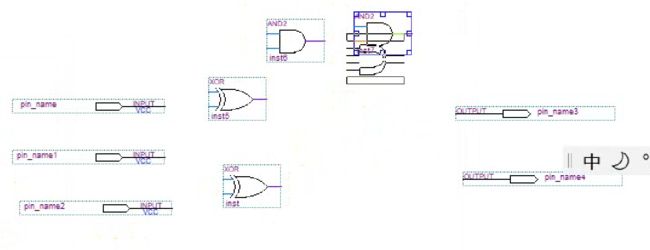

输入信号 : input 、输出信号 : output 、2与门 : and2 、2或门 : or2 、异或门 : xor

修改输入信号依次位A、B、Cin 输出信号依次为 S、Cout

(2)连接元件: 不用点线,鼠标放在线头上直接拖拽即可

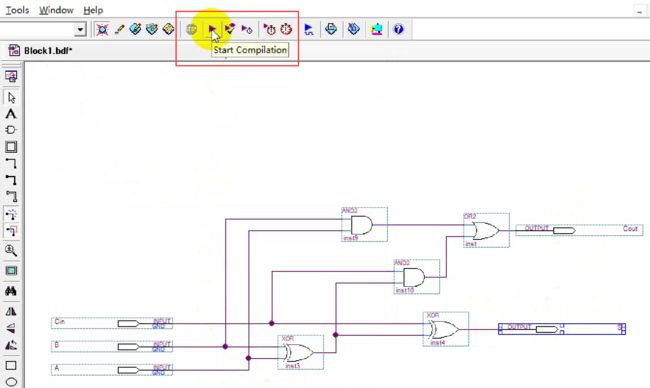

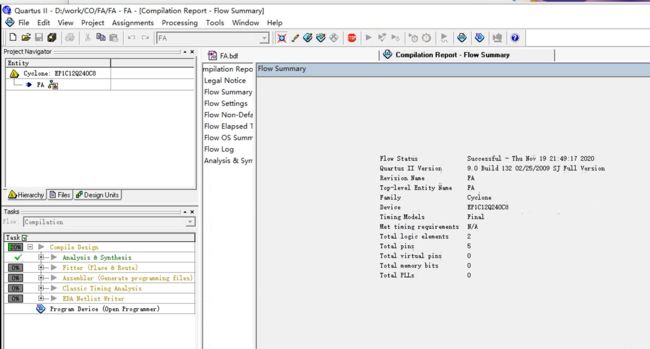

5. 编译:点击 Start Ccompilation

5. 编译:点击 Start Ccompilation

注意:提示编译成功接口,如果编译出错,可能是你图画的不对,很大原因在于你连接的线有问题,绕,打结了!

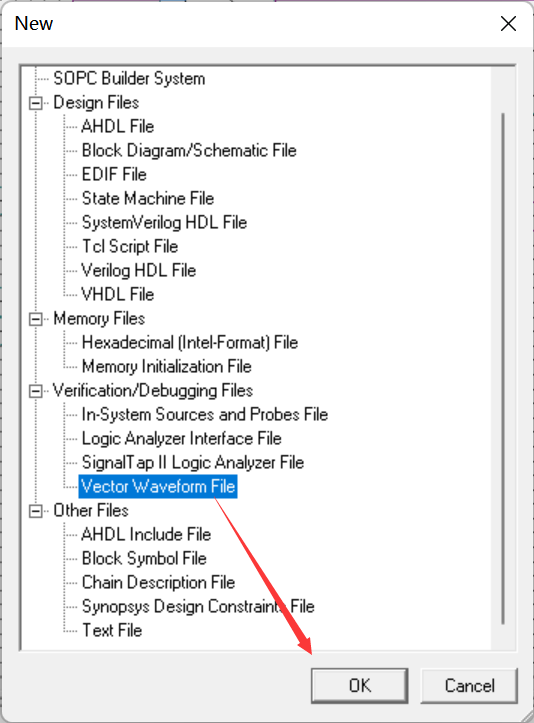

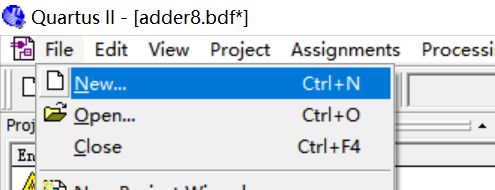

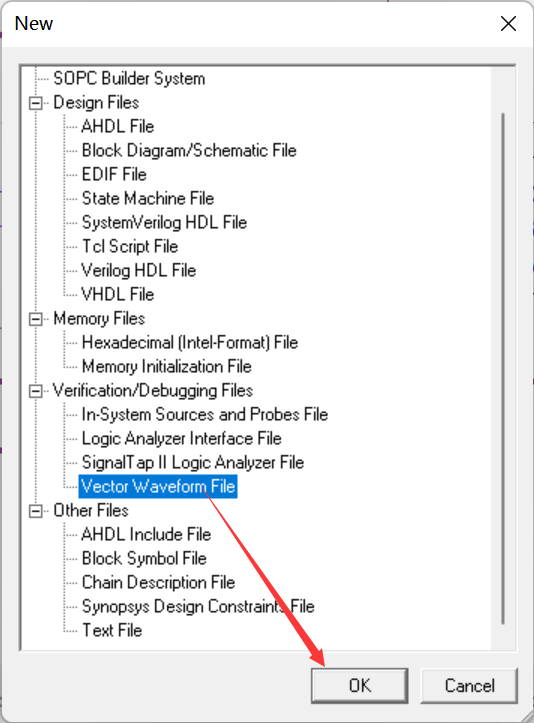

6. 设计仿真波形文件

新建——Vector Waveform File

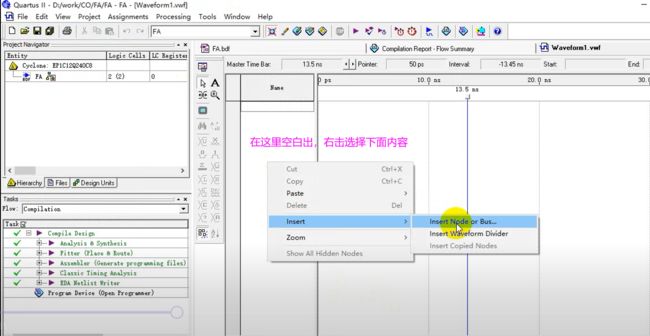

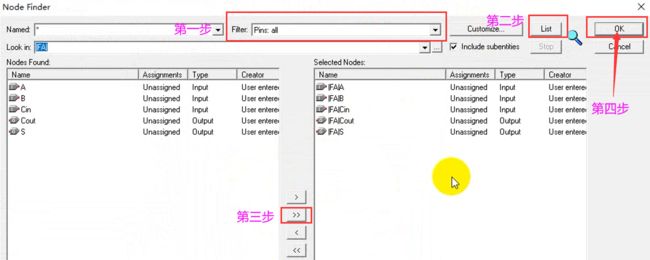

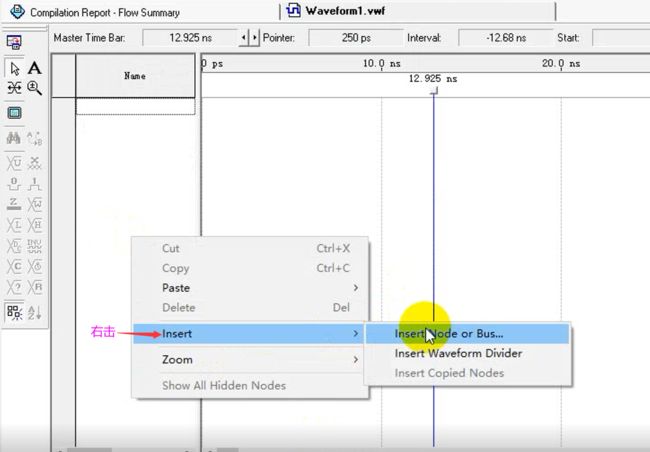

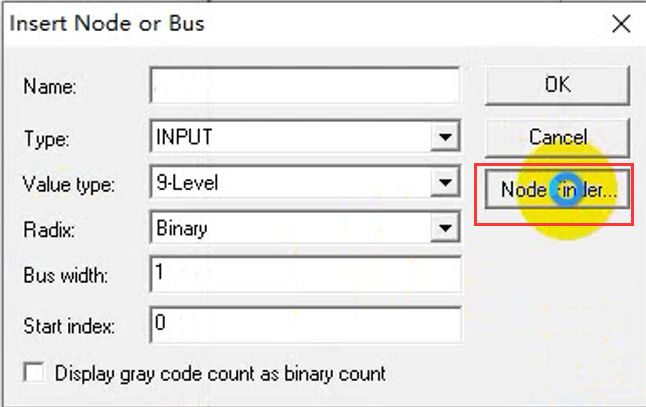

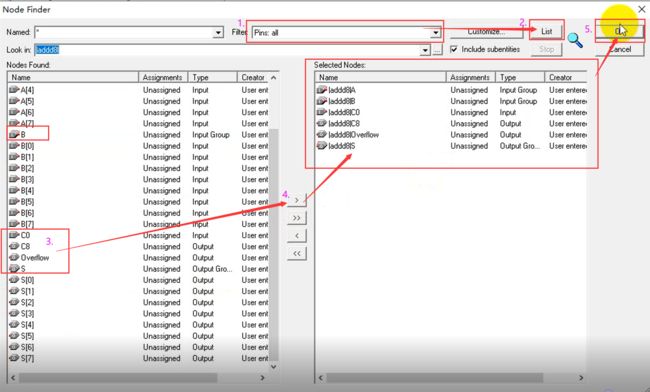

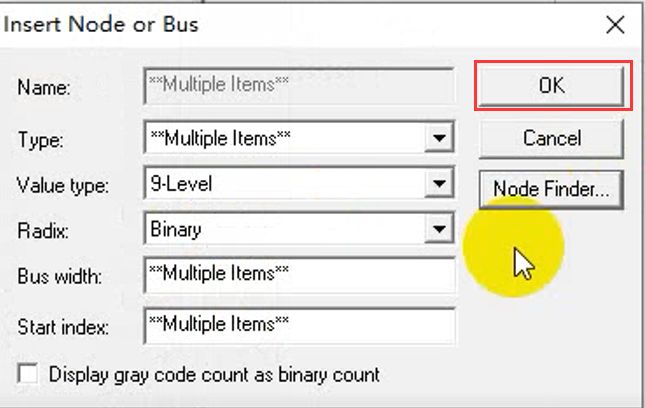

7. 插入仿真的信号(快捷菜单——inert node or bus——node finder)

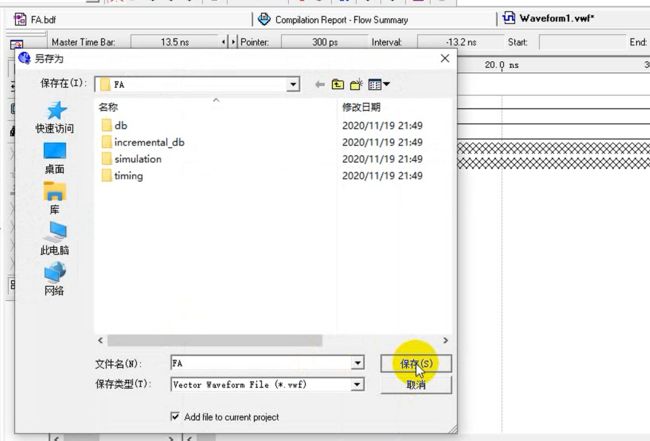

8. Ctrl+S保存,命名FA

一定要命名一样的,不要问为什么,你不听,编译错自找麻烦!

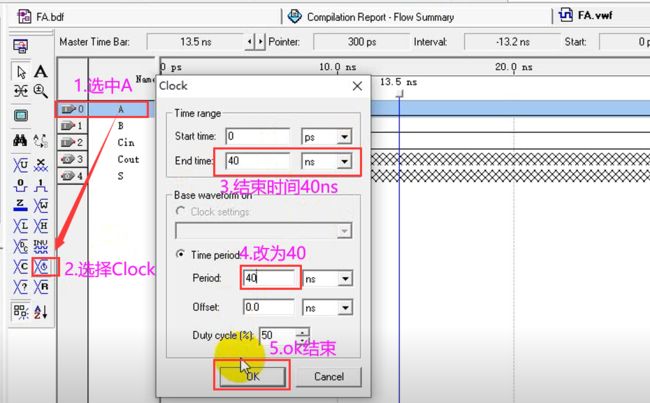

9. 设置A 为40ns的clock信号,end time 为40ns

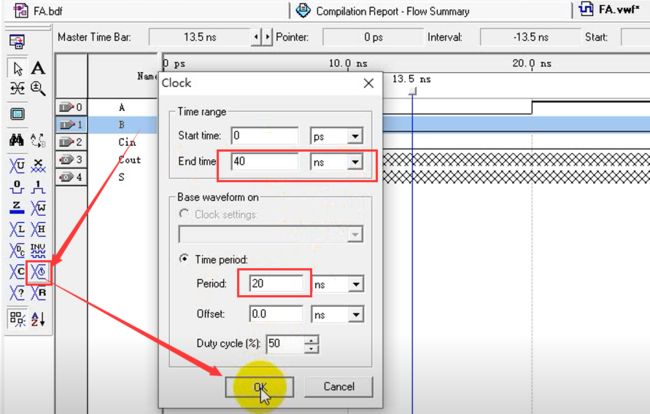

设置B 为20ns的clock信号,end time 为40ns

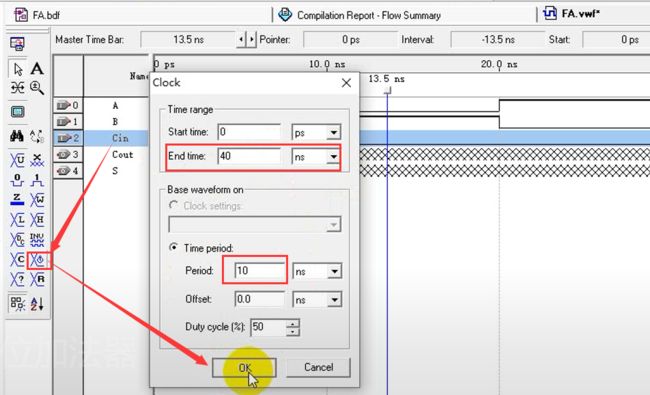

设置Cin 为10ns的clock信号,end time 为40ns

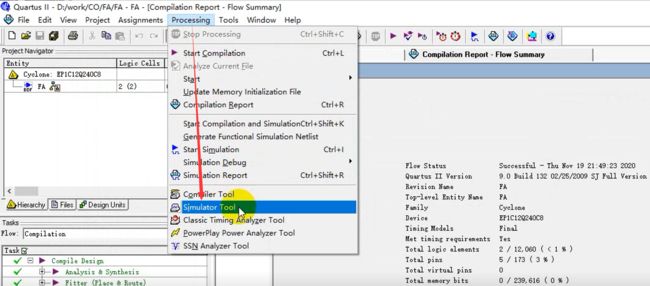

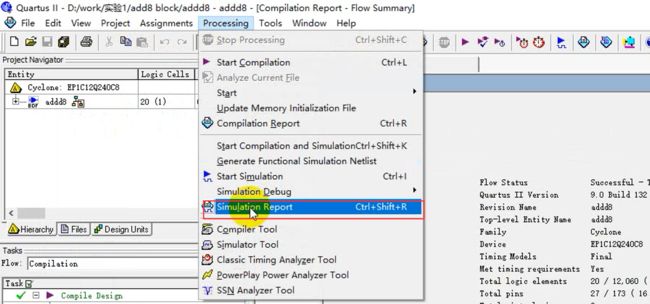

10. Processing ——simulation tools 仿真

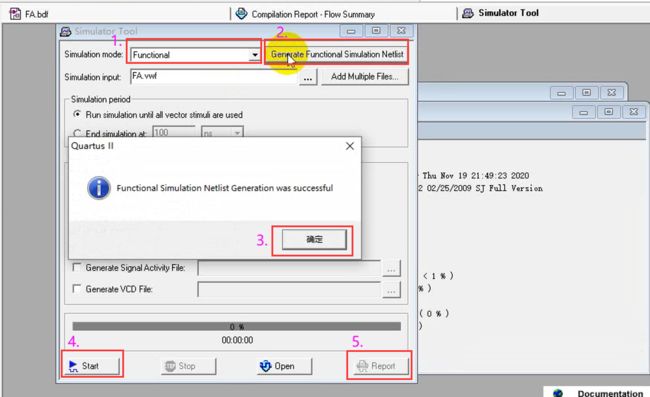

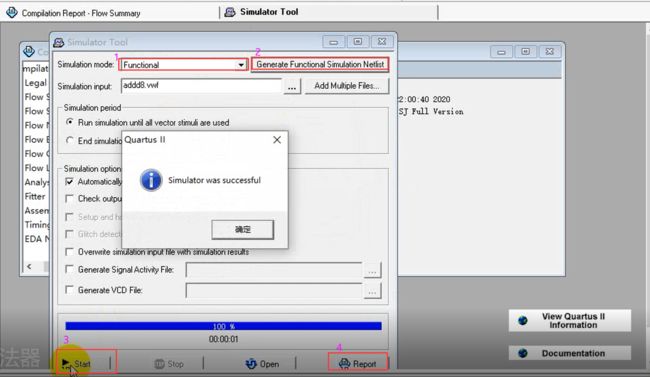

11. 选择——functional 进行功能仿真(生成功能仿真的网表文件)

Start——开始仿真

Report——查看仿真结果

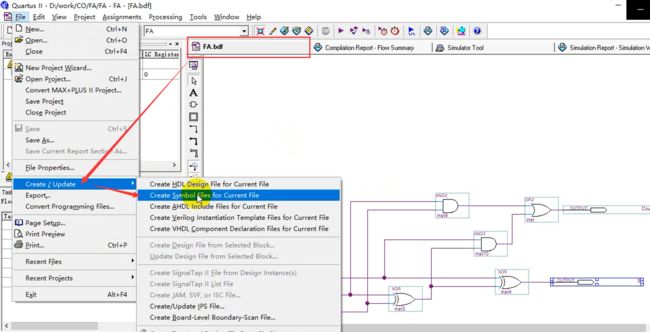

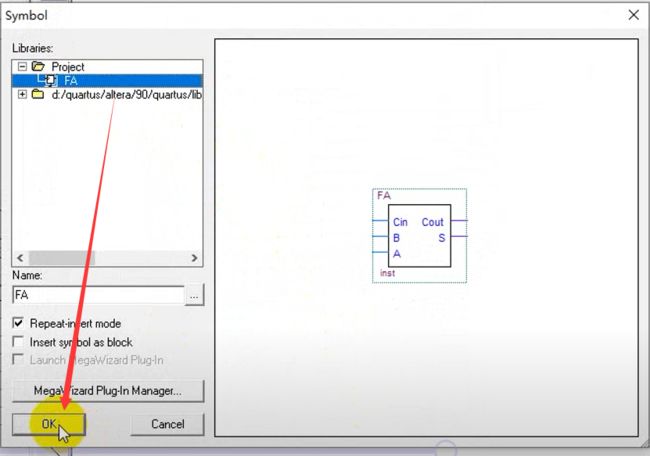

12. 用原理图文件FA.bdf,创建symbol文件FA.bsf

文件——Create/Update——Create Symbol File for Current File

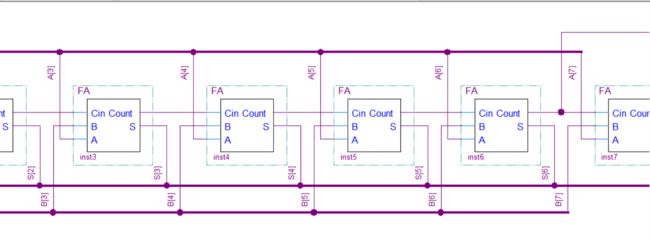

二、 建立一个工程,设计8位行波进位加法器,并加以仿真

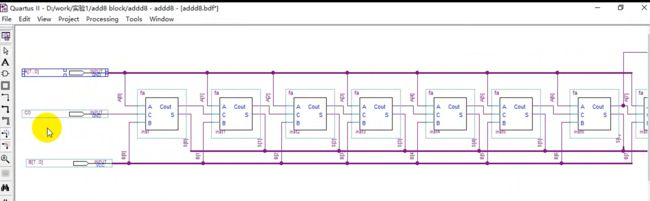

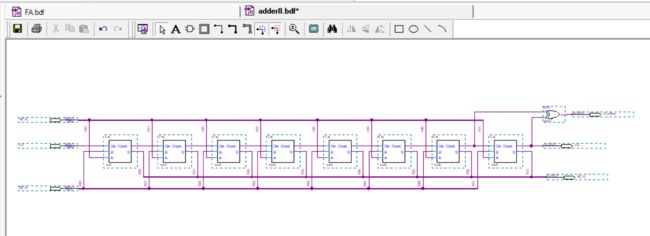

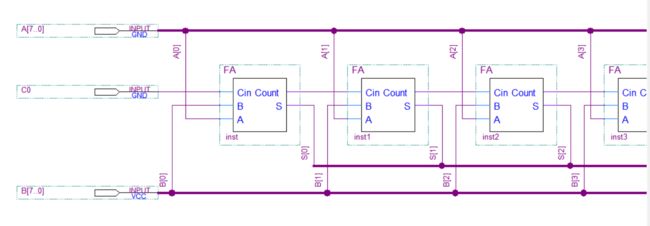

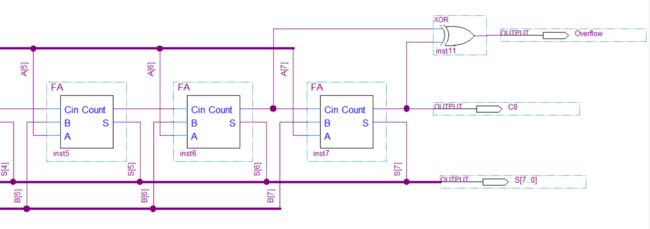

图形设计电路图:8位行波进位加法器

行波进位加法器是把n位全加器串联起来,低位全加器的进位输出连到相邻的高位全加器的进位输入,各位相加是并行的,但其进位信号是由低位向高位逐级传递的,好像行波一样,高位的和要等低位的进位形成后才能确定,最后最高位的进位和符号位的进位进行异或运算,可以得到是否溢出的信息。

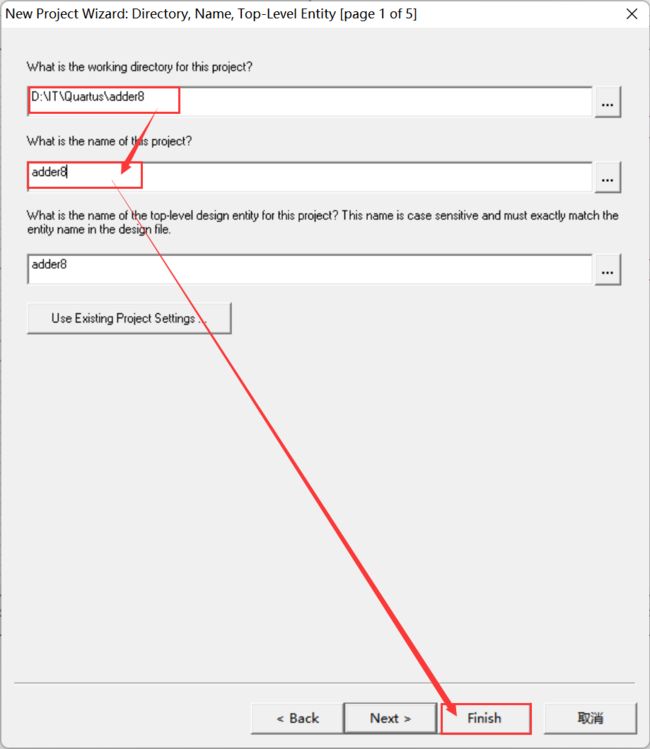

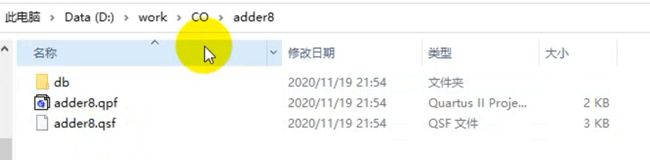

1. 新建工程 adder8

保存位置 D:\IT\Quartus\adder8

工程名称 adder8

主文件(top-level design entity)adder8

2. 将FA工程复制到adder8目录下

3. 新建——Block Diagram,保存为 adder8

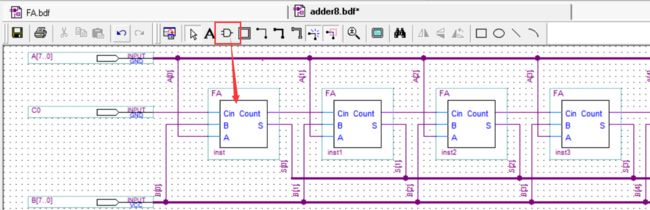

4. 添加元件 FA

输入信号、输出信号、FA、异或门xor

修改输入信号分别为A[7..0]、B[7..0]、C0

修改输出信号分别为S[7..0]、C8、Overflow

连接元件:

连接时为了指定连接的总线中的哪一个信号,需设置连线对应某信号,如:A[0]

老师的参考图

自己绘制的参考图

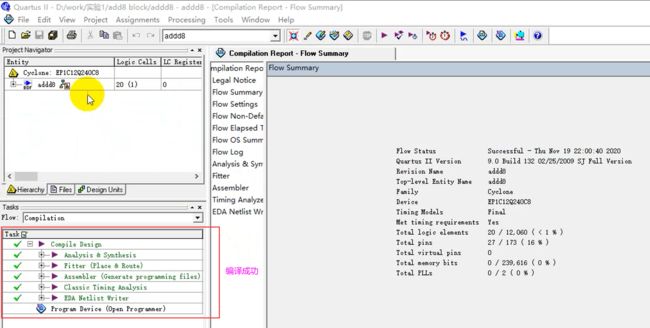

5. 编译

5. 编译

6. 设计仿真波形文件

新建——Vector Waveform File

7. 插入仿真的信号(快捷菜单——inert node or bus——node finder)

A、B、C0、 S、C8、Overflow

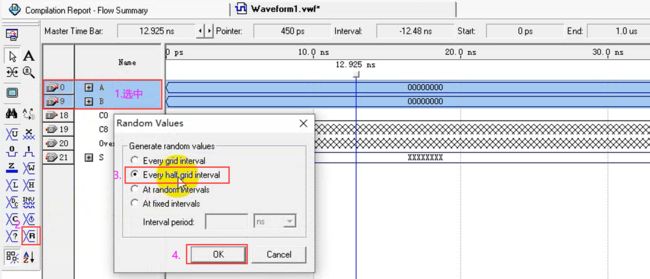

8. 设置C0为0,A、B均为半个时钟变化一次的随机值

(随机值需要包含 可能出现的各种情况,如果不合适可以手动修改某个值)

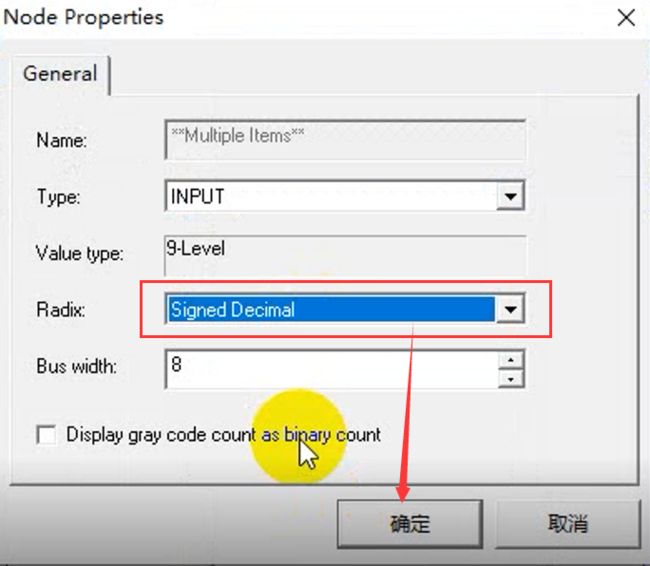

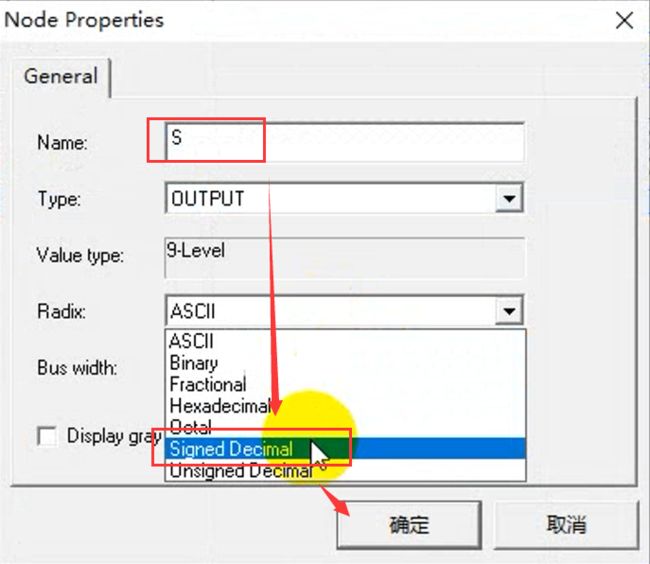

A、B、S均显示为Signed Decimal(有符号数)

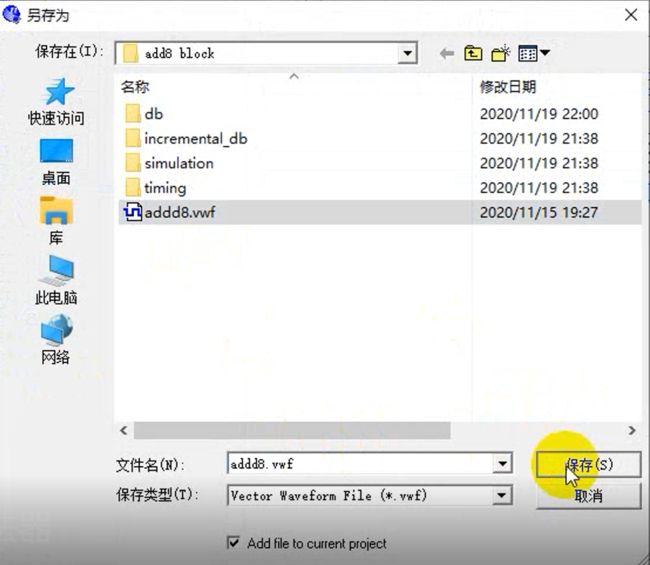

9. 保存文件——保存为adder8.vwf

10. Processing ——simulation tools 仿真

选择——functional 进行功能仿真,(生成功能仿真的网表文件)

Start——开始仿真

Report——查看仿真结果

11. 进行分析

以上就是关于实验的操作步骤,早一点自学,别等到上课再听老师讲,效率太低了,鉴于网上没有人写关于这部分操作,我就辛苦点为大家服务了!