数字逻辑---头歌实训作业---加法器设计(Logisim)

第1关:半加器设计

如有任何不解或者想要答案代码,可在评论区喊话我哦,希望我的答案对你有帮助,点个关注再走吧,感谢!!!

本关卡最终答案:

任务描述

本关任务:利用在Logisim中的“组合逻辑分析”工具自动生成半加器电路。

相关知识

半加器电路是指对两个输入的二进制数据位A、B相加(没有进位输入),输出和Sum与进位Cout,是实现两个一位二进制数的加法运算电路。真值表如下:

A |

B |

Cout |

Sum |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 0 |

测试说明

请用记事本或者其他纯文本编辑器打开电路文件(Adder.circ),全选、复制,然后粘贴到代码窗口中,点击右下方的“评测”按钮,平台会对你的代码进行测试。

第2关:全加器设计

如有任何不解或者想要答案代码,可在评论区喊话我哦,希望我的答案对你有帮助,点个关注再走吧,感谢!!!

本关卡最终答案:

任务描述

本关任务:请根据教材中的全加器原理图在Logisim中手工绘制全加器电路。

相关知识

全加器FA(Full Adder)是实现两个1位二进制数(xi、yi)和来自低位进位(ci)相加,产生和(si)与进位输出(ci+1)的组合逻辑电路。真值表如下:

xi |

yi |

ci |

ci+1 |

si |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 | 1 |

| 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 1 | 1 |

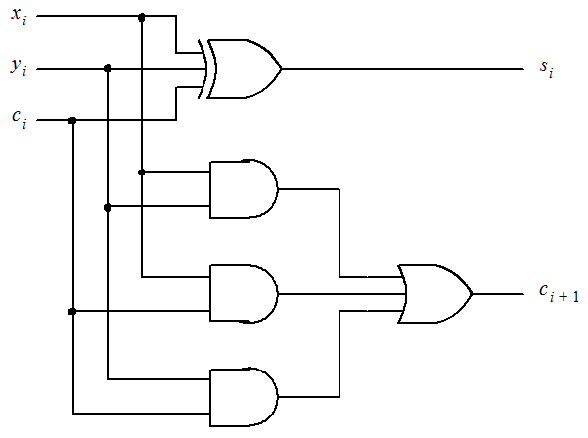

全加器的逻辑表达式如下: s=∑m(1,2,4,7)=xi⊕yi⊕ci ci+1=∑m(3,5,6,7)=xiyi+xici+yici=xiyi+(xi⊕yi)ci 电路原理图如下:

实验内容

实验电路框架与第一关相同。 在Logisim中打开实验电路框架,在工程中的“手绘全加器”子电路中绘制全加器电路。

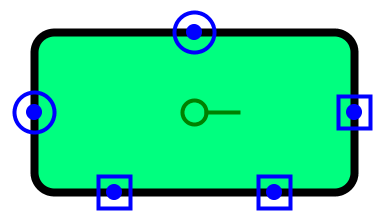

子电路封装外观

子电路封装外观如下图所示,请不要改变引脚位置,否则无法完成测试!

测试说明

请用记事本或者其他纯文本编辑器打开电路文件(Adder.circ),全选、复制,然后粘贴到代码窗口中,点击右下方的“评测”按钮,平台会对你的代码进行测试。

常见问题

不要使用“组合逻辑分析”工具自动生成电路,否则电路封装外观会改变,无法完成在线评测!

第3关:行波进位加法器设计

如有任何不解或者想要答案代码,可在评论区喊话我哦,希望我的答案对你有帮助,点个关注再走吧,感谢!!!

本关卡最终答案:

任务描述

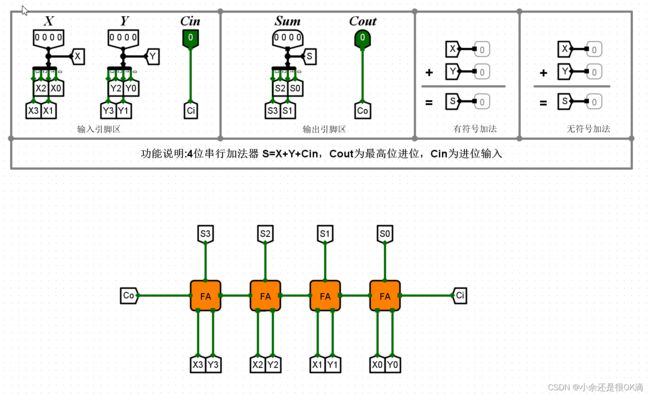

本关任务:在Logisim中,利用上一关设计的全加器FA级联设计一个4位的行波进位加法器。

相关知识

行波进位是指进位信号从低位逐位向高位传递,特点是结构简单,但速度比较慢。原理示意图如下:

子电路封装外观

请勿移动引脚位置,否则无法完成测试!

实验内容

实验电路框架与第一关相同。 在Logisim中打开实验电路框架,在工程中的“4位行波进位加法器”子电路中,利用全加器模块级联设计一个4位的加法器。

测试说明

请用记事本或者其他纯文本编辑器打开电路文件(Adder.circ),全选、复制,然后粘贴到代码窗口中,点击右下方的“评测”按钮,平台会对你的代码进行测试。

第4关:1位十进制加法器设计

如有任何不解或者想要答案代码,可在评论区喊话我哦,希望我的答案对你有帮助,点个关注再走吧,感谢!!!

本关卡最终答案:

任务描述

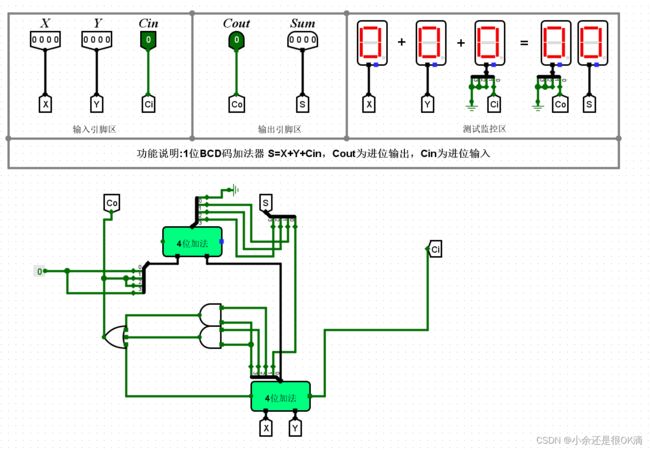

本关任务:在Logisim中,利用上一关的4位加法器来设计一个1位十进制数(8421BCD)加法器电路。

相关知识

BCD码加法原理

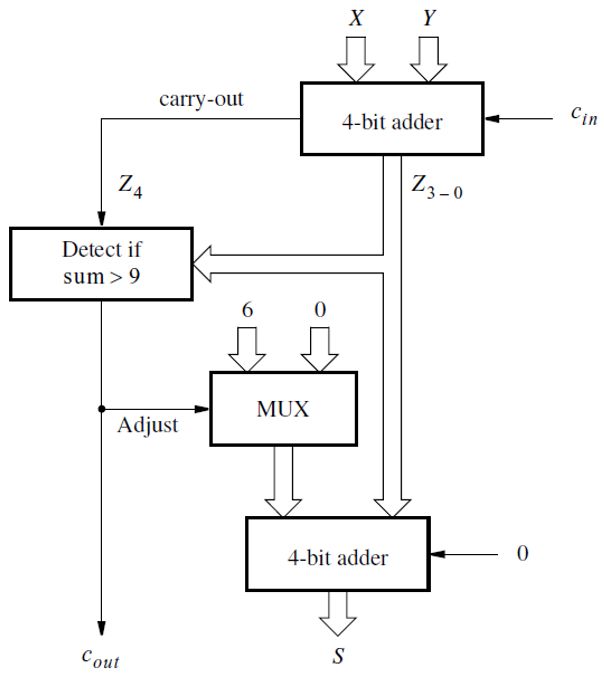

1位十进制数(8421BCD码)加法原理图如下:

修正逻辑设计

第一次相加的结果Z大于9的判断: 简化真值表如下:

表达式:Adjust=Z4+Z3Z2+Z3Z1

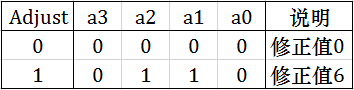

修正值0或6的生成逻辑

真值表如下:

表达式:a3=a0=0;a2=a1=Adjust

子电路封装外观

请勿移动引脚位置,否则无法完成电路测试!

实验内容

实验电路框架与第一关相同。 在Logisim中打开实验电路框架,在工程中的“1位十进制加法器”子电路中,利用4位加法器和适当的门电路来设计完成1位BCD码加法器电路。 本实验要用到线路库(Wiring)中的“分线器(Splitter)”! 本实验禁止使用比较器和多路选择器MUX!

拓展设计建议

完成上述实验后,可以在本地尝试多位十进制加法器设计、8421码到余3码的转换电路设计等。

测试说明

请用记事本或者其他纯文本编辑器打开电路文件(Adder.circ),全选、复制,然后粘贴到代码窗口中,点击右下方的“评测”按钮,平台会对你的代码进行测试。