【FPGA基础篇】底层结构组成

文章目录

- 前言

-

- CPU和DSP、FPGA、ASIC对比

- FPGA和CPLD比较

- FPGA基础

-

- IOB——输入输出单元

- CLB——可编程逻辑模块

-

- LUT——查找表

- MUX——选择器(复用器)

- Carry Chain——进位链

- Flip-Flop——触发器

- BRAM——块RAM

- DCM——数字时钟管理器

-

- 布线资源

- 内嵌的底层功能单元

- 内嵌专用硬件模块

- 可参考文献

前言

CPU和DSP、FPGA、ASIC对比

CPU和DSP:软件可编程、灵活性高、功耗高

FPGA:硬件可编程、灵活性高、功耗较低

ASIC:特定应用固化、不可编程,不灵活,功耗很低

灵活性与效率之间存在矛盾,因此出现了芯片融合的方案——即MPU+DSP+专用IP+PL(可编程逻辑)

FPGA和CPLD比较

相同点:

统称为PLD,都属于可编程逻辑器件

不同点:

CPLD以乘积项结构方式构成逻辑行为,触发器有限,乘积项丰富,适用于完成复杂的逻辑组合任务。

FPGA触发器丰富,适用于完成时序逻辑,多用于数字信号处理领域。

FPGA基础

目前主流的FPGA仍以查找表技术为基础,主要由六部分组成:可编程输入输出单元(IOB)、可编程逻辑单元(CLB)、完整的时钟管理(DCM)、嵌入块状RAM(BRAM)、布线资源、内嵌的底层功能单元(soft core,软核,区别于软IP核)和内嵌专用硬件模块(hard core,硬核,区别于硬IP核)。其中最为主要的是可编程输出输出单元、可编程逻辑单元和布线资源。

IP核一般分为软IP核,硬IP核和固IP核。和上述的软硬核并不是同一个定义范畴。

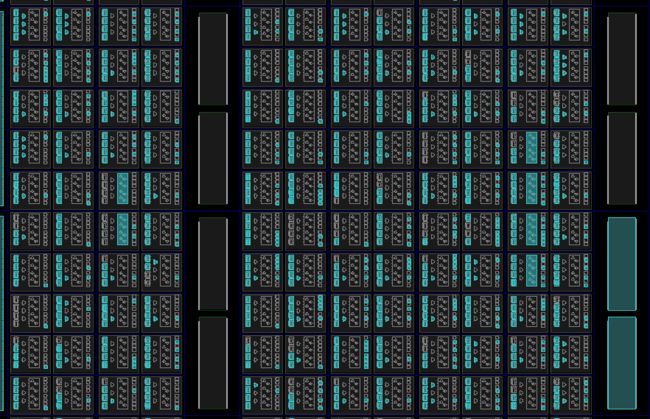

这些就是内部资源,主要是逻辑单元和块状RAM及一些内嵌功能单元。

再放大,这些逻辑单元的内部结构也出来了,像大型“停车场”,其中亮色的表示被占用的资源,亮色部分越多,表示资源利用率越高。

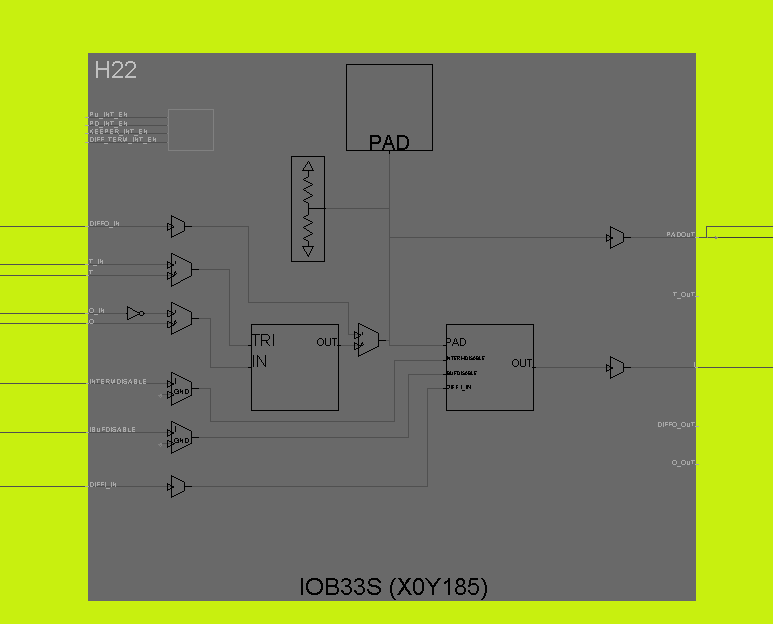

IOB——输入输出单元

FPGA内的I/O按组(bank)分类,每个组都能独立支持不同的I/O标准,但同一组的电器标准必须一致,否则综合时会报错。IOB通过软件的灵活配置(一般指约束文件),可适应不同的电气标准核I/O物理特性,可调整驱动电流的大小,还可以改变上下拉电阻的阻值。

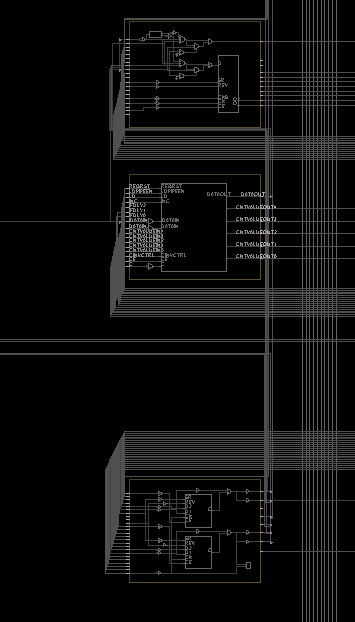

IOB的结构如上,PAD即与外界连接焊盘引脚,同时有一个IBUF和OBUF。当配置为output时,连接左边的OBUF,配置为input时,连接右边的IBUF。在FPGA中,每一个IOB都有与之对应的一个xIOI3模块(,有LIOI3和RIOI3之分,由三个触发器Flip-Flop组成,TFF,OFF和IFF),且其布线资源比较固定,如下所示

切换到逻辑资源视角且放大某一个xIOI3看如下所示

使用xIOI3中的触发器有一个较大的好处,就是其布线资源固定,且最靠近各个引脚,可以实现较低的延迟,在某些特定的场合如高速数据采样下,使用xIOI3可以实现良好的采样效果。如果不使用IOB的触发器而连接普通的Slice内部寄存器,则信号进入第一级寄存器的布线会因为每次综合结果的不同而各有不同,且由于Slice距离接口较远,有可能导致高速信号的采样不正确,不满足时序要求。

一般情况下IOB的寄存器缺省为OFF,如果需要设置接口的寄存器,则在约束文件中应该约束

set_property IOB TRUE {get_ports xxx}

可以通过写两个完全一致的代码,在.xdc文件下约束为TRUE和FALSE,即可发现区别。

CLB——可编程逻辑模块

【注】此部分直接从FPGA基础学习(7) – 内部结构之CLB复制,因为博主总结得很好,也从中学习到了不少知识和方法。

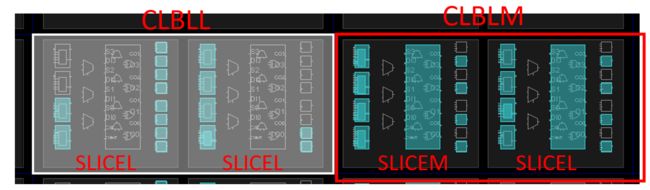

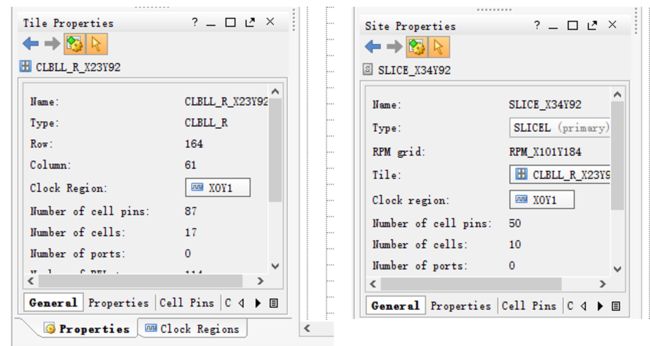

可配置逻辑单元(Configurable Logic Block,CLB)在FPGA中最为丰富,由两个SLICE组成。由于SLICE有SLICEL(L:Logic)和SLICEM(M:Memory)之分,因此CLB可分为CLBLL和CLBLM两类。

点击内部的逻辑单元,通过阴影区别包含的范围,你可以清晰的看到结构划分的层级。在旁边窗口可以清晰的看到选中部分的属性(Properties)。

来,再放大,放大到一个SLICEL,如下图所示。

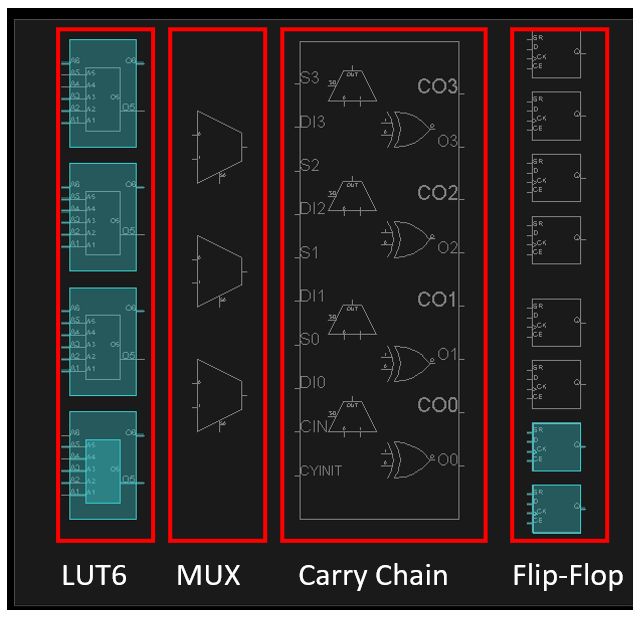

SLICEL和SLICEM内部都包含4个6输入查找表(Look-Up-Table,LUT6)、3个数据选择器(MUX)、1个进位链(Carry Chain)和8个触发器(Flip-Flop),下面分部分介绍的时候,时不时可以再回头看这张结构图。

LUT——查找表

虽然SLICEL和SLICEM的结构组成一样,但两者更细化的结构上略有不同,区别在于LUT6上(如下图所示),从而导致LUT6的功能有所不同(如下表格所示)。

| LUT功能 | SLICEL | SLICEM |

|---|---|---|

| 逻辑函数发生器 | v | v |

| ROM | v | v |

| 分布式RAM | v | |

| 移位寄存器 | v |

上边的功能可以看到,不论是SLICEL还是SLICEM,他们的LUT6都可以作为ROM使用,配置为64x1(占用1个LUT6,64代表深度,1代表宽度)、128x1(占用2个LUT6)和256(占用4个LUT6)的ROM。

另外既然SLICEM中的M代表memory的意思,所以增加了更多存储功能。可以配置为RAM,尤其指分布式RAM。其中RAM的写操作为同步,而读操作是异步的,即与时钟信号无关。如果要实现同步读操作,则要额外占用一个触发器,从而增加了意识时钟的延迟(Latency),但提升了系统的性能。**这就解释了为什么我们实现RAM同步读写的时候,读出输出要延迟一个clk。**一个LUT6可配置64x1的RAM,当RAM的深度大于64时,会占用额外的MUX(F7AMUX,F7BMUX,F8MUX,即一个SLICE中的那3个MUX)。

SLICEM中的LUT还可以配置为移位寄存器,每个LUT6可实现深度为32的移位寄存器,且同一个SLICEM中的LUT6(4个)可级联实现128深度的移位寄存器。

MUX——选择器(复用器)

SLICE中的三个MUX(Multiplexer:F7AMUX,F7BMUX和F8MUX)可以和LUT6联合共同实现更大的MUX。事实上,一个LUT6可实现4选1的MUX。

SLICE中的F7MUX(F7AMUX和F7BMUX)的输入数据来自于相邻的两个LUT6的O6端口。

一个F7MUX和相邻的两个LUT6可实现一个8选1的MUX。因此,一个SLICE可实现2个8选1的MUX。

4个LUT6、F7AMUX、F7BMUX和F8MUX可实现一个16选1的MUX。因此,一个SLICE可实现一个16选1的MUX。

Carry Chain——进位链

进位链用于实现加法和减法运行。就是结构图中,中间那个大的部分,可以看到它内部实际还包含4个MUX和4个2输入异或门(XOR)。

异或运算是加法运算中必不可少的运算。

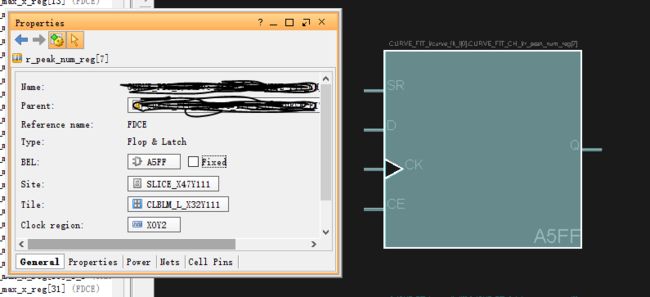

Flip-Flop——触发器

每个SLICE中有8个触发器。这个8个触发器可分为两大类:4个只能配置为边沿敏感的D触发器(Flip-Flop)和4个即可配置为边沿敏感的D触发器又可配置为电平敏感的锁存器(Flop&Latch)。当后者被用作锁存器的时候,前者将无法使用。

当这8个触发器都用作D触发器时,他们的控制端口包括使能端CE、置位/复位端口S/R和时钟端口CLK是对应共享的,也就是就是说共用的。{CE,S/R,CLK}称为触发器的控制集。显然,在具体的设计中,控制集种类越少越好,这样可以提高触发器的利用率。**那么怎样减少控制集种类呢?**我的理解是:

- 减少时钟种类,即频率越少越好;

- 统一规范的设计逻辑,如复位。

S/R端口可配置为同步/异步置位或同步/异步复位,且高有效,因此可形成4种D触发器,如下表所示。

| 原语(Primitive) | 功能描述 | 原语(Primitive) | 功能描述 |

|---|---|---|---|

| FDCE | 同步使能,异步复位 | FDRE | 同步使能,同步复位 |

| FDPE | 同步使能,异步置位 | FDSE | 同步使能,同步置位 |

在我们的常规设计中,FDCE和FDPE占了绝大多数。

BRAM——块RAM

绝大多数FPGA都具有内嵌的块RAM。BRAM可被配置成位单端口RAM,双端口RAM,内容寻址存储器(CAM,Coment-Addressable Memory)和FIFO等常用的存储结构。CAM存储器在其内部的每个存储单元都有一个比较逻辑,写入CAM的数据会和内部的每一个数据进行比较,并返回与端口数据相同的所有数据的地址。

一般的FPGA器件中,单片BRAM的容量为18Kbit,即位宽为18bit、深度为1024,可根据需要改变其位宽和位深,也可将多片BRAM级联构成大规模RAM。

DCM——数字时钟管理器

目前,业内大多数FPGA均提供数字时钟管理,在内部资源中通常整合为CMT(Clock Manage Tile,时钟管理模块),每个区域对应一个CMT,一个CMT由一个MMCM(Mix-mode Clock Manager)和1个PLL(Phase Locked Loop)组成。主要起到频率综合、去抖动和去偏斜的作用。

布线资源

FPGA芯片内部有丰富的布线资源,根据工艺、长度、宽度和分布位置的不同而划分为4类:

- 全局布线资源,用于芯片内部全局时钟和全局复位/置位的布线;

- 长线资源,用于完成芯片bank间的告诉信号和第二全局时钟信号的布线;

- 短线资源,用于完成基本逻辑单元之间的逻辑互联和布线;

- 分布式的布线资源,用于专有时钟、复位等控制信号线。

内嵌的底层功能单元

内嵌功能模块主要指延迟锁定环DLL,锁相环PLL,DSP等软处理核。其主要是一些比较基础的模块用于辅助完成FPGA的基础功能和优化性能。

内嵌专用硬件模块

内嵌专用硬件模块是相对于底层嵌入的软核而言的,FPGA内部集成的强大硬核等效于ASIC电路,如专用乘法器用于提高乘法速度,**串并收发器(SERDES)**将收发速度提升到数十Gbps,如我们经常看到的一些芯片参数(GTx,即Gigabyte Transfer,兆比特传输,GTP可参考文献