AXI总线(top)

AXI总线是一种基于burst的传输总线,适合用在high-bandwidth和low-latency的场景,大致分为5个通道:

- read address

- read data

- write address

- write data

- write response

AXI总线支持:

1)unaligned data transfer,包括SIZE的对齐和Wrap Burst的对齐;

2)Burst-based transactions,只有首地址issued;(burst首地址之后的地址,slave来产生)

3)能够进行multiple outstanding address的发送;(outstanding FIFO与reorder FIFO不一样)

4)能够以out-of-order的方式,完成transaction;(应该outstanding的FIFO大于reorder的FIFO depth)

write data channel是一种从master到slave的传输,在一个写操作中,返回一个整体的response。

read data channel是一种从slave到master的传输,在一个读操作中,response与read data同一通道,分别为transfer返回response

AXI中的每个channel包含两个handshake signal,source提供VALID信号,destination提供READY信号。

写读分别会有source和destination发出last信号,来表示最后一个transfer。

AXI中的interconnect由一系列的master和slave接口来组成,一般有三种topologies:

shared address and data buses;

shared address buses and multiple data buses;

multilayer with multiple address and data buses;

由于很多系统,对于地址的带宽一般都比数据带宽小很多,所以应用最多的还是shared address buses and multiple data buses。

Interconnect中的Register slices,两个作用:trade-off between cycles of latency and maximum frequency of operaton。 每个register slice的插入都会增加一个cycle 的latency。 isolate a longer path to less performance critical。

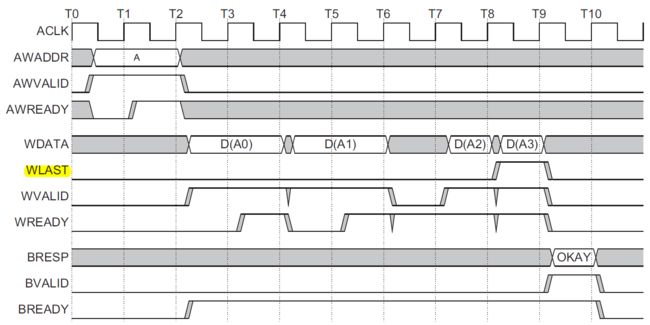

一个write burst传输:

AW通道在下一个clock cycle被采样,W通道然后传输data,R通道最后传输resp。

没有component可以提前结束一个burst,在resp产生error时,也必须将数据写完(可以加strb,控制写数据)或读完然后将数据丢掉。这种情况在访问FIFO时,会影响之后的数据访问,所以这时,要求master发出准确的transfer。

读写地址中的信号:

- AXLEN:burst传输的长度,transfer的个数。计算方式AXLEN + 1。wrap类型的burst只能是2,4,8,16。对于AXI3,incr类型的burst从1-16;对于AXI4,从1-256。

- AXSIZE:每一个transfer中的byte个数。3bit,计算方式2的幂次方,最多128个byte,1024bit。如果AXI BUS比AXSIZE大,应该由interface来决定有效的byte lanes。写操作strb信号,读操作无操作。

- AXBURST:表示burst的type。fixed burst:每次的address相同,可以用在loading/emptying FIFO。INCR burst:address依次增加,以SIZE的byte数为单位。可以用在正常的sequential memory. WRAP burst:最大地址称为wrap boundary,与AXSIZE*AXLEN相对齐。循环读写此区间内的数据。可以进行cache line的访问。length必须是2的幂数。初始地址必须是与size对齐的,到了最大地址之后,会wrap会小的地址。

- AXLOCK:AXI3中包含exclusive transaction和lock transaction,AXI4中只包含exclusive transaction。

- AXCACHE:在AXI3中,4bit数据分别是buffer,cache,read allocate, write allocate。bufferable多用在write操作中,表示可以由一个中间节点来返回response信号。cacheable在读操作中,表示可以prefetch一些数据,在写操作中,表示可以将不同的write merged together。RA针对,读操作。WA针对,写操作。只有在cacheable有效的情况下,这两个bit才有效。在AXI4中,cache bit改名为modefiable,RA,WA的概念被更新,将不用的哪一个allocate bit改为other allocate。

- AXPROT:3bit数据分别表示,privilage/secure/instruction。在amba总线中与ARM core的状态联系在一起。

- AXQOS:AXI4中的信号,4bit的quality,用在每个读写transaction的channel中,用作priority indicator,越大的值,表示越高的优先级,默认值是4’b0000表示接口不实现QoS。master侧必须根据scenario来产生具体的QoS值,而slave根据QoS的值来决定不同transaction的值。如用在DDR Controller中,决定transaction的优先级来转换为DDR的读写次序。

- AXREGION:AXI4中的信号,4bit可以表示16个region。主要作用是简化slave中的address decode。由interconnect在做address decode时产生。否则使用默认值。同样必须在4k范围内。

- AXUSER:AXI4中的信号,arm不推荐使用。存在于五个通道中。

- RRESP/BRESP:表示四种错误,OKAY/EXOKAY/SLVERR/DECERR。

- EXOKAY,用在exclusive的访问,

- SLVERR,表示trans已经经过interconnect,到达slv,但是slv返回error。比如,对read-only区域的写,lowe-power状态下的访问,不支持的size,burst等。

- DECERR,表示interconnect的route出错,被导向interconnect内部的一个default slave。由于axi的out-of-order特性,晚的transfer的resp可能会更早的返回,早的transfer的resp返回的比较晚,master需要可以处理这样的情况的。

读写数据通道:

- WLAST/RLAST:表示一个transaction中的最后一个transfer。

- WSTRB:只存在于WDATA channel,选取有效的beats。

- Lower-power signals:CSYSREQ/CSYSACK:两个与clock controller的handshake signals,来离开和进入lower_power state。针对带有power-down/up的peripheral。

- CACTIVE:表示(不)需要clock,也可以用在没有power-down/up的外设,与clock controller单端通信。三个信号也可以用在一个power domain中。power-down/up的外设需要这三个信号,而没有power-down/up的外设只需要一个信号。

AXI中的reset,reset信号可以在assert时,async,但是在deassert时,必须sync与ACLK。master必须将AWVALID,ARVALID,WVALID拉低。slave必须将RVALID,BVALID拉低。

AXI中的handshake signal,所有的通道。source不允许等READY信号来触发VALID信号,而且一旦VALID信号触发就必须等到READY信号有效。ready信号可以在valid信号无效时,有toggle的变动。destination允许等到VALID信号有效,而触发READY。

一般的READY信号,有两种产生方式:

1)等VALID有效后,READY信号有效。

2)default READY信号有有效。

ARM官方的建议,AWREADY/WREADY/BREADY/ARREADY/RREADY都default为1,这样可以让传输更快的传输,但是slave端必须准备好。

在read data channel中,RVALID必须等到ARVALID和ARREADY信号都assert,RVALID才能assert。R通道必须在AR通道完成之后,才开始。在write data channel中,BVALID必须等到WVALID和WREADY信号都assert,BVALID才能assert(AXI3)。

b通道必须在aw通道完成之后,才开始,但是在axi3中aw和w通道之间的关系,是没有约束的。

AWREADY的assert可以等到AWVALID和WVALID信号有效后。WVALID的assert不可以等到AWREADY信号有效。

在write data channel中,BVALID必须等到AWVALID和AWREADY,WVALID和WREADY信号都assert,BVALID才能assert(AXI4)。主要是因为AXI4中取消了wid,w通道的顺序与aw通道的顺序是相同的。

在AXI3中,由于AW通道和w通道完全没有关联,所以aw和w的传输顺序是任意的,aw可以在w之后,aw也可以与w同一拍。但是AXi4中,由于wid的取消,w通道只能紧接着aw通道,就不存在data ahead of address的传输。(在axi3中,只要aw通道插入的RS比w通道多一些,就可能出现data ahead of address)

AXI中的slave可以归结为两大类:Memory slave,一般要求handle all transaction type。

Peripheral slave,只要求work for a defined method of access。

Transaction identifiers:一般来说interconnect都会在ARID,AWID,WID(AXI4已删除)中增减一些addition bits。interconnect在送来的transaction中增加addition bits(AWID/WID/ARID)来表示各个master port。因为各个master port可能会有ID冲突。interconnect在slave发送过来的transaction中减少addition bits(RID/BID),来发送给master。 这样,slave中的ID号总是比master中的ID号,多几位。对于只支持single order的interface,可以将ID的output,tie掉。

AXI中的order model: 同一ID的transaction必须是ordered,不同的ID的transaction order no restrict。同一ID,slave端必须按接收到的address顺序来传输。

outstanding address是指:master可以不等该transaction结束,就发送下一个transaction的address。

complete transaction out of order是指:transaction之间的完成顺序与issue的order可以不同。 但是同一个burst中的transfer必须是按顺序的。对于ARID,同一个master返回的同一个ID的transaction必须是按address的顺序来发送的。在interconnect中,同一ID的transaction必须按master issue address的order来返回。对于AWID和ARID,协议中没有限制,如果master要求必须是先读后写,master端必须保证。简单的master可以选择,transaction按顺序来处理,一次一个transaction,不支持outstanding。

read data reordering depth与slave中可以pending的address的个数相同。(也叫interleave depth)

按顺序处理transaction的slave,等于read data reordering depth为1。

Writing data ordering:如果slave不支持interleave的write,master在发送write data的时候,与address的顺序必须是一致的。

同样interconnect在处理的过程中,也必须保证data的顺序与address的顺序也是一致的。(与WID号无关)

interleave的操作只能用在不同ID号的burst中。

interleave depth与slave中支持的pending address个数相同。

AXI中的interleave操作是指burst之间是有交叠的,interleave的深度,表示可以交叠的个数。

但是这个特性,会很大程度的增加IP的设计复杂度,(自己设计的master一般不会有这个feature,但是arm本身的core是可能有的,

一般情况下,对大多数的master,interleave write不是很必要,所以master可以以address的order来发送data,

只有当master从不同的多个source,像interconnect写数据时,才需要进行interleave操作。

读写之间的interaction:协议中没有规定读写之间的关系,所以必须由master保证一个结束之后,才发送下一个。

对于peripheral device,master保证transaction必须按他们issued order来到达peripheral。一个接一个,不进行outstanding。

对于memory device,master,需要有addr check保证如果有same/overlapping address,

transaction也必须一个个发送,不能outstanding。

对于unaligned transfer,master可以提供一个lower-address,unaligned address,通过byte lanes strobes信号来signal unaligned address。

或者也可以传输aligned transfer。

先传输低地址的非burst transfer,后按aligning的burst传输:(白色表示传输数据的地址),此时unaligned addr会占用一个transfer/beat。

对于narrow transfers,每个beat的byte lanes是不同的,针对burst,每次增加的地址,由size计算得到。

例如一个burst length=4的read,起始地址为xx111,arsize=64bit,bus中的width=128bit.

则首先master发出一个起始地址为7的,transfer,此时从slave拿到的数来自[63:56];

master发出下一个起始地址为0的,transfer,此时从slave拿到的数来自[31:0];

master发出下一个起始地址为8的,transfer,此时从slave拿到的数来自[63:32];

master发出下一个起始地址为0的,transfer,此时从slave拿到的数来自[31:0];

至此四个length的burst传输结束。

axi中的数据,是不区分大小端的,直接将memory中的低位数据,放在data bus的低位。byte-invariant

实际数据的大小端,需要由slave来自己调整。

对于一个burst传输,不能超过4K的地址空间,主要是为了防止burst横跨两个slave。

通过burst,横穿两个IP,会导致第二个IP的地址出错,从而数据出错,所以必须有这样的限制机制。

因为memory page size的一般就是4K,所以这里设置为4K Byte。

AXI4中取消了W通道的id号信号,w通道的次序保证与aw通道的次序相同。

关于bufferable和cacheable:cacheable表示可不可以直接去cache中寻找数据以及cache miss之后的操作,如allocated等。

bufferable主要考虑write操作中,response返回的执行者是不是最终的slave发出的。

关于valid和ready信号,数据输出者,发出valid信号,数据接收者,发出ready信号。

eg:arm读数据,rvalid由matrix提供,ready由arm core提供。

AXI中的5组信号,可以是master---interconnect,可以是interconnect----slave,也可以是master-slave