- zynq串口的例子vio_uart

vio_uartvio_uart是一个基于串口通信的内存映射接口模块,其功能类似于Vivado中的VIOIP。它用于实现主从设备之间的数据采集与控制命令交互。两类寄存器vio_uart提供了采集寄存器和一个控制寄存器o_acq_gram_x:模拟采集器寄存器(生成采样数据)i_ctrl_gram_x:模拟控制器寄存器(接收主控写入的控制命令)地址映射类型信号名地址范围描述采集寄存器o_acq_gr

- FPGA芯片厂商及关键的开发测试工具

Chip Design

xPUChipDesignfpga开发

以下是结合2025年技术动态整理的。一、FPGA芯片主要厂商及产品系列厂商芯片系列典型特点目标市场AMD/XilinxVersal,Kintex,Artix,Zynq高性能异构计算(AI引擎+FPGA+CPU)数据中心、5G、航空航天Intel(Altera)Stratix,Arria,Agilex,Cyclone高带宽内存集成(HBM),支持CXL协议网络加速、边缘计算LatticeCertus

- Xilinx Vivado开发环境快速导出hdf文件(bat批处理)

XilinxFPGA使用Vivado开发环境创建MicroBlaze软核或ZYNQPS侧SDK逻辑工程时,需要FPGA侧搭建的硬件平台文件,即hdf文件,常规方式是编译完成生成bit流文件后,通过File->Export->ExportHardware菜单来导出,在弹出的菜单再选择要导出的路径和文件名称等,这个过程比较繁琐,通过观察TCL终端窗口:update_compile_order-file

- 【AXI】读重排序深度

oahrzvq

总线AMBAAXI

我们以DDR4存储控制器为例,设计一个读重排序深度为3的具体场景,展示从设备如何利用3级队列优化访问效率:基础设定从设备类型:DDR4存储控制器(支持4个存储体Bank0-Bank3)读重排序深度:3(允许同时跟踪3个未完成读请求)访问延迟特征:Bank激活后访问:3周期(低延迟)Bank预充电后访问:7周期(高延迟)主机请求序列(按时间顺序发送):时间点请求标识ARID值目标Bank地址描述T0

- [FPGA AXI IP] AXI Crossbar

AXICrossbarIP详细介绍概述AXICrossbar是属于AXIInterconnectIPSuite的一部分,专为AXI4、AXI3和AXI4-Lite协议设计,提供多个AXI主设备(Master)和从设备(Slave)之间的灵活互联功能。它通过交叉开关(Crossbar)架构实现高效的数据路由,支持多主多从的点对点连接,广泛应用于FPGA和SoC系统设计,特别是在需要复杂AXI总线互联

- [AXI] AXI Interconnect

AXIInterconnectIP详细介绍概述AXIInterconnect专为AXI4、AXI3和AXI4-Lite协议设计,提供多个AXI主设备(Master)和从设备(Slave)之间的灵活互联功能。它通过模块化架构实现高效的数据路由、协议转换、数据宽度转换和时钟域转换,广泛应用于FPGA和SoC系统设计,特别是在需要复杂AXI总线互联的场景,如多核处理器系统、视频处理、网络通信和硬件加速器

- 【ARM AMBA AXI 入门 5.1 - QoS是什么?QoS是怎么工作的? 】

主公讲 ARM

#ARMAMBAAXI系列QoS是什么?QoS怎么工作的?AXIQoS

请阅读【嵌入式及芯片开发学必备专栏】转自:揭秘数通知识:QoS是什么?QoS是怎么工作的?(一)文章目录QoS概述综合服务和差分服务QoS工具报文分类报文标记流量监管和整形工具拥塞管理工具拥塞避免工具队列策略FIFO(先进先出队列,FirstInFirstOutQueue)PriorityQueue(优先队列PQ)Weighted-fairQueue(加权平均队列WFQ)丢弃策略我们在学习嵌入的时

- FDMA读写AXI BRAM交互:FPGA高速数据传输的核心技术

芯作者

D1:ZYNQ设计fpga开发

在图像处理系统中,当1080P视频流以每秒60帧的速度传输时,传统DMA每帧会浪费27%的带宽在地址管理上——而FDMA技术能将这些损失降至3%以内现代FPGA系统中,高效数据搬运往往是性能瓶颈的关键所在。当你在手机上流畅播放4K视频、在自动驾驶系统中实时处理激光雷达点云时,背后都依赖于FDMA(FlexibleDirectMemoryAccess)与AXIBRAM的高效交互技术。本文将深入探讨这

- 基于ZYNQ7000的AD9226采集卡实现(1、采集数据到PL)

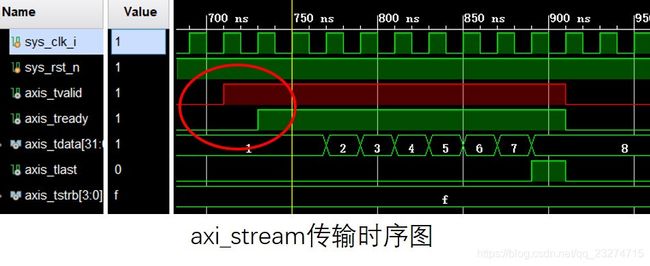

目标AD9226为12位,65MHz采样率ADC。基于ZYNQ7010平台,PL端采集AD数据,通过内部AXI总线,将数据搬运到PS的DDR。可以将如上目标分解为3个小目标实现PL采集AD9226模块,采集后的数据为AXIS接口。实现PL侧DMA可搬运AXIS数据到PS的DDR,可配置地址,帧长度,帧数量等。实现PS侧DMA驱动本章节实现第一个小目标:硬件:主控板采集模块模块引脚功能:D0-D11

- ZYNQ MPSOC PL端DDR4读写--介绍(1)

LEEE@FPGA

FPGA高速接口开发fpga开发DDR4

1DDR4介绍DDR4SDRAM(Double-Data-RateFourthGenerationSynchronousDynamicRandomAccessMemory,简称为DDR4SDRAM),是一种高速动态随机存取存储器,它属于SDRAM家族的存储器产品,提供了相较于DDR3SDRAM更高的运行性能与更低的电压,并被广泛的应用于计算机的运行缓存。DDR4主要特点1)更高频率与带宽起步频率为

- RDMA简介8之AXI 总线协议分析1

tiantianuser

RDMARDMAverilog高速传输Vivado

AXI总线是一种高速片内互连总线,其定义于由ARM公司推出的AMBA协议中,主要用于高性能、高带宽、低延迟、易集成的片内互连需求。AXI4总线是第四代AXI总线,其定义了三种总线接口,分别为:AXI4、AXI4-Lite和AXI4-Stream接口。其中AXI4也称为AXI4-Full是一种基于地址的高性能传输接口,其支持乱序传输、突发传输等传输方式,同时通过独立的地址总线,实现高性能的数据地址映

- ZYNQ无DMA的四路HP总线极限性能探索

芯作者

D1:ZYNQ设计fpga开发硬件工程智能硬件

深入挖掘AXIHP总线的直接传输潜力,突破传统DMA的性能瓶颈一、HP总线:ZYNQ系统的"高速公路"在XilinxZYNQ架构中,HP(HighPerformance)总线是连接PS(处理器系统)和PL(可编程逻辑)的关键通道。传统方案依赖DMA控制器进行数据传输,但当我们需要超低延迟或确定性响应时,无DMA的直接CPU控制成为更优选择。本文将揭示如何通过四路HP总线实现惊人的24GB/s理论带

- Xilinx XC7K70T-2FBG484I 可编程罗辑芯片

深圳市泰凌微电子

音视频可编程罗辑芯片

XC7K70T-2FBG484I具有高达478K逻辑单元,34MbRAM,1920DSP片,2845GMAC/sDSP性能,32个收发器,12.5Gb/s收发器速度,800Gb/s串行带宽,x8Gen2PCIe接口,500个I/O引脚,VCXO组件,高级可扩展接口4(AXI4)IP,灵活混合信号(AMS)集成,以及1.2至3.3VI/O电压。Kintex®-7系列适用于3G与4G无线应用,平板显示

- 复旦微ZYNQ SOC AXI_DMA高速数据传输实战指南

芯作者

D1:ZYNQ设计fpga开发

突破传统瓶颈:零拷贝+双缓冲实现2.4GB/s传输速率AXI_DMA在异构计算中的核心价值在复旦微ZYNQSOC系统中,AXI_DMA是连接PS(处理系统)和PL(可编程逻辑)的高速数据通道。本文通过创新性的零拷贝双缓冲架构,实现2.4GB/s的稳定传输速率,相比传统方案提升300%!我们将从硬件设计到软件优化,揭秘工业级DMA应用的完整开发流程。一、系统架构创新设计1.1传统DMA方案瓶颈分析方

- vxWorks7.0下基于zynq的boot启动程序

hongbozhu_1981

最近工作有点忙,好久没有更新内容,前段时间抽空做了vxWorks7.0下的基于zynq的boot程序,在此做个总结。vxworks7.0支持三种不同的boot程序:第一种uboot,第二种vxworks6.9.x以上的bootloader,第三种bootapp,关于uboot的创建方法在前面的博文中已经提到过,bootloader6.9的话,因为我不在使用6.9的版本,所以在此也就不做介绍,今天我

- 实时系统vxWorks-Zynq7020 axi gpio使用

不只会拍照的程序猿

实时vxWorks听说ZYNQ嵌入式物联网ZYNQvxworks实时操作系统

概述这篇文章将为大家展示如何编写vxWorks应用程序来操作axigpio。注意开发环境:vxWorks6.9.4,workbench3.3.5,开发板:TLZ7x-EasyEVM-A3。详细操作方法参见文章《实时系统vxWorks-Zynq7020移植vxWorks》和《

- VxWorks在Zynq平台上的移植详细流程

缪超争Lighthearted

VxWorks在Zynq平台上的移植详细流程【下载地址】VxWorks在Zynq平台上的移植详细流程本资源文档全面解析了将WindRiver的嵌入式操作系统VxWorks移植至XilinxZynq系列SoC平台的过程。Zynq平台以其独特的FPGA与ARMCortex-A处理单元结合的设计,广泛应用于工业控制、航空航天、通信设备等多个领域。本文档深入浅出,旨在帮助开发者理解和掌握如何在这一平台上成

- 深入实战:ZYNQ中AXI BRAM打通PS与PL数据交互的高速通道

芯作者

D1:ZYNQ设计fpga开发智能硬件硬件工程

在ZYNQ异构计算平台上,高效的数据交互是发挥PS(处理器系统)与PL(可编程逻辑)协同计算优势的关键。本文将深入探讨利用AXIBRAM控制器实现PS与PL间共享内存通信的方案,提供详实的代码、创新优化思路及性能分析,助你构建高速数据通道。一、为何选择AXIBRAM?在ZYNQ中,PS与PL交互的常用方式包括:AXIDMA:适合大数据流传输AXIGPIO:仅适合小数据量控制AXIBRAM:低延迟、

- Ajax 核心知识点全面总结

YD_1989

前端基础微服务面试ajaxokhttp前端

文章目录Ajax核心知识点全面总结一、Ajax基础概念1、定义2、核心特点二、Ajax工作原理与核心组件1、工作流程2、XMLHttpRequest(XHR)对象三、Ajax请求方法与参数1、常见请求方法2、请求参数处理四、Ajax异步与错误处理1、异步处理2、错误处理五、跨域资源共享(CORS)与解决方案1、跨域问题2、解决方案六、Ajax与现代替代方案1、FetchAPI(ES6+)2、Axi

- AXI (Transaction Attributes)

Jay丶ke

AMBA协议verilogfpga开发

目录:AXI(TransactionAttributes)1.事务类型与属性:2.存储相关属性信号:3.存储类型:AXI(TransactionAttributes)1.事务类型与属性:现代计算机架构中,对memory的读写有若干种优化,prefetch,cache,writebuffer。同时,对host来说,一些其他的外部设备的寄存器或者外部设备的内存也会被映射到host端的地址上。这部分地址

- 用Zynq实现脉冲多普勒雷达信号处理:架构、算法与实现详解

神经网络15044

算法仿真模型python信号处理架构算法

用Zynq实现脉冲多普勒雷达信号处理:架构、算法与实现详解脉冲多普勒(PD)雷达是现代雷达系统的核心技术之一,广泛应用于机载火控、气象监测、交通监控等领域。其核心优势在于能在强杂波背景下检测运动目标,并精确测量其径向速度。本文将深入探讨如何利用XilinxZynqSoC(FPGA+ARM)平台高效实现PD雷达的信号处理链,涵盖理论基础、系统架构设计、关键算法实现及优化策略。一、脉冲多普勒雷达基础原

- ZYNQ学习记录FPGA(五)高频信号中的亚稳态问题

DQI-king

ZYNQ学习记录数据库

一、亚稳态概述:1.1触发器在讲解亚稳态前,先介绍一下亚稳态的源头——触发器。1.1.1基本概念在数字电路里,触发器(Flip-Flop)是一种存储元件,常用于同步电路中存储二进制数据。它是由逻辑门(如与门、或门、非门)构成的时序电路,能够根据时钟信号的变化来存储和改变其输出状态。触发器分为D触发器(DataFlip-Flop)、T触发器(ToggleFlip-Flop)、JK触发器和SR触发器(

- [AXI] AXI Data Width Converter

S&Z3463

FPGAAXIIPfpga开发

AXIDataWidthConverterIP详细介绍概述AXIDataWidthConverter属于AXIInfrastructureIPSuite。该IP核专为AXI4和AXI4-Lite协议设计,用于在不同数据宽度的AXI主设备(Master)和从设备(Slave)之间进行数据宽度转换。它通过内部打包、解包和缓冲机制,确保跨宽度传输的数据完整性和协议合规性,广泛应用于FPGA和SoC系统设

- 使用ZYNQ芯片和LVGL框架实现用户高刷新UI设计系列教程(第十七讲)

尤老师FPGA

Lvglui

这一期讲解的控件是表格,表格是由包含文本的行、列和单元格构建的。表格对象非常轻量级,因为仅存储文本。没有创建真实的对象,但它们只是即时绘制的。在lvgl中的默认格式如下图所示:在GUI_Guider中可以改变表格的行列的元素个数以及表格主体的背景、边框和阴影。具体代码如下图所示://Writecodesscreen_1_table_1//创建一个名为screen_1_table_1的表格并将其添加

- ZYNQ笔记(二十):Clocking Wizard 动态配置

W以至千里

ZYNQ笔记fpga开发

版本:Vivado2020.2(Vitis)任务:ZYNQPS端通过AXI4Lite接口配置ClockingWizardIP核输出时钟频率目录一、介绍二、寄存器定义三、配置四、PS端代码一、介绍Xilinx的ClockWizardIP核用于在FPGA中生成和管理时钟信号。它支持动态重配置(DynamicReconfiguration),允许在运行时通过AXI4-Lite接口或DRP接口(这两个接口

- 【FPGA】IO电平标准

步达硬件

ZYNQ嵌入式硬件fpga开发嵌入式硬件单片机

【FPGA】IO电平标准1LVCMOS(低压CMOS)1.1TTL、CMOS、LVTTL、LVCMOS逻辑电平定义1.2ZYNQ-7000PS、PLIOLevel示例2LVTTL(低压TTL)3HSTL(高速TTL)4SSTL(高速)5LVDS(高速)参考资料FPGA支持多种IO电平标准,这些标准包括但不限于TTL,CMOS,LVTTL,LVCMOS,ECL,PECL,LVPECL,RS232

- XDMA pcie环路测试

hahaha6016

硬件设计fpga开发

图-1测试框架图一、上图中,主要用于测试XDMA的axilite寄存器访问和axi-memory大数据访问,图1完成了逻辑设计。二、如果是windows环境,进行相关驱动开发,打驱动,然后进行应用层数据读写操作参考:(WIN)S04-CH01PCIEXDMA开发环境搭建以及环路测试-4-PCIEUISRC工程师开源站-三、如果是和ARM交互,那就是使用linux驱动,然后应用层进行数据读写操作参考

- 深入剖析ZYNQ Linux动态PL配置:xdevcfg驱动创新实践指南

芯作者

D1:ZYNQ设计fpga开发

一、ZYNQ动态重配置技术解析1.1可编程逻辑的革命性价值XilinxZYNQ系列SoC的划时代设计将ARM处理系统(PS)与FPGA可编程逻辑(PL)深度融合,创造出独特的异构计算架构。传统FPGA开发模式中,比特流烧写需要停机操作,而动态重配置技术彻底打破了这一限制,使得:工业设备可在线切换通信协议(Modbus/Profinet/EtherCAT)机器视觉系统动态加载不同图像处理流水线5G基

- XILINX ZYNQ700系列 FPGA简介、开发环境、应用领域、学习要点

GJZGRB

fpga开发学习嵌入式硬件硬件工程ZYNQ7000

XILINXZYNQ-7000系列是赛灵思(Xilinx)推出的可扩展处理平台(SoCFPGA),将ARMCortex-A9双核处理器(属于“处理系统”,PS)与可编程逻辑(PL,即传统FPGA部分)集成在单芯片中,兼顾通用计算、实时控制与硬件加速能力。其核心优势是“软硬件协同设计”,广泛应用于对性能、功耗和灵活性要求较高的嵌入式领域。一、ZYNQ-7000系列简介1.架构特点双核心架构:PS(P

- ZYNQ7020学习历程

m0_61275923

学习fpga开发

一、介绍Zynq的全称是Zynq-7000AllProgrammableSoC,是它由一个双核ARMCortex-A9处理器和一个传统的现场可编程门阵列(FPGA)逻辑部件组成的。作为片上系统(SystemonChip,SOC),仅使用单个硅芯片即可实现整个系统的功能。Zynq是由两个主要部分组成的:一个是由双核ARMCortex-A9为核心构成的处理系统(PS,ProcessingSystem)

- 戴尔笔记本win8系统改装win7系统

sophia天雪

win7戴尔改装系统win8

戴尔win8 系统改装win7 系统详述

第一步:使用U盘制作虚拟光驱:

1)下载安装UltraISO:注册码可以在网上搜索。

2)启动UltraISO,点击“文件”—》“打开”按钮,打开已经准备好的ISO镜像文

- BeanUtils.copyProperties使用笔记

bylijinnan

java

BeanUtils.copyProperties VS PropertyUtils.copyProperties

两者最大的区别是:

BeanUtils.copyProperties会进行类型转换,而PropertyUtils.copyProperties不会。

既然进行了类型转换,那BeanUtils.copyProperties的速度比不上PropertyUtils.copyProp

- MyEclipse中文乱码问题

0624chenhong

MyEclipse

一、设置新建常见文件的默认编码格式,也就是文件保存的格式。

在不对MyEclipse进行设置的时候,默认保存文件的编码,一般跟简体中文操作系统(如windows2000,windowsXP)的编码一致,即GBK。

在简体中文系统下,ANSI 编码代表 GBK编码;在日文操作系统下,ANSI 编码代表 JIS 编码。

Window-->Preferences-->General -

- 发送邮件

不懂事的小屁孩

send email

import org.apache.commons.mail.EmailAttachment;

import org.apache.commons.mail.EmailException;

import org.apache.commons.mail.HtmlEmail;

import org.apache.commons.mail.MultiPartEmail;

- 动画合集

换个号韩国红果果

htmlcss

动画 指一种样式变为另一种样式 keyframes应当始终定义0 100 过程

1 transition 制作鼠标滑过图片时的放大效果

css

.wrap{

width: 340px;height: 340px;

position: absolute;

top: 30%;

left: 20%;

overflow: hidden;

bor

- 网络最常见的攻击方式竟然是SQL注入

蓝儿唯美

sql注入

NTT研究表明,尽管SQL注入(SQLi)型攻击记录详尽且为人熟知,但目前网络应用程序仍然是SQLi攻击的重灾区。

信息安全和风险管理公司NTTCom Security发布的《2015全球智能威胁风险报告》表明,目前黑客攻击网络应用程序方式中最流行的,要数SQLi攻击。报告对去年发生的60亿攻击 行为进行分析,指出SQLi攻击是最常见的网络应用程序攻击方式。全球网络应用程序攻击中,SQLi攻击占

- java笔记2

a-john

java

类的封装:

1,java中,对象就是一个封装体。封装是把对象的属性和服务结合成一个独立的的单位。并尽可能隐藏对象的内部细节(尤其是私有数据)

2,目的:使对象以外的部分不能随意存取对象的内部数据(如属性),从而使软件错误能够局部化,减少差错和排错的难度。

3,简单来说,“隐藏属性、方法或实现细节的过程”称为——封装。

4,封装的特性:

4.1设置

- [Andengine]Error:can't creat bitmap form path “gfx/xxx.xxx”

aijuans

学习Android遇到的错误

最开始遇到这个错误是很早以前了,以前也没注意,只当是一个不理解的bug,因为所有的texture,textureregion都没有问题,但是就是提示错误。

昨天和美工要图片,本来是要背景透明的png格式,可是她却给了我一个jpg的。说明了之后她说没法改,因为没有png这个保存选项。

我就看了一下,和她要了psd的文件,还好我有一点

- 自己写的一个繁体到简体的转换程序

asialee

java转换繁体filter简体

今天调研一个任务,基于java的filter实现繁体到简体的转换,于是写了一个demo,给各位博友奉上,欢迎批评指正。

实现的思路是重载request的调取参数的几个方法,然后做下转换。

- android意图和意图监听器技术

百合不是茶

android显示意图隐式意图意图监听器

Intent是在activity之间传递数据;Intent的传递分为显示传递和隐式传递

显式意图:调用Intent.setComponent() 或 Intent.setClassName() 或 Intent.setClass()方法明确指定了组件名的Intent为显式意图,显式意图明确指定了Intent应该传递给哪个组件。

隐式意图;不指明调用的名称,根据设

- spring3中新增的@value注解

bijian1013

javaspring@Value

在spring 3.0中,可以通过使用@value,对一些如xxx.properties文件中的文件,进行键值对的注入,例子如下:

1.首先在applicationContext.xml中加入:

<beans xmlns="http://www.springframework.

- Jboss启用CXF日志

sunjing

logjbossCXF

1. 在standalone.xml配置文件中添加system-properties:

<system-properties> <property name="org.apache.cxf.logging.enabled" value=&

- 【Hadoop三】Centos7_x86_64部署Hadoop集群之编译Hadoop源代码

bit1129

centos

编译必需的软件

Firebugs3.0.0

Maven3.2.3

Ant

JDK1.7.0_67

protobuf-2.5.0

Hadoop 2.5.2源码包

Firebugs3.0.0

http://sourceforge.jp/projects/sfnet_findbug

- struts2验证框架的使用和扩展

白糖_

框架xmlbeanstruts正则表达式

struts2能够对前台提交的表单数据进行输入有效性校验,通常有两种方式:

1、在Action类中通过validatexx方法验证,这种方式很简单,在此不再赘述;

2、通过编写xx-validation.xml文件执行表单验证,当用户提交表单请求后,struts会优先执行xml文件,如果校验不通过是不会让请求访问指定action的。

本文介绍一下struts2通过xml文件进行校验的方法并说

- 记录-感悟

braveCS

感悟

再翻翻以前写的感悟,有时会发现自己很幼稚,也会让自己找回初心。

2015-1-11 1. 能在工作之余学习感兴趣的东西已经很幸福了;

2. 要改变自己,不能这样一直在原来区域,要突破安全区舒适区,才能提高自己,往好的方面发展;

3. 多反省多思考;要会用工具,而不是变成工具的奴隶;

4. 一天内集中一个定长时间段看最新资讯和偏流式博

- 编程之美-数组中最长递增子序列

bylijinnan

编程之美

import java.util.Arrays;

import java.util.Random;

public class LongestAccendingSubSequence {

/**

* 编程之美 数组中最长递增子序列

* 书上的解法容易理解

* 另一方法书上没有提到的是,可以将数组排序(由小到大)得到新的数组,

* 然后求排序后的数组与原数

- 读书笔记5

chengxuyuancsdn

重复提交struts2的token验证

1、重复提交

2、struts2的token验证

3、用response返回xml时的注意

1、重复提交

(1)应用场景

(1-1)点击提交按钮两次。

(1-2)使用浏览器后退按钮重复之前的操作,导致重复提交表单。

(1-3)刷新页面

(1-4)使用浏览器历史记录重复提交表单。

(1-5)浏览器重复的 HTTP 请求。

(2)解决方法

(2-1)禁掉提交按钮

(2-2)

- [时空与探索]全球联合进行第二次费城实验的可能性

comsci

二次世界大战前后,由爱因斯坦参加的一次在海军舰艇上进行的物理学实验 -费城实验

至今给我们大家留下很多迷团.....

关于费城实验的详细过程,大家可以在网络上搜索一下,我这里就不详细描述了

在这里,我的意思是,现在

- easy connect 之 ORA-12154: TNS: 无法解析指定的连接标识符

daizj

oracleORA-12154

用easy connect连接出现“tns无法解析指定的连接标示符”的错误,如下:

C:\Users\Administrator>sqlplus username/

[email protected]:1521/orcl

SQL*Plus: Release 10.2.0.1.0 – Production on 星期一 5月 21 18:16:20 2012

Copyright (c) 198

- 简单排序:归并排序

dieslrae

归并排序

public void mergeSort(int[] array){

int temp = array.length/2;

if(temp == 0){

return;

}

int[] a = new int[temp];

int

- C语言中字符串的\0和空格

dcj3sjt126com

c

\0 为字符串结束符,比如说:

abcd (空格)cdefg;

存入数组时,空格作为一个字符占有一个字节的空间,我们

- 解决Composer国内速度慢的办法

dcj3sjt126com

Composer

用法:

有两种方式启用本镜像服务:

1 将以下配置信息添加到 Composer 的配置文件 config.json 中(系统全局配置)。见“例1”

2 将以下配置信息添加到你的项目的 composer.json 文件中(针对单个项目配置)。见“例2”

为了避免安装包的时候都要执行两次查询,切记要添加禁用 packagist 的设置,如下 1 2 3 4 5

- 高效可伸缩的结果缓存

shuizhaosi888

高效可伸缩的结果缓存

/**

* 要执行的算法,返回结果v

*/

public interface Computable<A, V> {

public V comput(final A arg);

}

/**

* 用于缓存数据

*/

public class Memoizer<A, V> implements Computable<A,

- 三点定位的算法

haoningabc

c算法

三点定位,

已知a,b,c三个顶点的x,y坐标

和三个点都z坐标的距离,la,lb,lc

求z点的坐标

原理就是围绕a,b,c 三个点画圆,三个圆焦点的部分就是所求

但是,由于三个点的距离可能不准,不一定会有结果,

所以是三个圆环的焦点,环的宽度开始为0,没有取到则加1

运行

gcc -lm test.c

test.c代码如下

#include "stdi

- epoll使用详解

jimmee

clinux服务端编程epoll

epoll - I/O event notification facility在linux的网络编程中,很长的时间都在使用select来做事件触发。在linux新的内核中,有了一种替换它的机制,就是epoll。相比于select,epoll最大的好处在于它不会随着监听fd数目的增长而降低效率。因为在内核中的select实现中,它是采用轮询来处理的,轮询的fd数目越多,自然耗时越多。并且,在linu

- Hibernate对Enum的映射的基本使用方法

linzx0212

enumHibernate

枚举

/**

* 性别枚举

*/

public enum Gender {

MALE(0), FEMALE(1), OTHER(2);

private Gender(int i) {

this.i = i;

}

private int i;

public int getI

- 第10章 高级事件(下)

onestopweb

事件

index.html

<!DOCTYPE html PUBLIC "-//W3C//DTD XHTML 1.0 Transitional//EN" "http://www.w3.org/TR/xhtml1/DTD/xhtml1-transitional.dtd">

<html xmlns="http://www.w3.org/

- 孙子兵法

roadrunners

孙子兵法

始计第一

孙子曰:

兵者,国之大事,死生之地,存亡之道,不可不察也。

故经之以五事,校之以计,而索其情:一曰道,二曰天,三曰地,四曰将,五

曰法。道者,令民于上同意,可与之死,可与之生,而不危也;天者,阴阳、寒暑

、时制也;地者,远近、险易、广狭、死生也;将者,智、信、仁、勇、严也;法

者,曲制、官道、主用也。凡此五者,将莫不闻,知之者胜,不知之者不胜。故校

之以计,而索其情,曰

- MySQL双向复制

tomcat_oracle

mysql

本文包括:

主机配置

从机配置

建立主-从复制

建立双向复制

背景

按照以下简单的步骤:

参考一下:

在机器A配置主机(192.168.1.30)

在机器B配置从机(192.168.1.29)

我们可以使用下面的步骤来实现这一点

步骤1:机器A设置主机

在主机中打开配置文件 ,

- zoj 3822 Domination(dp)

阿尔萨斯

Mina

题目链接:zoj 3822 Domination

题目大意:给定一个N∗M的棋盘,每次任选一个位置放置一枚棋子,直到每行每列上都至少有一枚棋子,问放置棋子个数的期望。

解题思路:大白书上概率那一张有一道类似的题目,但是因为时间比较久了,还是稍微想了一下。dp[i][j][k]表示i行j列上均有至少一枚棋子,并且消耗k步的概率(k≤i∗j),因为放置在i+1~n上等价与放在i+1行上,同理

![]()