if-else:if判断语句和执行语句之间相差1个时钟周期吗?并行执行吗?有优先级吗?

一、是否慢一个时钟周期?

1.1 慢一个时钟周期

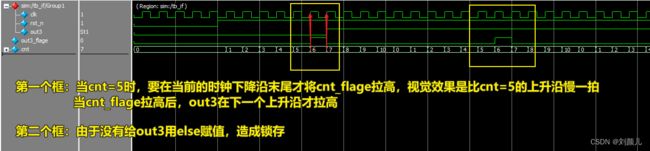

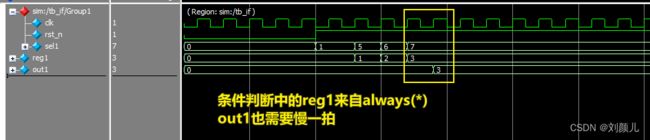

如果条件判断中的语句的值也是 通过always赋值得到的,那么执行语句要比条件判断慢一拍

即使条件判断中的值是来自组合逻辑always(*),也需要慢一拍

1.1.1 时序逻辑的always

module if_top (

input clk,

input rst_n,

input sel,

output reg out1,

output reg out2,

output reg out3

);

reg [3:0] cnt;

reg out3_flage;

always @(posedge clk or negedge rst_n) begin

if(!rst_n)

cnt <= 4'd0;

else if(cnt == 4'd10)

cnt <= 4'd0;

else

cnt <= cnt + 4'd1;

end

always @(posedge clk or negedge rst_n) begin

if(!rst_n)

out3_flage <= 1'd0;

else if(cnt == 4'd5)

out3_flage <= 1'd1;

else

out3_flage <= 1'd0;

end

always @(posedge clk or negedge rst_n) begin

if(!rst_n)

out2 <= 1'd0;

else if(cnt == 4'd5)

out2 <= 1'd1;

end

always @(posedge clk or negedge rst_n) begin

if(!rst_n)

out3 <= 1'd0;

else if(out3_flage)

out3 <= 1'd1;

end

endmodule

1.1.2 组合逻辑的always

module if_top (

input clk,

input rst_n,

input [3:0]sel1,

output reg [2:0] out1

);

reg [4:0] reg1;

always @(posedge clk or negedge rst_n) begin

if(!rst_n)

out1 <= 3'd0;

else if(reg1 == 3'd3)

out1 <= 3'd3;

else

out1 <= 3'd0;

end

always @(*) begin

case(sel1)

4'd5: reg1 <= 3'd1;

4'd6: reg1 <= 3'd2;

4'd7: reg1 <= 3'd3;

default:reg1 <= 3'd0;

endcase

end

endmodule

1.2 不需要慢一个时钟周期

当if的条件条件语句不是通过always赋值得到的,那么执行语句就不需要比判断语句慢一个时钟周期

module if_top (

input clk,

input rst_n,

input in1,

input sel,

output reg out1

);

always @(posedge clk or negedge rst_n) begin

if(!rst_n)

out1 <= 1'd0;

else if(sel)

out1 <= in1;

end

endmodule

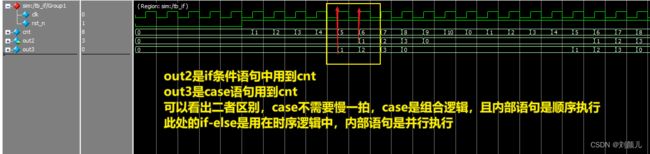

二、并行执行吗?

设计文件中,各个always模块直接是并行执行的

但是always内部是否是并行的,组合逻辑和时序逻辑的情况是不同的

2.1 组合逻辑

always内部顺序执行

always @(*) begin

case(cnt)

4'd5: out3 <= 3'd1;

4'd6: out3 <= 3'd2;

4'd7: out3 <= 3'd3;

default:out3 <= 3'd0;

endcase

end

2.2 时序逻辑

always内部并行执行,并且if-else之间有优先级

module if_top (

input clk,

input rst_n,

input [1:0]sel,

output reg [2:0] out1,

output reg [2:0] out2,

output reg [2:0] out3

);

reg [3:0] cnt;

always @(*) begin

if(sel == 3'd1)

out1 = 3'd1;

else if(sel == 3'd2)

out1 = 3'd2;

else if(sel == 3'd3)

out1 = 3'd3;

else

out1 = 3'd0;

end

always @(posedge clk or negedge rst_n) begin

if(!rst_n)

cnt <= 4'd0;

else if(cnt == 4'd10)

cnt <= 4'd0;

else

cnt <= cnt + 4'd1;

end

always @(posedge clk or negedge rst_n) begin

if(!rst_n)

out2 <= 3'd0;

else if(cnt == 4'd5)

out2 <= 3'd1;

else if(cnt == 4'd6)

out2 <= 3'd2;

else if(cnt == 4'd7)

out2 <= 3'd3;

else

out2 <= 3'd0;

end

always @(*) begin

case(cnt)

4'd5: out3 <= 3'd1;

4'd6: out3 <= 3'd2;

4'd7: out3 <= 3'd3;

default:out3 <= 3'd0;

endcase

end

endmodule

always @(posedge clk or negedge rst_n) begin

if(!rst_n)

out2 <= 3'd0;

else if(cnt == 4'd5)

out2 <= 3'd1;

else if(cnt == 4'd1)//测试优先级!!!!!!!!!!!

out2 <= 3'd2;

else if(cnt == 4'd7)

out2 <= 3'd3;

else

out2 <= 3'd0;

end

三、存在优先级吗?

下面的情况存在优先级

module if_top (

input clk,

input rst_n,

input sel1,

input sel2,

input sel3,

output reg [2:0] out1

);

always @(posedge clk or negedge rst_n) begin

if(!rst_n)

out1 <= 3'd0;

else if(sel1)

out1 <= 3'd1;

else if(sel2)

out1 <= 3'd2;

else if(sel3)

out1 <= 3'd3;

else

out1 <= 3'd0;

end

endmodule