综合方法论

版权声明:转载时请以超链接形式标明文章原始出处和作者信息及本声明

http://bb2hh.blogbus.com/logs/43953273.html

从一高手那里学来的:)

ic中综合的基本要求就是设置各种外部环境,让工具综合出符合这种环境的网表。但是这种方法有些不好的地方,因为外部环境比较复杂,不能设置的100%符合要求。

所以有如下和后端紧密接合的方法,当然现在cadence以及synopsys都在推新工具(soce,icc),这些新工具的方法也和下面类似。

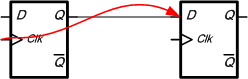

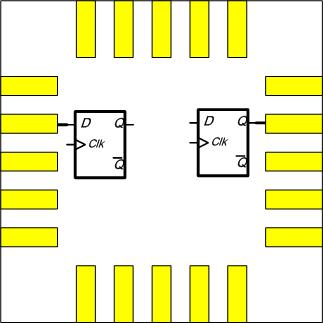

首先,根据synopsys推荐的代码风格,或者行业默认的风格,对最顶层的输入输出寄存2拍。当然有些不能这样处理:)即如下:

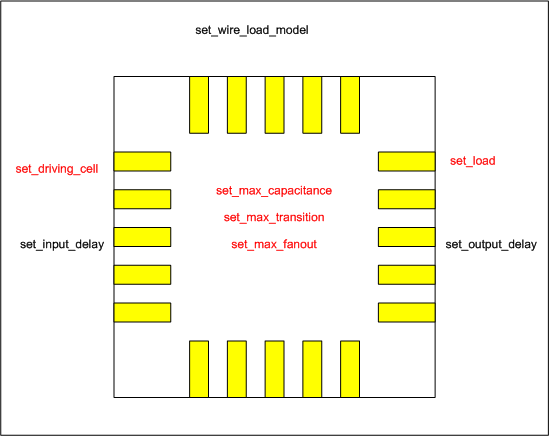

2.对传统的环境约束设置,不再设置wire_load_model,input_delay,output_delay,仅声明系统中的所有时钟,

包括generated clock,选择时钟,以及multiple clock ,以及各种clock之间的false path,multicycle path。当然drive,load,以及drc要设置一些。 wire_load可以设置成top。wire_load_model可以pr后create,或者让工具自己选择。

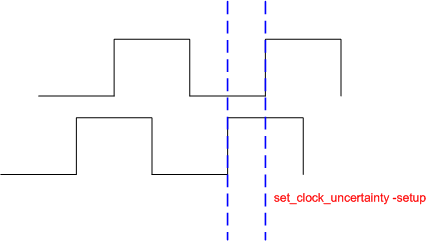

3.一点点增大clock的margin,即clock 的setup uncertainty。

第二步的基本思想就是让工具按照理想状况区约束reg2reg的路径。第三步的思想是尽可能让reg2reg的路径最小,使用任何约束方法比如retiming,boundary optimize, ungroup, group, critical range ,weight, cost priorty,等等。

4,综合到理想的时序后,开始加入input_delay output_delay,写出sdc文件。

这个可以不需要再次compile,只需要分析下时序是否满足,以及port的端口是否约束完整。

当然这里如果需要也可以设置一些false path。

不过如果输入输出通过pad没有寄存2拍的话,可以增量编译一次。以优化input2reg,reg2output的组合逻辑。

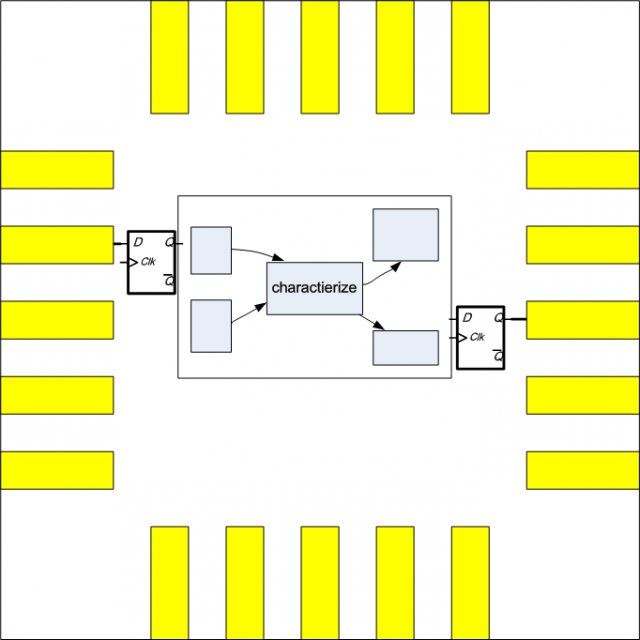

5.当然时序如果不理想,即reg2reg的时序不是很理想可以,可以使用characterize来例化该模块的周围环境,然后细节性的优化该模块。更形象的说法叫,勒紧袋子,再揣2脚。

6.后端布局的时候,需要经输入的第一级寄存器,以及输出的寄存器放置在对应pad的周围。并固定。

7,pr后提取网表,以及相关参数后,进一步约束周围环境,即input_delay,output_delay,甚至源同步的相关约束。并分析。

ps:这种方法的前提是好的代码风格,即顶层的输入输出信号都寄存了至少2拍。这个主要是当你把输入的第一级

寄存器或者输出的最后一级寄存器约束在端口附近的时候。第二级或者第三级。。依次类推,可以方便的

放置版图的位置中,优化时序,这个主要是2个单纯的寄存器之间至少有1个时钟周期用来布线。所以寄存几拍

对后端来说很乐观。如果后端是使用hierarchy pr的话。最后模块主要模块之间也这样做。

下面就从AC,DC方面固定寄存器位置。

1.AC,所谓AC就是根据外部条件了。一般来说外部条件就是接口了。这里我一般采用862原则:)(只是dc综合的时候使用,sta要修改约束)

8:输入延迟最大为时钟周期的80%

6:输出延迟的最大延迟为周期的60%

2:输出延迟最小延迟为周期的20%

那么输入的最小延迟呢?设置个0.1或者0就够了,这样都满足,其他情况都可以满足了。

当然别忘记设置clock的margin

比如时钟周期为8ns

set_input_delay -max [expr 8*0.6] -clock CLK PI (ps:好像6x4是敏感字,哎,只好用表达式)

set_input_delay -min 0.1 -clock CLK PI

set_output_delay -max 4.8 -clock CLK PO

set_output_delay -min -1.6 -clock CLK PO

当然这是一般情况,特殊情况需特殊对待,比如有的外围芯片要求比较高的情况,或者上下双边沿的情况。

甚至可以更严格些:)

这样的话,后端读入sdc之后,第一级寄存器就不会放的太远。

2.DC,所谓DC就是芯片自己内部的延迟。

可以通过set_min_delay ,set_max_delay设置。其实也是约束pad到内部第一个寄存器之间的延迟。

我一般采用时序路径使用AC,非时序路径使用DC。

如果pr也是一个人做同时熟悉外围器件时序,后端pr的时候,如果布线紧张,也是稍稍改动sdc。

PS:另外的一种约束也挺好,就是根据外围器件的要求,设置约束。这样约束也有好处就是从dc到pr到sta约束改动不大。