HDLbits 刷题答案 3.2.1 Latches and Flip-Flops

3.2.1 Latches and Flip-Flops

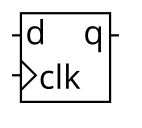

3.2.1.1 D flip-flop

module top_module (

input clk, // Clocks are used in sequential circuits

input d,

output reg q );//

// Use a clocked always block

// copy d to q at every positive edge of clk

// Clocked always blocks should use non-blocking assignments

always @ (posedge clk)

q <= d;

endmodule

3.2.1.2 D flip-flops

创建一个8-bit的D-触发器,时钟上升沿有效

module top_module (

input clk,

input [7:0] d,

output [7:0] q

);

always @ (posedge clk)

q <= d;

endmodule

3.2.1.3 DFF with reset

创建一个同步复位的8-bit D-触发器

module top_module (

input clk,

input reset, // Synchronous reset

input [7:0] d,

output [7:0] q

);

always @ (posedge clk) begin

if(reset)

q <= 8'b0;

else

q <= d;

end

endmodule

3.2.1.4 DFF with reset value

创建一个同步复位的8-bit D-触发器,复位时输出为0x34

module top_module (

input clk,

input reset,

input [7:0] d,

output [7:0] q

);

always @ (negedge clk) begin

if(reset)

q <= 8'h34;

else

q <= d;

end

endmodule

3.2.1.5 DFF with asynchronous reset

创建一个异步复位的8-bit D-触发器

将异步复位信号加入敏感事件表,当异步复位信号发生改变,依旧可以触发always语句块

module top_module (

input clk,

input areset, // active high asynchronous reset

input [7:0] d,

output [7:0] q

);

always @ (posedge clk or posedge areset) begin

if(areset)

q <= 8'b0;

else

q <= d;

end

endmodule

3.2.1.6 DFF with byte enable

创建一个16-bit的D-触发器,byteena[1]控制高8位,byteena[0]控制低8位

module top_module (

input clk,

input resetn,

input [1:0] byteena,

input [15:0] d,

output [15:0] q

);

always @ (posedge clk) begin

if (!resetn)

q <= 16'b0;

else begin

if (byteena[1])

q[15:8] <= d[15:8];

if (byteena[0])

q[7:0] <= d[7:0];

end

/*else if (byteena[1] || byteean [0]) begin

if (byteena[1])

q[15:8] <= d[15:8];

if (byteana[0])

q[7:0] <= d[7:0];

end*/

end

endmodule

3.2.1.7 D Latch

- 没有clk端口,取而代之是一个ena端口,这是一个锁存器

- 相比与触发器,这个锁存器是电平触发

module top_module (

input d,

input ena,

output reg q);

always @ (*) begin

if(ena) begin

q <= d;

end

end

endmodule

3.2.1.8 DFF

- 在敏感时间表中,不同同时出现边沿触发条件和电平触发条件

- 一般下降沿触发,会在名字后边加n,如下降沿复位 rstn

module top_module (

input clk,

input d,

input ar, // asynchronous reset

output q);

always @ (posedge clk or posedge ar) begin

if (ar) begin

q <= 0;

end

else begin

q <= d;

end

end

endmodule

3.2.1.9 DFF

同步复位端,不需要在敏感时间表中进行声明

module top_module (

input clk,

input d,

input r, // synchronous reset

output q);

always @ (posedge clk) begin

if (r) begin

q <= 0;

end

else begin

q <= d;

end

end

endmodule

3.2.1.10 DFF+gate

实现该电路

图中有一个 D 触发器与一个异或门,触发器的输出 q 和输入信号 in 一起作为异或门的输入。异或门的输入作为触发器的输入 d

module top_module (

input clk,

input in,

output out);

always @ (posedge clk) begin

out <= out ^ in;

end

endmodule

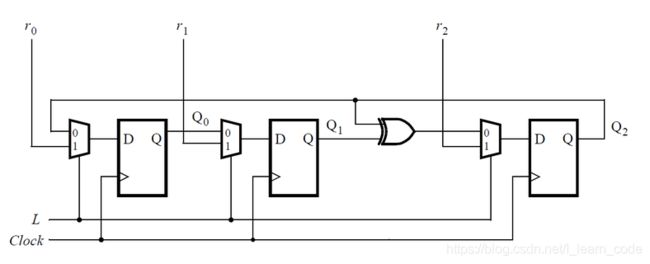

3.2.1.11 MUX and DFF

module top_module (

input clk,

input L,

input r_in,

input q_in,

output reg Q);

wire tmp;

assign tmp = L ? r_in : q_in;

always @ (posedge clk) begin

Q <= tmp;

end

endmodule