FPGA时序分析

FPGA时序部分不管是笔试还是面试都太容易被考察到了,把这部分的知识点进行汇总!

目录

时钟基本概念

时钟源

门控时钟

时钟延迟

时钟偏移(skew)

时钟抖动(jitter)

时序分析

什么是时序分析?

时序路径三要素

时序分析基本概念

上升沿&下降沿

建立时间&保持时间

clock arrive time

data arrive time

data required time

slack

时钟基本概念

时钟源

根据时钟源在数字设计模块中位置的不同,可以将时钟源分为外部时钟源和内部时钟源。

外部时钟源

RC/LC 振荡电路:利用正反馈或负反馈电路产生周期性变化时钟信号。此类时钟源电路简单,频率变化范围大,但工作频率较低,稳定度不高。

无源/有源晶体振荡器:利用石英晶体的压电效应(压力和电信号可以相互转换)产生谐振信号。此类时钟源频率精度高,稳定性好,噪声低,温漂小。有源晶振中,往往还加入了压控或温度补偿,时钟的相位和频率都有较好的特性。但电路实现相对复杂,频带较窄,频率基本不能调节。

调试特定电路时,往往也会使用一些搭建的特定电路(例如施密特触发器)或信号发生器设备产生的时钟源。

内部时钟源

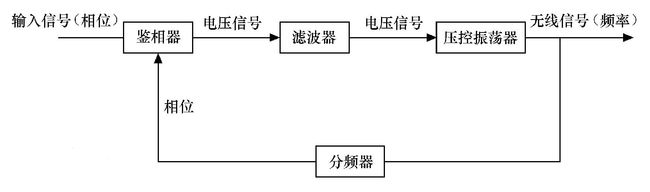

锁相环(PLL, Phase Locked Loop):利用外部输入的参考信号控制环路内部振荡信号的频率和相位,实现输出信号频率对输入信号频率的自动跟踪,通过反馈通路将信号倍频到一个较高的固定频率。

一般晶振由于工艺与成本原因,做不到很高的频率,利用 PLL 电路就可以实现稳定且高频的时钟。PLL 集成到设计模块的内部,可以保证数字电路具有较好的延迟和稳定性。

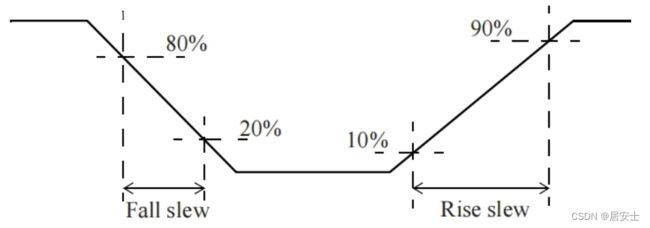

在静态时序分析(STA)中,一个上升或者下降的波形通常用slew rate来表征其跳变的快与慢。Transition time就是用来记录这个信号在两个电平之间的转换时间。这里需要注意的是,transition time实际是slew rate的倒数。Transition time如果越大,那么slew rate就会越慢,反之亦然。

为了能量化这样的波形,我们近似采用一个线性上升或者下降的信号来模拟真实信号波形。这个线性区域的起点和终点,可能因为某些估算模型而有所不同。在STA中,我们有时候会采用比较宽松的约束模式,例如20%/80%、10%/90%。当然,我们也可以采用激进一些的模式,如30%/70%。

门控时钟

如右图,产生了一个尖峰,因此我们尽量不要对时钟做运算,不要采用门控时钟

时钟延迟

时钟延迟包括源延迟、布线网络延迟、输入输出延迟

源延迟:时钟信号从实际时钟原点到第一级寄存器交汇点的传输时间

布线网络延迟:是从设计模块时钟定义点到模块内触发器时钟端的传输时间,传输路径上可能经过缓冲器(buffer)

输入输出延迟:第一级寄存器交汇点到第一级寄存器的传输时间

时钟偏移(skew)

由于线网的延迟,时钟信号在到达触发器端口时,不能保证不同触发器端口的时钟沿是对齐的,即不同触发器端口的时钟相位存在差异。这种差异称为时钟偏移。示意图如下:

一般时钟偏移与时钟频率没有直接的关系,与走线长度、负载电容、负载数量等因素有关。

同一个时钟信号到达两个不同寄存器之间的时间差值,时钟偏斜永远存在,到一定程度就会严重影响电路的时序

时钟抖动(jitter)

相对于理想时钟沿,实际时钟中存在的不随时间积累的、时而超前、时而滞后的偏移称为时钟抖动。可以用抖动频率和抖动幅度对时钟抖动进行定量描述。数字设计中,时钟抖动都是用时间来描述,示意图如下。

时钟抖动可分为随机抖动和固定抖动。随机抖动的来源为热噪声、半导体工艺等。固定抖动的来源为开关电源、电磁干扰或其他不合理的布局布线等。

所谓抖动(jitter),就是指两个时钟周期之间存在的差值,这个误差是在时 钟发生器内部产生的,和晶振或者 PLL 内部电路有关,布线对其没有影响

时序分析

什么是时序分析?

时序分析本质上就是一种时序检查,目的是检查设计中所有的 D 触发器是否能够正常 工作,也就是检查 D 触发器的同步端口(数据输入端口)的变化是否满足建立时间要求 (Setup)和保持时间要求(Hold);检查 D 触发器的异步端口(异步复位端口)的变化 是否满足恢复时间要求(Recovery)和移除时间要求(Removal)。

时序分析包括静态时序分析(STA)和动态时序分析。

动态时序分析:将布局布线生成的布线延迟信息反标注到门级网表中进行仿真,检查是 否存在时序违例。此时的仿真包括门延迟和布线延迟信息,能够较好反应芯片的实际工作情 况。因为不可能产生完备的测试向量,覆盖门级网表中的每一条路径。因此在动态时序分析 中,无法暴露一些路径上可能存在的时序问题。

静态时序分析:采用穷尽分析方法来提取出整个电路存在的所有时序路径,计算信号在 这些路径上的传播延时,检查信号的建立和保持时间是否满足时序要求,通过对最大路径延 时和最小路径延时的分析,找出违背时序约束的错误。它不需要输入向量就能穷尽所有的路 径,且运行速度很快、占用内存较少,不仅可以对芯片设计进行全面的时序功能检查,而且 还可利用时序分析的结果来优化设计,因此静态时序分析已经越来越多地被用到数字集成电 路设计的验证中。

时序路径三要素

源时钟路径:从源时钟的源节点(通常是 FPGA 的时钟输入引脚)到源寄存器的时钟 端口的路径。当时序路径的起点是 FPGA 输入端口时,该时序路径是没有源时钟路径的。

数据路径:从时序路径的起点到时序路径的终点之间的数据传播路径。时序路径的起点 可以是源寄存器的时钟端口或 FPGA 的输入端口,时序路径的终点可以是目的寄存器的输 入端口或 FPGA 的输出端口。

目的时钟路径:从目的时钟的源节点(通常是 FPGA 的时钟输入引脚)到目的寄存器 的时钟端口的路径。当时序路径的终点是 FPGA 的输出端口时,该时序路径是没有目的时 钟路径的。

时序分析基本概念

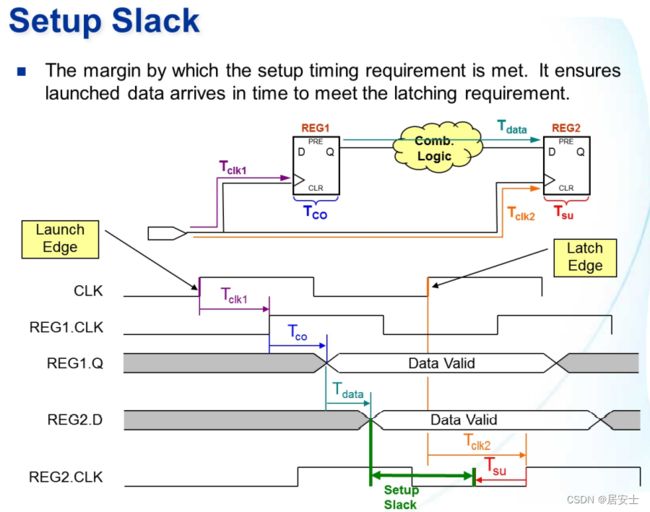

同步逻辑时序模型 如上图所示,T = tCO+tDELAY+tSU。时钟周期大于 T,触发器正常工 作;时钟周期小于 T,不满足建立时间,触发器可能经历亚稳态。

上升沿&下降沿

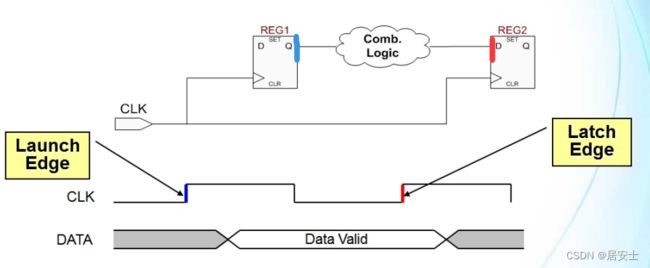

1)Launch Edge:前级寄存器发送数据对应的时钟沿,是时序分析的起 点。

2)Latch Edge:后级寄存器捕获数据对应的时钟沿,是时序分析的终点

建立时间&保持时间

建立时间Tsetup:在信号采样沿之前,数据要保持稳定的时间

保持时间Thold: 在信号采样沿之后,数据要保持稳定的时间

clock arrive time

时钟到达时间:(clock arrive time)从时钟输出源到目的端寄存器的时钟输入管脚

data arrive time

数据到达时间:(data arrive time)从launch edge开始到第二级寄存器输入的时间

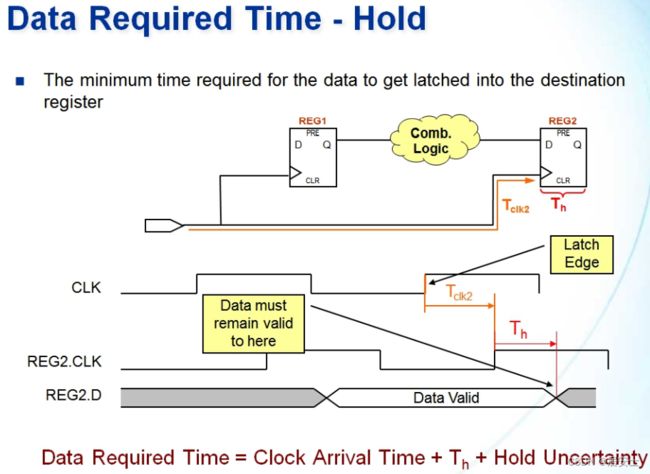

data required time

寄存器数据对到达的时间的要求

数据要求时间setup:Tclk2-Tsu

数据要求时间shold:Tclk2+Th

Tclk2-Tsu<寄存器数据保持稳定 Setup Slack =data required time – data arrival time =(Tclk2-Tsu)—(launch edge+Tclk1+Tco+Tdata) 举个例子: T=10ns Tclk1=1ns Tco =0.2ns Tdata =2ns Tclk2=2ns Tsu=0.5 Slack=? Data required time=clock arrival time – Tsu= 12-0.5=11.5ns Data arriaval time= lauch edge +Tclk1+tco+tdata =0+1+0.2+2 =3.2ns Slack =data required time – data arrival time =11.5-3.2 =8.3n 时间余量有正有负,为负值时,不满足要求 hold Slack = data arrival time –data required time =( next lauch edge +Tclk1+Tco+Tdata)—(Tclk2-Tsu) 举个例子: T=10ns Tclk1=1ns Tco =0.2ns Tdata =2ns Tclk2=2ns Tsu=0.5ns Thold =0.1ns hold Slack=? Data arriaval time= lauch edge +Tclk1+tco+tdata =10+1+0.2+2 =13.2ns(下一个数据 的到达时间) Data required time=clock arrival time +Thold = 12+0.1=12.1ns Slack =data required time – data arrival time=13.2-12.1=1.1nsslack