嵌入式分享合集44

从来不做语言的奴隶, 没想到程序员行业也怎么多喜欢拍马屁的,还是那句话 就用最合适的,难道我会java go c py 我就要左右手脚互搏吗好无聊 还是说说嵌入式哦

一、三极管的应用电路

三极管有三个工作状态:截止、放大、饱和,放大状态很有学问也很复杂,多用于集成芯片,比如运放,现在不讨论。whaosoft aiot http://143ai.com

其实,对信号的放大我们通常用运放处理。三极管更多的是当做一个开关管来使用,且只有截止、饱和两个状态。

截止状态看作是关,饱和状态看作是开。

Ib≥1mA时,完全可以保证三极管工作在饱和状态,对于小功率的三极管此时Ic为几十到几百mA,驱动继电器、蜂鸣器等功率器件绰绰有余。

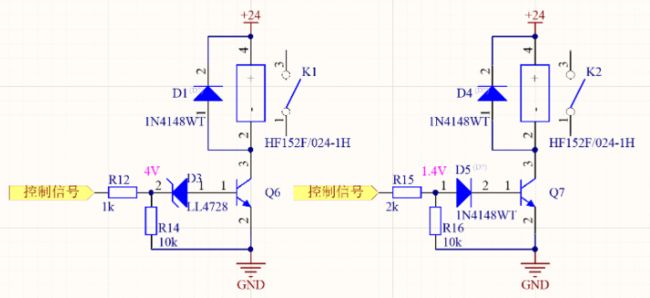

三极管电路举例

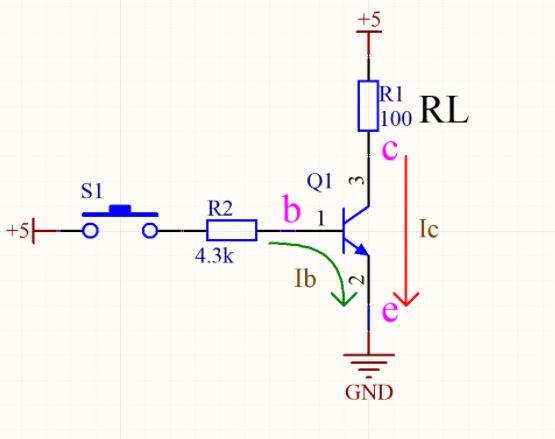

把三极管箭头理解成一个开关,如下图为NPN型三极管,按下开关S1,约1mA的Ib流过箭头,三极管工作在饱和状态,c极到e极完全导通,c极电平接近0V(GND),负载RL两端压降接近5V。

Ib与Ic电流都流入e极,根据电流方向,e极为低电平,应接地,c极接负载和电源。

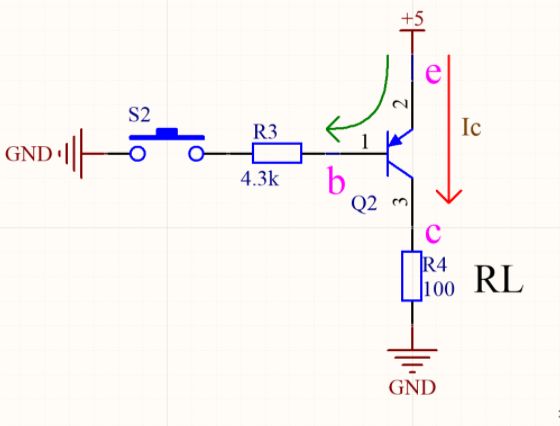

如下图为PNP型三极管,按下开关S2,约1mA的Ib流过箭头,三极管工作在饱和状态,e极到c极完全导通,c极电平接近5V,负载RL两端压降接近5V。

Ib与Ic电流都流出e极,根据电流方向,e极为高电平,应接电源,c极接负载和地。

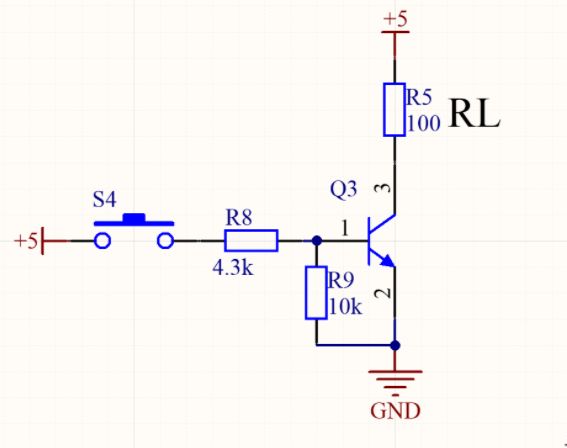

如下图NPN三极管,对于NPN三极管更应该在b极加一个下拉电阻,一是为了保证b、e极间电容加速放电,加快三极管截止;二是为了保证给三极管b极一个已知逻辑状态,防止控制输入端悬空或高阻态时对三极管工作状态的不确定,相关文章推荐:通俗理解STM32中的上/下拉电阻。

如下图是PNP三极端,对于PNP三极管,更应该在b极加一个上拉电阻,原理同上。

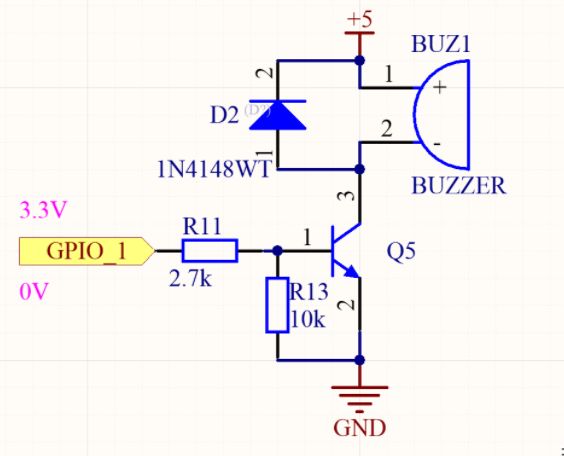

下图NPN三极管,对于感性负载,必须在负载两端并联一个反向续流二极管,因为三极管在关断时,线圈会自感产生很高的反向电动势,而续流二极管提供的续流通路,同时钳位反向电动势,防止击穿三极管。

续流二极管的选型必须是快恢复二极管或肖特基二极管,两者响应速度快。

如下图的NPN三极管,对于某些控制信号为低电平时,可能并不是真正的0V,一般在1V以内,为保证三极管完全截止,不得不在三极管b极加一个反向稳压管或正向二极管,以提高三极管导通的阈值电压。

根据个人经验,推挽输出的数字信号不用加,OC输出、二极管输出以及延时控制有必要加,通常稳压管正常的工作电流≥1mA。

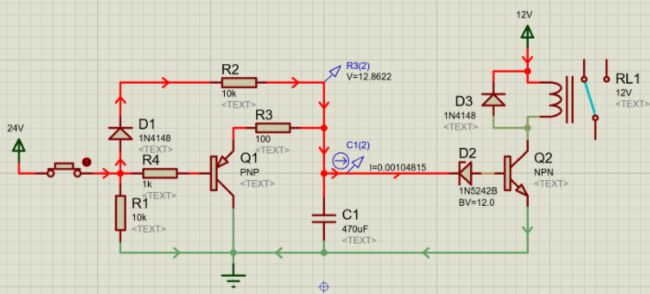

下图是用三极管实现继电器的延时控制的例子。

为三极管延时导通,快速关断的一个仿真电路,D1、R2、C1、D2构成延时导通Q2的回路,C1的电压为12V的时候Q2导通,R3、Q1、R4、R1构成快速关断Q2的回路,C1通过R3和Q1快速放电。

要点

-

对于NPN三极管,在不考虑三极管的情况下,b极电阻与下拉电阻的分压必须大于0.7V,PNP同理。

-

b极电流必须≥1mA可保证三极管处于饱和状态,此时Ic满足三极管最大的驱动能力。

-

另外,对于三极管的放大倍数β,指的是输出电流的驱动能力放大了β,比如100倍,并不是把输出电流真正的放大了100倍。

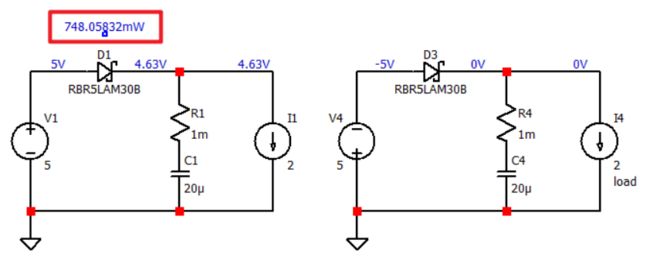

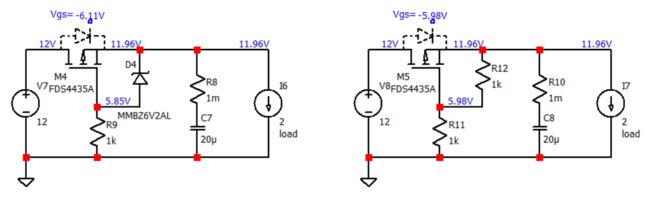

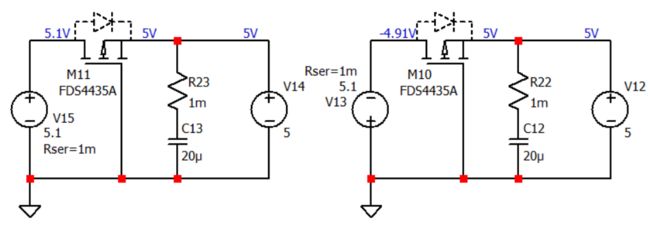

二、电源防反接电路,基于二极管、MOS管

二极管串联

以常用的5V/2A为例。常用二极管串联在电路中,在电源反接时,二极管承担所有的电压,有效防止电源反接损坏后级设备。但是,二极管上压降较大,损耗较高。使用肖特基二极管可以减小损耗,但是仍对电路有较大影响,特别是在电源电压更低的情况下。

反并二极管+保险丝

使用反并二极管+保险丝,正常运行时基本没有损耗。在电源反接时,电源侧接近短路,保险丝熔断,从而实现保护。反接发生后,二极管和保险丝一般都需要更换。并且,输入反接时产生一个负压,后级设备还是有可能损坏。

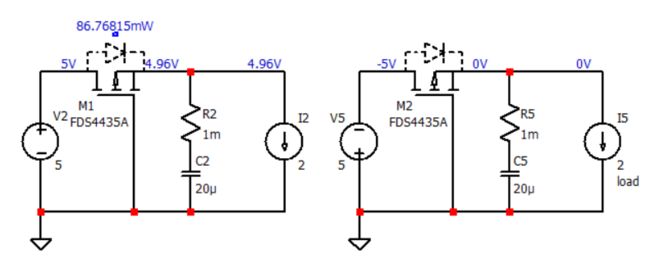

PMOS防反接电路

基本电路

基本的PMOS防反接电路,利用PMOS的寄生二极管:

电源正接,寄生二极管导通,S极电压升高,V G S ≈ − V i n ,从而PMOS开启,一般导通电阻在数十mΩ,导通损耗远低于二极管。

电源反接,寄生二极管截止,V G S = 0 V,PMOS关断,后级设备电压为0。

添加稳压管

如果使用PMOS的Vgs耐压低于电源电压,可以使用稳压管限制Vgs。或者在输入电压基本不变的情况下,也可以使用电阻分压。

注意

1、PMOS需要选择合适的Vds、Vgs耐压,选择低Rds的型号可以减小损耗;

2、注意PMOS上的功耗和散热;

3、因为PMOS开启后电流可双向流动,这个电路的负载不能是电池等电压源。否则,如下右图,因为负载电池有5V电压,V G S = − 5 V V_{GS}=-5V,实际上PMOS还是开启了,输入反接还是会导致过流。

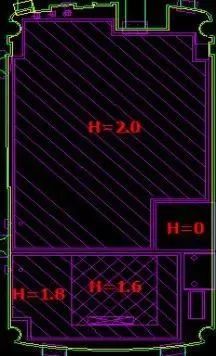

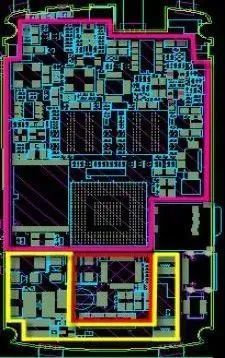

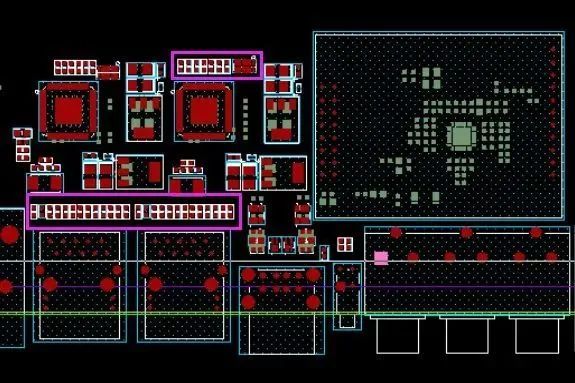

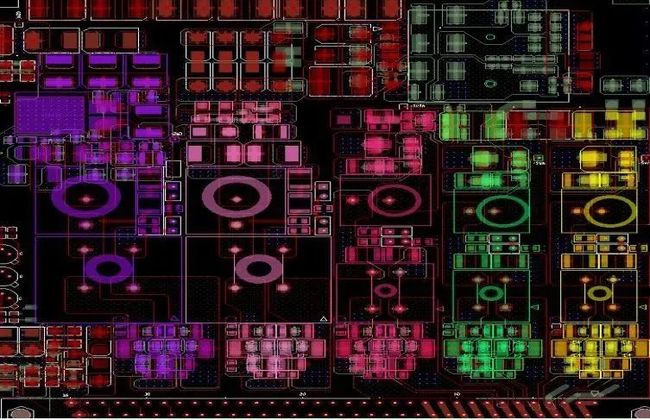

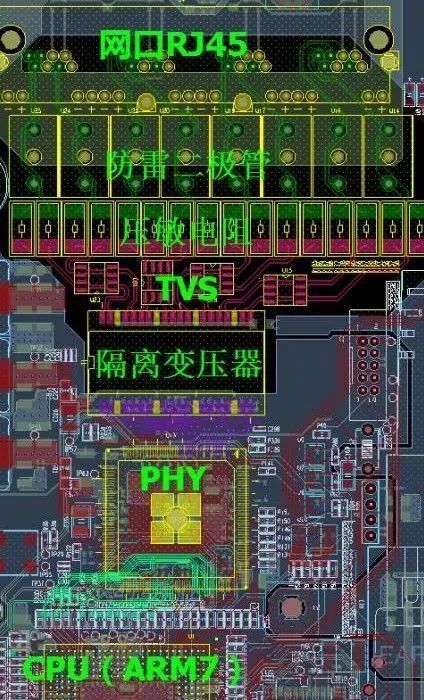

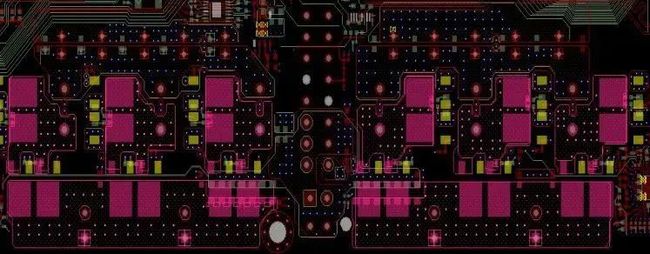

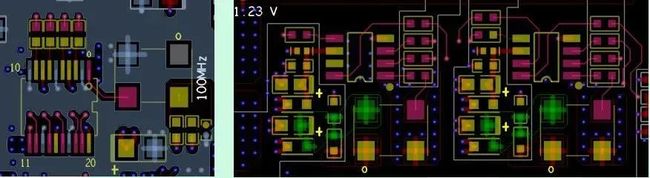

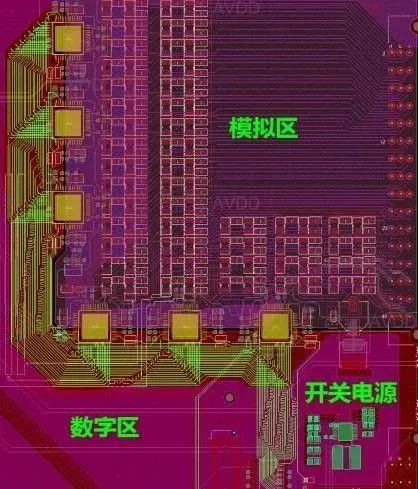

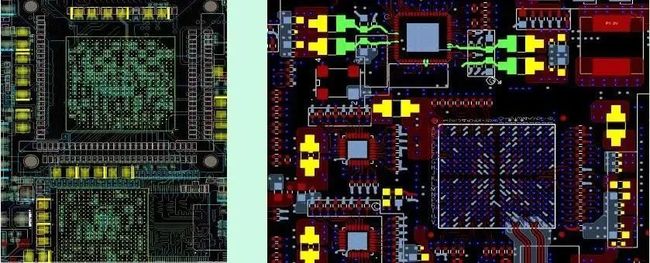

三、PCB布局思路分析

分析好整个电路原理以后,就可以开始对整个电路进行布局布线,下面,给大家介绍一下布局的思路和原则。

1、首先,我们会对结构有要求的器件进行摆放,摆放的时候根据导入的结构,连接器得注意1脚的摆放位置。

2、布局时要注意结构中的限高要求。

3、 如果要布局美观,一般按元件外框或者中线坐标来定位(居中对齐)。

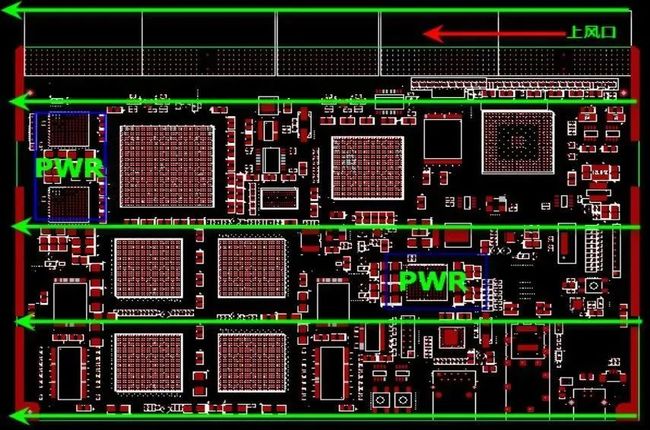

4、 整体布局要考虑散热。

5、 布局的时候需要考虑好布线通道评估、考虑好等长需要的空间。

6、 布局时需要考虑好电源流向,评估好电源通道。

7、 高速、中速、低速电路要分开。

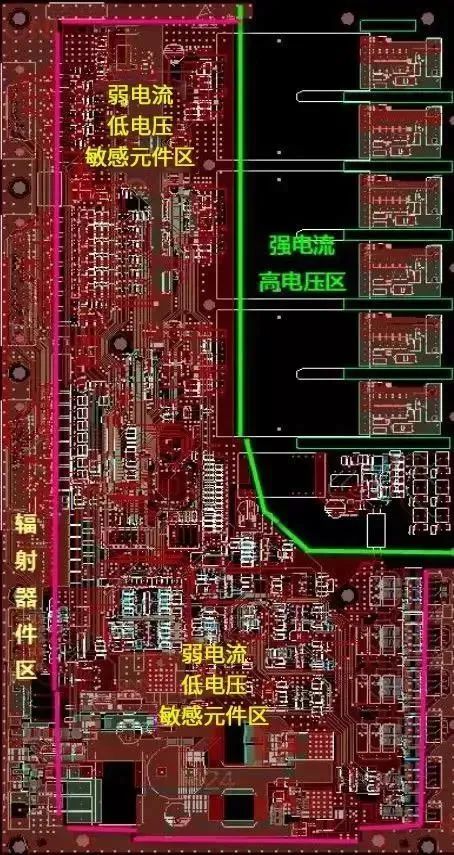

8、强电流、高电压、强辐射元器件远离弱电流、低电压、敏感元器件。

9、 模拟、数字、电源、保护电路要分开。

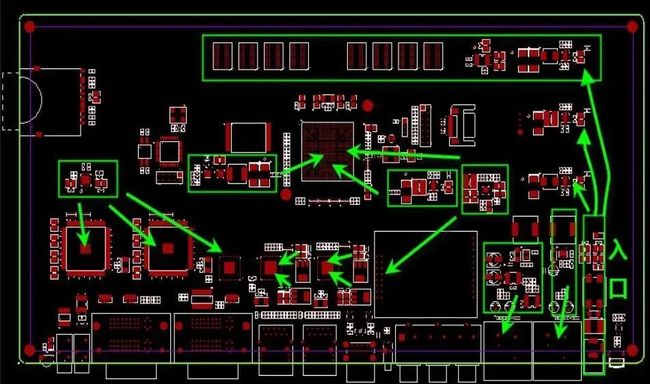

10、 接口保护器件应尽量靠近接口放置。

11、 接口保护器件摆放顺序要求:(1)一般电源防雷保护器件的顺序是:压敏电阻、保险丝、抑制二极管、EMI滤波器、电感或者共模电感,对于原理图 缺失上面任意器件顺延布局;(2)一般对接口信号的保护器件的顺序是:ESD(TVS管)、隔离变压器、共模电感、电容、电阻,对于原理图缺失上面任意器件顺延布局;严格按照原理图的顺序(要有判断原理图是否正确的能力)进行“一字型”布局。

12、电平变换芯片(如RS232)靠近连接器(如串口)放置。

13、 易受ESD干扰的器件,如NMOS、 CMOS器件等,尽量远离易受ESD干扰的区域(如单板的边缘区域)。

14、 时钟器件布局:(1)晶体、晶振和时钟分配器与相关的IC器件要尽量靠近;(2)时钟电路的滤波器(尽量采用“∏”型滤波)要靠近时钟 电路的电源输入管脚;(3)晶振和时钟分配器的输出是否串接一个22欧姆的电阻;(4)时钟分配器没用的输出管脚是否通过电阻接地;(5)晶体、晶振和时钟分配器的布局要注意远离大功率的元器件、散热器等发热的器件;(6)晶振距离板边和接口器件是否大于1inch。

15、开关电源是否远离AD\DA转换器、模拟器件、敏感器件、时钟器件。

16、开关电源布局要紧凑,输入\输出要分开, 严格按照原理图的要求进行布局,不要将开关电源的电容随意放置。

17、 电容和滤波器件 :(1)电容务必要靠近电源管脚放置,而且容值越小的电容要越靠近电源管脚;(2)EMI滤波器要靠近芯片电源的输入口;(3)原则上每个电源管脚一个0.1uf的小电容、一个集成电路一个或多个10uf大电容,可以根据具体情况进行增减;