【流水线】FPGA中流水线的原因和方法

目录

写在前面

什么是流水线?

无流水线设计

流水线设计

流水线的后果

结论

写在前面

对 FPGA(现场可编程门阵列)进行编程是一个定制其资源以实现确定逻辑功能的过程。这涉及使用FPGA的基本构建模块(如可编程逻辑模块(CLB)、专用多路复用器等)对程序指令进行建模,以满足数字系统的要求。

在设计过程中,需要考虑的一个重要标准是系统固有的时序问题,以及用户制定的任何约束。可以帮助设计人员实现这一目标的一种设计机制是流水线。

什么是流水线?

流水线是一个能够并行执行程序指令的过程。您可以在下面看到流水线处理器体系结构的可视化表示形式。

上图流水线处理器体系结构的可视表示形式。每个方块对应一条指令。正方形使用不同的颜色传达了这样一个事实,即指令是相互独立的。

在FPGA中,这是通过以特定方式排列多个数据处理模块来实现的。为此,我们首先将整个逻辑电路分成几个小部分,然后使用寄存器(触发器)将它们分开。

让我们通过考虑一个示例来分析FPGA设计流水线的模式。

示例

让我们看一个由三个乘法组成的系统,然后在四个输入数组上进行一次加法。我们的输出y我因此将等于(ai × bi × ci) + di。

无流水线设计

创建这样一个系统时想到的第一个设计是乘法器,然后是一个加法器,如图2a所示。

上图为非流水线 FPGA 设计示例

在这里,我们期望操作的顺序是一个我和b我 乘数 M 的数据1,然后是其乘积Ci乘数 M2最后,将所得产物与di通过加法器 A1.

然而,当系统被设计为同步时,在第一个时钟周期,只有乘法器M1才能在其输出端产生有效数据(a1×b1).这是因为,此时此刻,只有M1具有有效数据 (a1和b1) 在其输入引脚处,与 M 不同2和 A1.

在第二个时钟周期中,两个M的输入引脚上将有有效数据1和 M2.但是,现在我们需要确保只有M2在 M 时操作1保持其输出原样。这是因为,此时此刻,如果 M1操作,然后其输出行更改为 (a2× b2) 而不是其预期值 (a1× b1) 导致错误的 M2输出(a2× b2× c1) 而不是 (a1× b1× c1).

当时钟第三次滴答作响时,所有三个分量都有有效的输入:M1, M2和 A1.但是,我们只希望加法器是可操作的,因为我们期望输出是y1 = (一个1× b1× c1+ d1).这意味着系统的第一个输出将在第三个时钟滴答声后可用。

y2 = (a2 × b2 × c2 + d2)。

当元件遵循类似的激励模式时,我们可以预期下一个输出发生在时钟周期9、12、15等处(图2b)。

流水线设计

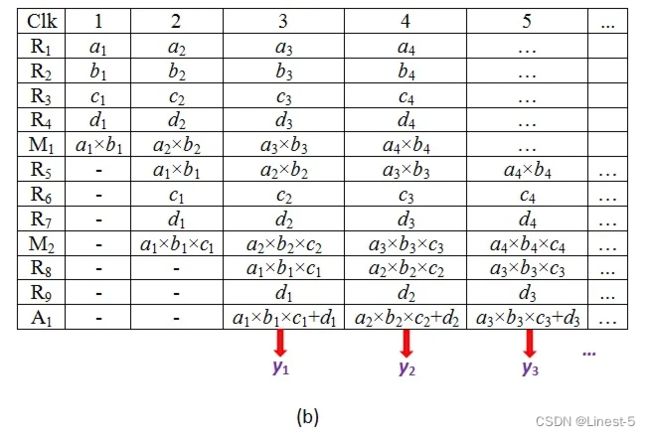

现在,让我们假设我们在输入端向此设计添加寄存器(R1通过 R4),介于 M 之间1和 M2(R5和 R8)和沿直接输入路径(R6、R7和 R9),如图3a所示。

在这里,在第一个时钟滴答时,仅针对寄存器R显示有效输入1通过 R4 (一个1,b1,c1和 d1)和乘数 M1 (一个1和 b1).因此,只有这些才能产生有效的输出。而且,一旦M1产生其输出,它被传递到寄存器R5并存储在其中。

在第二个时钟周期,存储在寄存器R中的值5和 R6 (一个1× b1和 c1) 显示为 M 的输入2这使其能够将其输出呈现为1× b1× c1,而输出 R4 (d1) 被移位到寄存器 R7.同时,即使是第二组数据(a2,b2,c2和 d2) 进入系统并出现在 R 的输出端1通过 R4.

在这种情况下,M1允许在其输入上运行,以便使其输出线从1× b1到2× b2,与非流水线设计的情况不同。这是因为,在此设计中,M输出的任何变化1不影响M的输出2.这是因为确保M的正确功能所需的数据2已锁定在寄存器R中5在第一个时钟滴答时(即使在第二个时钟滴答时也不受干扰)。

这意味着插入寄存器R5已经使 M1和 M2功能独立,因此它们都可以同时对不同的数据集进行操作。

接下来,当时钟第三次滴答作响时,寄存器的输出R8和 R9 ((a1× b1× c1) 和 d1) 作为输入传递给加法器 A1.结果,我们得到我们的第一个输出y1 = ((a1× b1× c1) + d1).然而,在同一时钟滴答作响时,M1和 M2将可以自由操作(a3,b3) 和 (a2,b2,c2),分别。这是可行的,因为存在寄存器R5隔离块 M1从 M2和 R8隔离乘法器 M2从加法器 A1.

因此,在第三个时钟滴答作响时,我们甚至会得到(a3× b3) 和 (a2× b2× c2) 从 M1和 M2,分别除 y 之外1.

现在,当第四个时钟滴答声到来时,加法器A1对其输入进行操作以产生第二个输出 y2 = ((a2× b2× c2) + d2).此外,输出M1从 (a3× b3) 到 (a4× b4)而M2从 (a2× b2× c2) 到 (a3× b3× c3).

在遵循相同的工作模式时,我们可以期望从那时起,每个时钟周期都会出现一个输出数据(图3b),这与非流水线设计的情况不同,在非流水线设计中,我们必须等待三个时钟周期才能获得每个输出数据(图2b)。

流水线的后果

延迟

在所示的示例中,流水线设计显示为第三个时钟周期的每个时钟周期产生一个输出。这是因为每个输入在到达输出之前必须经过三个寄存器(构成管道深度)。类似地,如果我们有一个深度为n的管道,那么每个时钟周期的有效输出仅从n开始显示一个千时钟滴答作响。

在第一个有效输出出现之前,与丢失的时钟周期数相关的这种延迟称为延迟。管道阶段的数量越多,与之关联的延迟就越大。

工作时钟频率的增加

图2a所示的非流水线设计每三个时钟周期产生一个输出。也就是说,如果我们的时钟周期为1 ns,则输入需要3 ns(3×1 ns)才能得到处理并显示为输出。

然后,这条最长的数据路径将成为关键路径,它决定了我们设计的最小工作时钟频率。换句话说,设计系统的频率必须不大于(1/3 ns)= 333.33 MHz,以确保令人满意的运行。

在流水线设计中,一旦管线填满,就会为每个时钟周期生成一个输出。因此,我们的工作时钟频率与定义的时钟频率相同(此处为1/1ns = 1000 MHz)。

这些数字清楚地表明,与非流水线设计相比,流水线设计大大提高了工作频率。

提高吞吐量

流水线设计在每个时钟周期(一旦克服延迟)产生一个输出,而不管设计中包含的流水线级数如何。因此,通过设计流水线系统,我们可以提高FPGA的吞吐量。

更好地利用逻辑资源

在流水线中,我们使用寄存器来存储设计各个阶段的结果。这些组件增加了设计使用的逻辑资源,使其在硬件方面变得非常庞大。

结论

流水线设计的行为非常详尽。您需要在适当的时刻将整个系统划分为单独的阶段,以确保最佳性能。然而,它所付出的辛勤工作与它在设计执行时所呈现的优势是一样的。

文章来自

http://www.allaboutcircuits.com