FPGA 之 时钟,时钟域, 以及复位系统的设计

FPGA时钟和时钟域

时钟树

所谓时钟树为FPGA内部资源, 分 : 全局时钟树, 区域时钟树 , IO时钟树

原则上优先使用全局时钟树, 在GT接口上使用IO时钟树, 一般工具也会对GT时钟加以限制;

时钟树使用方式

-

正确的物理连接

FPGA会由物理管脚专门用于全局时钟设置, 通过查询数据手册可以在PCB设计阶段进行确认,当外部时钟接入此管脚时 ,工具会自动占有全局时钟树资源, 当接入普通信号时不会分配时钟树资源;

-

恰当的代码描述

原语的使用, 即BUFG的使用,可以将PLL的输出等内部时钟进行全局时钟资源的分配;

IO时钟资源需要参考相应接口手册, 以ultrascale 的GTH为例, 其JESD204 的时钟方案针对不同的子类会由不同的专用时钟方案, 和时钟BUF的使用;

需要注意对时钟树上的时钟信号进行任何逻辑操作产生的新信号将不再时钟树上

跨时钟

跨时钟问题的原理与单时钟域避免隐患一样, 即避开不稳定态;

两级采样

高频采低频使用两级采样保证设计行为的正确性和一致性;

低频采高频,则高频时钟域内必须保证其输出信号在一个大于低频周期的时间内保持不变确保不会漏采样;

握手

正常握手逻辑, 需要注意A的握手信号需要在A寄存器输出不变的一个时钟周期后在拉高并保持至少一个B的周期(考虑Skew最好2个)以保证B的顺利采样和数据稳定;

异步FIFO

需注意FIFO的数据平衡,保证 写速率 == 读速率;

PLL和DCM

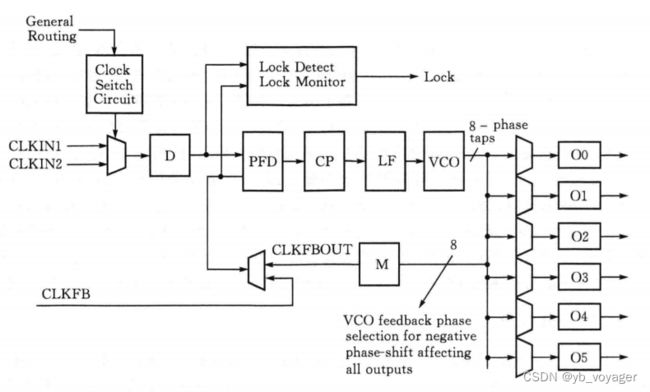

压控振荡器VCO输出的信号为整个锁相环最终的输出信号, 该信号会经过一个整数分频器分频后反馈给鉴相器PD(也是鉴频器), PD比较该反馈信号与输入的本振信号, 如有差别 PD输出差别信号 , 该差别经过低通滤波器LF滤波形成控制VCO频率变化的控制电压, 在该电压的控制下VCO输出信号 的频率或相位会改变, 新的输出如果和本振信号相等则PLL进入锁定;

时钟输入, 输出端口

同一时刻只能有一个CLKIN使能, 但是可以有多个CLKOUT输出;

CLKIN必须是连续时钟信号 , 否则PLL会不断失锁;

CLKIN的频率必须是符合对应器件PLL的时钟频率范围要求;

CLKIN的占空比最好接近50%;

CLKOUT可以有多个输出, 原理是VCO的输出CLKMID会扇出多路, 每一路都有一个分频器和移相器用以产生CLKOUT;

CLKMID的频率根据器件有一定的范围限制, 具体参数查看相应参数;

CLKMID扇出路径上的分频移相系数有限制, 所以各路CLKOUT具有相关性, 要产生两个完全不相关的CLKOUT需要两个PLL;

CLKOUT频率受是时钟树资源限制,其频率和移相精度也有一定限制;

PLL锁定指示端口

PLL中的CLKMID针对CLKIN有一定时间的锁定延迟;

LOCKED信号指示锁定. LOCKED == 0 失锁, LOCKED == 1锁定;

复位的设计

复位分类

同步复位

同步复位 : 复位信号在时钟边沿到来时刻为有效,则执行一次复位, 同步复位为瞬间态, 离散;

优点:

- 同步复位离散, 有利于仿真器的仿真;

- 同步复位只在时钟边沿到来时生效, 可以滤除高于时钟频率的毛刺.提高复位操作可靠性;

- 同步复位系统可以设计为典型同步时序电路,有利于时序约束和时序分析;

缺点:

- 复位信号有效持续时间长度大于一个时钟周期,否则可能会被当作毛刺;

- 同步复位信号与时钟相关, 因此设计和实现必须考虑各种延迟和时间参数;

- 大多数寄存器只有异步复位端口, ,采用同步复位会在寄存器输入端口增加额外的组合逻辑, 消耗更多的资源;

异步复位

异步复位 : 复位信号立即执行, 无关时钟信号的有效边沿,异步复位具有持续性, 连续性;

优点:

- 大多数寄存器否具有异步复位端口, 这样可以节省资源;

- 异步部位不关心复位信号与时钟信号关系, 设计简单;

缺点:(异步信号有效与时钟边沿靠近的一系列问题)

-

容易导致亚稳态;

-

大面积逻辑时因为路径延迟, 导致逻辑功能混乱;

-

易受到毛刺干扰;

复位的设计方法

纯粹的异步复位别用, 尽量使用同步复位;

资源紧张使用低电平有效的异步复位, 同步释放;

同步信号同步复位

always@(posedge clk)

begin

if(rst)

;

else

;

end

同步信号异步复位

always@(posedge clk , negedge rst)

begin

if(!rst)

;

else

;

end

异步信号同步复位

先对异步复位信号进行同步化处理, 在使用同步复位的方式进行复位;

always@(posedge clk)

begin

temp_rst<= a_rst;

b_rst <= temp_rst;

end

always@(posedge clk)

begin

if(b_rst)

;

else

;

end

异步信号异步复位

always@(posedge clk)

begin

temp_rst<= a_rst;

b_rst <= temp_rst;

end

always@(posedge clk,negedge b_rst)

begin

if(!b_rst)

;

else

;

end

复位的高扇出的解决方案

-

寄存器的复制

//同步信号的复制 ,复制若干个类R寄存器 always@(posedge clk) begin rst <= reset; end //异步信号的复制 //temp0 , temp1两级采样, temp2位类R寄存器 always@(posedge clk) begin temp0 <= rst; temp1 <= temp0; temp2 <= temp1; end -

正确利用全局时钟树

时钟树可以保证信号到达FPGA不同触发器的时间差尽可能小,但不保证消耗最短的资源; 那么全局时钟树上的信号群延迟就会比较大, 那么复位信号使用全局时钟树也会存在群延迟, 此时为保证系统稳定性需要对时钟引入一个相同的群延迟;

BUFG resetOnTree(.O(rst),.I(reset)); BUFG clockOnTree(.O(clk),.I(clock)); //rst clk 即可用于设计 //异步信号 always@(posedge clock) begin temp_rst<= a_rst; b_rst <= temp_rst; end BUFG resetOnTree(.O(rst),.I(b_rst)); BUFG clockOnTree(.O(clk),.I(clock)); //此时clock不能是在时钟树上的时钟; //如果clock已经上树, 那么为抵消复位系统引入的延迟可以使用不带BUFG的反馈回路的PLL

本文为个人读书笔记,仅作记录之用