AXI总线学习-------从零开始详细学-------------连载(1)

AXI总线学习连载(1)

鲁迅曾经说过:

学硬件,不是学哪里查哪里,有一些东西是必须系统的学的,不管是嵌入式还是FPGA,硬件学习的积累一定要是系统的。

我也曾经说过:

英文手册非常重要,这是学习硬件标准的不二法门,没有捷径,我们这一行可以不说英语,英语也可以像我和我某些同事一样口语富有乡土气息,但是一定要能熟练看,内心看,做阅读理解一样看

跟着这篇博客,慢慢学习,对着官方文档,不仅可以学会这个协议,更能够学会硬件学习的方法,所谓举一反三。(我说的比鲁迅还多)

好了既然是axi,那么这么说,只要你使用arm架构的芯片,arm和fpga(pl 可编程逻辑)部分通信,或者外部设备通信,你都会用上这个协议。所以一起来学习,打工人!就该把自己的时间全部放在上面

好了不废话了,一起来探索吧!

qq:2198187857 这里放出来一下,就是希望朋友们指导,有不足的地方批评教育一下,作为新手,还是很认真在学习

开贴之前呢还是表示表示,这个是自己翻译学习,感谢实验室的各位同事伙伴的帮助,作为硬件开发学习者,如果想要掌握arm及ps-pl集成soc的流程,学习axi协议必不可少。

由于系统学习axi协议之后,作为经验总结,这里做一个连载吧,按照arm官方手册介绍,通过翻译和解析达到学习目的,也作为日后工作参考。

------------------------------------------------------分割线------聪明人才看得见--------------------------------------------------

学习总结之AXI原型(1) 介绍部分 (具体参考A1章节)

这个章节介绍了axi protocol的一些架构和专业问题,作为开篇学习非常重要。

A1-20 关于AXI原型

A1-21 关于AXI原型的补充修订

A1-22关于AXI基础架构

A1-25重要术语!! 这里强调一下这里,这些术语非常重要,是我们学习之后章节的重要内容,所以每次遇到这些术语时建议回头来看一看

好了这就是本次文章梳理的部分

------------------------------------------------------分割线------聪明人才看得见--------------------------------------------------

AXI把是amba的一支,是一个总线协议,如果说呢,忘记了以前系统学习总线,就这么理解吧,你开车总要开在路上吧,现在axi就是一条路,一种具有标准的路。

其中需要简单的说明一下这个总线协议有什么特点:

1.首先这是一个高速而且高频率的系统,总线本身就是一个数字系统

2.这个总线高带宽并且是一个低延迟的设计

3.不需要使用任何复杂的方式,就能够提供高频率的操作(这是翻译的,我的理解就是我不懂。。。所以就当这么理解吧,有什么问题再说,这个东西已经够复杂得了,看的心累)

4.可以和一系列复杂接口的元器件设备匹配! (这个很重要,如果你玩硬件系统的时候就会发现,真的很重要)

5.可以给很多片上结构提供互联(类似于这个axi interconnector ip核 这种东西用到就看的到了)

6.可以反向兼容AHB和APB接口(其实我也只用到了axi4 lite 和标准 axi 4 接口,委屈脸)

以上叙述呢,大概表明了这个axi 原型是一个什么玩意儿,有一个感性认识,但是接下来会介绍关键特点

1.首先axi分离了 (数据)和(地址+控制)两个部分,请注意(地址+控制)是在一个通道里面的(现在先不管什么是通道之后再看,就记住地址和控制是绑定在一起的,地址是男朋友,控制则是他基友,别问是不是女友!! 硬件工程师能以找女朋友为目标?)

2.支持一个不对齐数据传输(unaligned data transfer),通过字节选通的方式(byte strobe)!!

不对齐数据传输(unaligned data transfer)

字节选通(byte strobe)

这两个概念不用着急什么意思,后续会讲解,这里要有个印象。ps 官方文档就是这样,学习的时候如果遇到了一些不明白术语,其实可以等待后面章节讲因为纲领性质的东西他会先给出来

3.基于了burst(突发)处理(transaction)机制,并且只给出来一个起始地址(start-address)

突发(burst)

处理(transaction)

起始地址(start-address)

这三个概念现在先讲一讲这个处理,所谓处理你就理解为,这个总线上要搞一些事情!发生了事儿,至于burst现在先不讲, 接下来就是起始地址(start-address)这个很好理解,就是第一次要去读也好,写也好,总得第一个地方得有个位置

4.这里将写数据(write data channel)和读数据通道(read data channel)分离开来,请注意是数据通道,并且可以提供一个低功耗的 直接存储器访问(direct memory acess)

写数据(write data channel)

读数据通道(read data channel)

直接存储器访问(direct memory acess)其实这里不用管这三个 只需要知道前两个通道是axi五个通道里面的两个,后续会引入

5.支持处理多个未解决的地址(support for issuing multiple outstanding addresses)

这个也先不管,但是要有印象,这是axi一个特性

6.支持无序的处理(support for out-of-order transaction )

这个也先不管,但是要有印象,这是axi一个特性

7.提供寄存器进行一些时序终止操作。

这个也先不管,但是要有印象,这是axi一个特性

好了 以上就是axi的一些显著特点,我们的学习其实就是围绕这些特点的原理,设计思想,用途而展开。(AXI原型包括了AXI4 和 AXI4 LITE哈)

------------------------------------------------------分割线------聪明人才看得见--------------------------------------------------

AXI架构

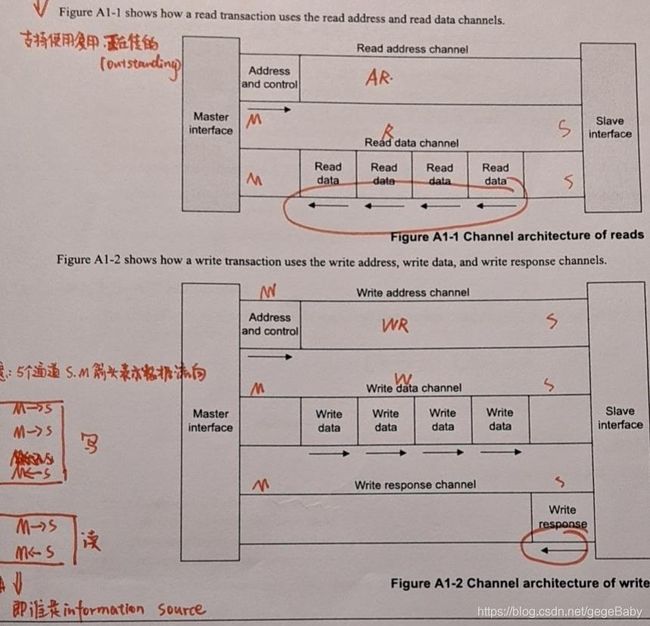

1.首先我们一定要熟悉记忆在AXI架构里面一共有五个通道,我把他们分成了两组来看

读地址通道(read address channel) AR

读数据通道(read data address channel)R

写地址通道(write address channel )AW

写数据通道(write data channel )W

写响应通道(write response channel ) B

总结一下我们可以看见有两组信号,其中分别属于读和写的,但是要区分开,这个读和写其实是对应于链接总线两边的设备而言的,也就是我们常说的master主设备和slave从设备。

请在这里放大你的眼睛,主设备和从设备的概念要和源设备和目标设备区分

这里我用英文注解一下 master 主设备 slave 从设备 source 源设备 destination目标设备 请记住喔!!!!

先补充一下:主设备和从设备分别指axi两边连接的东西。

源设备指的是发出某个信号的源泉,目标设备是这个源泉抵达的地方

在后续可以区分哈

2.现在开始讨论一下

一个地址通道(AR和AW)他们在这个通道内传递的数据其实都是地址信息和控制信息,这些信息都是表示R或者W内真实数据的一些特性,比如地址是用来放这些真实数据的位置,

控制信息表示应该用什么样的方式放这些数据。(这是关于两个地址通道的)

一个写数据通道(W)可以把主设备发下去的数据写给从设备,当发生了写处理这个行为时(就是传若干数据),从设备会通过B(写响应)通道告诉主设备这个写行为的完成情况。

同理,一个读数据通道(R)就是指从设备把要读的数据发给主设备,好了读处理时是没有单独的读响应通道,读响应这个操作是在(AR)读地址当中完成的

以下又增加一些细节的axi 原型特性

在真实的数据传输前,axi允许先发送地址信息和控制信息(请记得地址和控制信息是在一个通道里的),当然这里要分读操作和写操作哈

作为总结和复习,细细品味一下这官方图的含义哈

当你看懂了这图,说明本次的就明白了!