【Verilog刷题篇】硬件工程师从0到入门2|组合逻辑

Verilog从0到入门2-组合逻辑

- 前言

- Q1:4位数值比较器电路

- Q2:4bit超前进位加法器电路

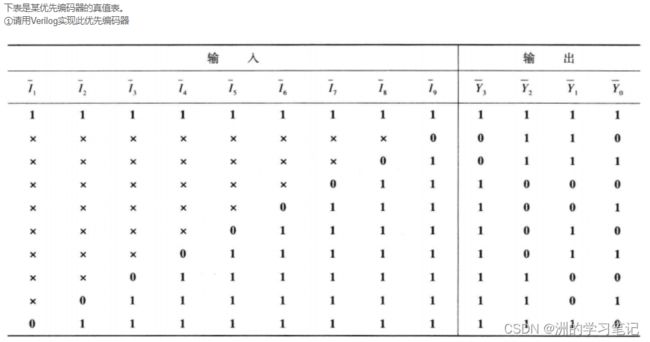

- Q3:优先编码器电路①

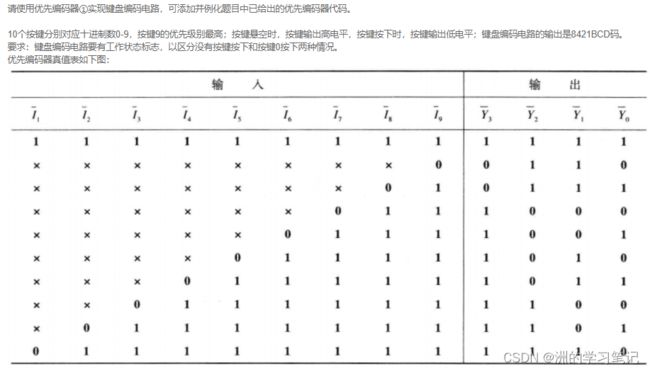

- Q4:用优先编码器①实现键盘编码电路

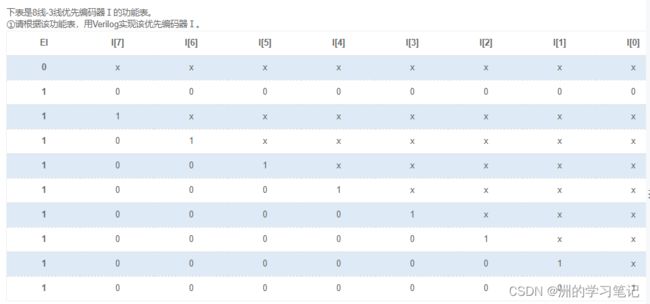

- Q5:优先编码器Ⅰ

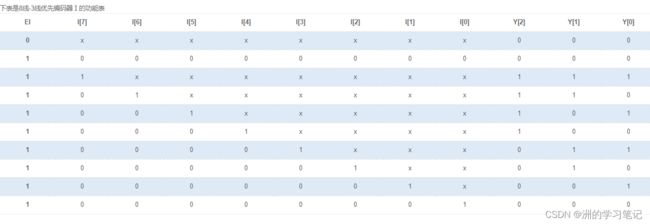

- Q6:使用8线-3线优先编码器Ⅰ实现16线-4线优先编码器

- 总结:小白跟大牛都在用的好平台!

前言

- 硬件工程师近年来也开始慢慢吃香,校招进大厂年薪总包不下30-40w的人数一大把!而且大厂人数并没有饱和!

- 本期是【Verilog刷题篇】硬件工程师从0到入门1|基础语法入门,有不懂的地方可以评论进行讨论! - 推荐给大家一款刷题、面试的神器,我也是用这一款神器进行学习Verilog硬件代码的!

- ~链接如下:刷题面试神器跳转链接

- 也欢迎大家去牛客查看硬件工程师招聘职位的各类资料,并进行提前批投递面试!

- 小白新手可以通过该神器进行日常的刷题、看大厂面经、学习计算机基础知识、与大牛面对面沟通~ 刷题的图片已经放在下面了~

![]()

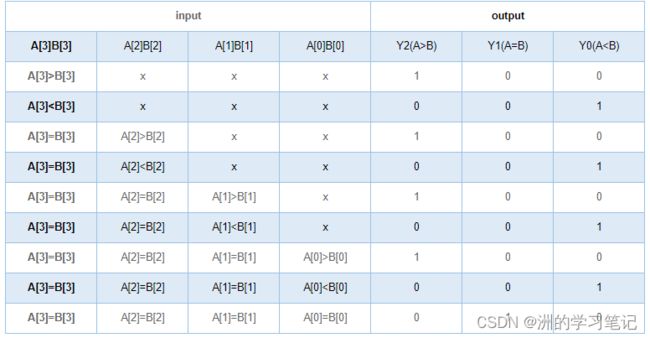

Q1:4位数值比较器电路

问题描述:某4位数值比较器的功能表如下。请用Verilog语言采用门级描述方式,实现此4位数值比较器。

输入描述:input [3:0] A ,input [3:0] B 示例代码: 输入描述: 输出描述: 示例代码: 输入描述:input [8:0] I_n 示例代码: 输入描述:input [9:0] S_n 示例代码: 输入描述: 示例代码: 问题描述:请使用2片该优先编码器Ⅰ及必要的逻辑电路实现16线-4线优先编码器。优先编码器Ⅰ的真值表和代码已给出。 输入描述: 示例代码: 快来点击链接进行跳转注册,开始你的保姆级刷题之路吧!刷题打怪码神之路 另外这里不仅仅可以刷题,你想要的这里都会有,十分适合小白和初学者入门学习~

输出描述:

output wire Y2 , //A>B

output wire Y1 , //A=B

output wire Y0 //A`timescale 1ns/1ns

module comparator_4(

input [3:0] A ,

input [3:0] B ,

output wire Y2 , //A>B

output wire Y1 , //A=B

output wire Y0 //AQ2:4bit超前进位加法器电路

输入信号:

A_in[3:0],

B_in[3:0]

C_1

类型:wire

输出信号:

S[3:0]

CO

类型:wire

`timescale 1ns/1ns

module lca_4(

input [3:0] A_in ,

input [3:0] B_in ,

input C_1 ,

output wire CO ,

output wire [3:0] S

);

wire [3:0] G;

wire [3:0] P;

wire [3:0] C;

assign G = A_in & B_in;

assign P = A_in ^ B_in;

assign C = G | (P & {C[2:0], C_1});

assign S = P ^ {C[2:0], C_1};

assign CO = C[3];

endmodule

Q3:优先编码器电路①

输出描述:output reg [3:0] Y_n`timescale 1ns/1ns

module encoder_0(

input [8:0] I_n ,

output reg [3:0] Y_n

);

always @(*) begin

casex(I_n)

9'b 0xxxxxxxx : Y_n=4'b0110;

9'b 10xxxxxxx : Y_n=4'b0110;

9'b 110xxxxxx : Y_n=4'b1000;

9'b 1110xxxxx : Y_n=4'b1001;

9'b 11110xxxx : Y_n=4'b1010;

9'b 111110xxx : Y_n=4'b1011;

9'b 1111110xx : Y_n=4'b1100;

9'b 11111110x : Y_n=4'b1101;

9'b 111111110 : Y_n=4'b1110;

9'b 111111111: Y_n=4'b1111;

default: Y_n=4'bxxxx;

endcase

end

endmodule

Q4:用优先编码器①实现键盘编码电路

输出描述:

output wire[3:0] L ,

output wire GS`timescale 1ns/1ns

module encoder_0(

input [8:0] I_n ,

output reg [3:0] Y_n

);

always @(*)begin

casex(I_n)

9'b111111111 : Y_n = 4'b1111;

9'b0xxxxxxxx : Y_n = 4'b0110;

9'b10xxxxxxx : Y_n = 4'b0111;

9'b110xxxxxx : Y_n = 4'b1000;

9'b1110xxxxx : Y_n = 4'b1001;

9'b11110xxxx : Y_n = 4'b1010;

9'b111110xxx : Y_n = 4'b1011;

9'b1111110xx : Y_n = 4'b1100;

9'b11111110x : Y_n = 4'b1101;

9'b111111110 : Y_n = 4'b1110;

default : Y_n = 4'b1111;

endcase

end

endmodule

module key_encoder(

input [9:0] S_n ,

output wire[3:0] L ,

output wire GS

);//11_1111_1111 L:0000 GS:0

//11_1111_1110 L:0000 GS:1

wire [3:0] L_temp

encoder_0 encoder(S_n[9:1],L_temp);

assign L = ~L_temp;

assign GS = ~((S_n[0])&(&L_temp));

endmodule

Q5:优先编码器Ⅰ

input [7:0] I ,

input EI

输出描述:

output wire [2:0] Y ,

output wire GS ,

output wire EO`timescale 1ns/1ns

module encoder_83(

input [7:0] I ,

input EI ,

output wire [2:0] Y ,

output wire GS ,

output wire EO

);

reg [2:0] Y_reg;

always@(*)begin

casex(I)

8'b1xxx_xxxx:Y_reg = 3'd7;

8'b01xx_xxxx:Y_reg = 3'd6;

8'b001x_xxxx:Y_reg = 3'd5;

8'b0001_xxxx:Y_reg = 3'd4;

8'b0000_1xxx:Y_reg = 3'd3;

8'b0000_01xx:Y_reg = 3'd2;

8'b0000_001x:Y_reg = 3'd1;

8'b0000_0001:Y_reg = 3'd0;

8'b0000_0000:Y_reg = 3'd0;

default:Y_reg = 3'd0;

endcase

end

assign Y = (EI == 1'b1)?Y_reg:3'd0;

assign GS = ((EI == 1'b1)&&(I != 8'b0000_0000))?1'b1:1'b0;

assign EO = ((EI == 1'b1)&&(I == 8'b0000_0000))?1'b1:1'b0;

endmodule

Q6:使用8线-3线优先编码器Ⅰ实现16线-4线优先编码器

可将优先编码器Ⅰ的代码添加到本题答案中,并例化。

优先编码器Ⅰ的代码如下:module encoder_83(

input [7:0] I ,

input EI ,

output wire [2:0] Y ,

output wire GS ,

output wire EO

);

assign Y[2] = EI & (I[7] | I[6] | I[5] | I[4]);

assign Y[1] = EI & (I[7] | I[6] | ~I[5]&~I[4]&I[3] | ~I[5]&~I[4]&I[2]);

assign Y[0] = EI & (I[7] | ~I[6]&I[5] | ~I[6]&~I[4]&I[3] | ~I[6]&~I[4]&~I[2]&I[1]);

assign EO = EI&~I[7]&~I[6]&~I[5]&~I[4]&~I[3]&~I[2]&~I[1]&~I[0];

assign GS = EI&(I[7] | I[6] | I[5] | I[4] | I[3] | I[2] | I[1] | I[0]);

//assign GS = EI&(| I);

endmodule

input [15:0] A ,

input EI

输出描述:

output wire [3:0] L ,

output wire GS ,

output wire EO`timescale 1ns/1ns

module encoder_83(

input [7:0] I ,

input EI ,

output wire [2:0] Y ,

output wire GS ,

output wire EO

);

assign Y[2] = EI & (I[7] | I[6] | I[5] | I[4]);

assign Y[1] = EI & (I[7] | I[6] | ~I[5]&~I[4]&I[3] | ~I[5]&~I[4]&I[2]);

assign Y[0] = EI & (I[7] | ~I[6]&I[5] | ~I[6]&~I[4]&I[3] | ~I[6]&~I[4]&~I[2]&I[1]);

assign EO = EI&~I[7]&~I[6]&~I[5]&~I[4]&~I[3]&~I[2]&~I[1]&~I[0];

assign GS = EI&(I[7] | I[6] | I[5] | I[4] | I[3] | I[2] | I[1] | I[0]);

//assign GS = EI&(| I);

endmodule

module encoder_164(

input [15:0] A ,

input EI ,

output wire [3:0] L ,

output wire GS ,

output wire EO

);

wire E_conect;//定义中间量

wire [2:0] Y1;

wire [2:0] Y0;

wire GS0;wire GS1;

encoder_83 U0(//低位

.I(A[7:0]),

.EI(E_conect),

.Y(Y0),

.GS(GS0),

.EO(EO)

);

encoder_83 U1(//高位

.I(A[15:8]),

.EI(EI),//因为是从高位开始查找不为零的数,所以EI先给高位芯片

.Y(Y1),

.GS(GS1),

.EO(E_conect)

);

assign GS= GS1|| GS0;

assign L[3]=GS1;

assign L[2] = Y1[2] | Y0[2];

assign L[1] = Y1[1] | Y0[1];

assign L[0] = Y1[0] | Y0[0];

endmodule

总结:小白跟大牛都在用的好平台!

- 本期是【Verilog刷题篇】硬件工程师从0到入门1|基础语法入门,有不懂的地方可以评论进行讨论!

1、算法篇(398题):面试必刷100题、算法入门、面试高频榜单

2、数据结构篇(300题):都是非常经典的链表、树、堆、栈、队列、动态规划等

3、语言篇(500题):C/C++、java、python入门算法练习

4、SQL篇(82题):快速入门、SQL必知必会、SQL进阶挑战、面试真题

5、大厂笔试真题:字节跳动、美团、百度、腾讯…掌握经验不在惧怕面试!![]()