【UCIe】UCIe 支持的协议及操作模式

点击查看精选 UCIe 系列文章

点击进入【芯片设计验证】社区,查看更多精彩内容

声明:

- 作者主页:【MangoPapa的CSDN主页】。

- ⚠️ 本文首发于CSDN,转载或引用请注明出处【https://mangopapa.blog.csdn.net/article/details/126786119】。

- ⚠️ 本文目的为 个人学习记录 及 知识分享。因个人能力受限,存在协议解读不正确的可能。若您参考本文进行产品设计或进行其他事项并造成了不良后果,本人不承担相关法律责任。

- ⚠️ 若本文所采用图片或相关引用侵犯了您的合法权益,请联系我进行删除。

- 欢迎大家指出文章错误,欢迎同行与我交流 ~

- 邮箱:[email protected]

文章目录

- 0. 前言

- 1. 三种协议

- 2. 七种操作模式

-

- 2.1 64B Flit Raw Mode

- 2.2 68B Flit Mode

- 2.3 256B Flit Mode

- 3. 协议及操作模式的协商

-

- 3.1 协议协商

- 3.2 操作模式协商

- 4. 协议与操作模式的依赖关系

-

- 4.1 不同协议对 Flit Mode 的需求

- 4.2 不同 RP、EP 互连时应采用的操作模式

- 5. 参考

0. 前言

CXL 2.0 建立在 PCIe 5.0 之上,PCIe 6.0 进一步 推进 CXL 2.0 的应用,CXL 3.0 继承 PCIe 6.0 全部特性,UCIe 兼容 PCIe 6.0 及 CXL 2.0/3.0。在 Intel 主导下,PCIe -> CXL -> UCIe 一脉相承一路走来。今天,再聊聊 UCIe 协议层的协议及 Flit Mode。 点击查看 配套 PPT

1. 三种协议

之前【UCIe】UCIe 协议层介绍 一文中简单介绍过 UCIe Link 支持的协议及操作模式。截至目前,UCIe 支持 PCIe、CXL 等标准协议,在链路双方约定好的情况下也支持 Vendor 自定义的流协议(Streaming Protocol)。无论采用哪种协议,发送的数据包都应该为定长的 Flit 数据包。

对于 CXL 协议,UCIe Spec 中明确提到不支持 UCIe 1.1,只支持 CXL 2.0、CXL 3.0 及之后出现的版本。CXL 1.1 是支持 68B Flit 的,CXL 2.0 及 CXL 3.0 也兼容 CXL 1.1,那么为什么 UCIe 不支持 CXL 1.1 呢?(待讨论)

对于 PCIe 协议,UCIe Spec 明确提到其支持 PCIe 6.0 Flit Mode。PCIe Gen6 时,采用标准的 256B Flit Mode。PCIe 6.0 是兼容 PCIe 1.0~5.0 的,那么 UCIe 是否支持 PCIe 1.0~5.0 呢?Spec 并未明确指出,只说明支持 PCIe Gen5。考虑到 CXL 是建立在 PCIe Gen5 基础上的,单纯的 PCIe Gen5 数据包是没有 Flit 概念的。此时必须采用 CXL 2.0 68B Flit Mode(CXL.io)。对于 Gen1~Gen4 速率,应该是不支持的。那么是否支持 PCIe 5.0 呢?笔者认为,对于 UCIe 而言,没有 PCIe x.0 的概念,其只关心 PCIe 是 Flit Mode 还是 Non-Flit Mode。在 UCIe 链路能力协商的时候,{AdvCap.Adapter} 中的 PCIe Flit Mode 对应 PCIe 6.0 Flit Mode,{AdvCap.CXL} 中的 PCIe capable/enable 对应 CXL 2.0 68B Flit Mode。

2. 七种操作模式

UCIe 链路支持 7 种操作模式,各操作模式编号如表 1 所示。7 种操作模式按照 Flit Size 可以分为 64B、68B、256B 三类:

- 64B Flit 对于的操作模式只用 Raw Mode 一种,Streaming Protocol 必须支持该模式,PCIe 及 CXL 协议可以选配该模式。

- 68B Flit 对于的操作模式有 CXL 2.0 68B Flit Mode 及 CXL 68B-Enhanced Flit Mode 两种。CXL 2.0 68B Flit Mode 是 PCIe Gen5 及 CXL 2.0/3.0 共用的,CXL 68B-Enhanced Flit Mode 是 CXL 协议专用的。

- 256B Flit 对于的操作模式有 4 种,其中两种 Standard 256B Flit Mode、两种 Latency-Optimized 256B Flit Mode。

| Format No. | Flit Mode | Protocol On UCIe Link |

|---|---|---|

| 1 | Raw Mode | PCIe 6.0, CXL 2.0, CXL 3.0 |

| 2 | CXL 2.0 68B Flit Mode | PCIe 6.0 |

| 3 | Standard 256B Flit Mode for PCIe | PCIe 6.0 |

| 4 | Standard 256B Flit Mode for CXL | CXL 3.0 |

| 5 | Latency-Optimized 256B Flit Mode | CXL 3.0 |

| 6 | Latency-Optimized 256B Flit Mode | CXL 3.0 |

| 7 | CXL 68B-Enhanced Flit Mode | CXL 2.0, CXL 3.0 |

2.1 64B Flit Raw Mode

Raw Mode 为 Format 1,本意是给 UCIe Retimer 用的。其他操作模式下,Flit 中留有 Flit_Hdr、CRC、FEC 等相关字段由 Adapter 来填充,但 Raw Mode 操作模式下,Flit 中所有字段均由协议层进行填充。这也不难理解,这本来就是给 UCIe Retimer 用的,Retimer 中完完整整传递 Flit 就好了,无需重新添加 Flit_Hdr 或添加校验信息。Raw Mode 下,Flit 数据在 Adapter 中是透传的,也正因为如此,原来需要在 Adapter 中做的 Retry、CRC、FEC 相关 Check 功能必须转移到协议层中实现。

2.2 68B Flit Mode

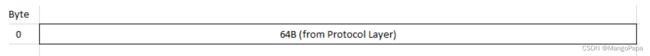

68B Flit Mode 是 PCIe 及 CXL 都具备的。PCIe Gen5 及 CXL 2.0 时都支持 68B Flit Mode。准确而言,PCIe 不具备 68B Flit Mode,它只是凭借其 Gen5 跟 CXL 2.0 的近亲关系,借用了 CXL 2.0 的 Flit Mode。不管是 PCIe Gen5 还是 CXL 2.0,其 68B Flit 在格式上没有区别,都是 2B Flit_Hdr + 64B Data + 2B CRC(图 2)。协议层只提供 64B 数据(TLP、Token、Idle 等),Flit Header 及 CRC 由 D2D Adapter 来填充。

根据链路上是否为 CXL 协议,可以将 68B Flit Mode 细分为两种:

- Format 2: CXL 2.0 68B Flit Mode。UCIe 链路中存在 PCIe Gen5 设备时,或者说 UCIe 链路上采用的为 PCIe 协议时,68B Flit 为 CXL 2.0 68B Flit Mode。

- Format 7: CXL 68B-Enhanced Flit Mode。UCIe 链路两侧均为 CXL 2.0 设备时,68B Flit 为 CXL 68B-Enhanced Flit Mode。

广义上,CXL 2.0 68B Flit Mode 包括 CXL 68B-Enhanced Flit Mode。

狭义上,CXL 2.0 68B Flit Mode 不包括 CXL 68B-Enhanced Flit Mode。

2.3 256B Flit Mode

256B Flit Mode,这个也是 PCIe 和 CXL 都有的,但是 UCIe 严格地将两者分为了 PCIe 6.0 Flit Mode 及 CXL 256B Flit Mode。之所以将两者区分开,是因为两者在格式上存在区别。

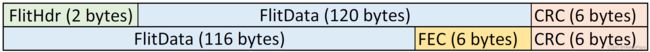

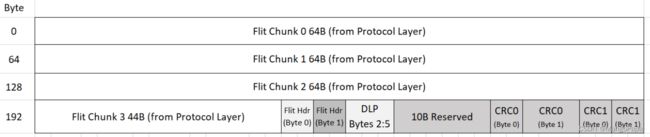

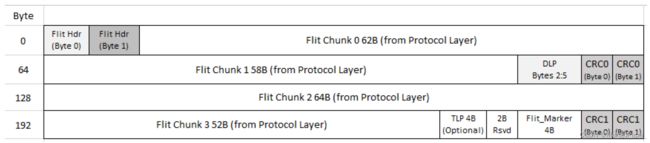

PCIe 6.0 Flit 只有一种格式:236B TLP + 6B DLP + 8B CRC + 6B FEC(图 3)。CXL 3.0 Flit 格式有两种,一种是标准的 256B Flit(2B Flit_Hdr + 240B Payload + 8B CRC + 6B ECC),一种是 Latency 优化后的 256 Flit(2B Flit_Hdr + 120B Payload + 6B CRC + 116B Payload + 6B FEC + 6B CRC),分别如图 4, 5 所示。进一步地,根据 CXL 协议栈的不同(CXL.io 或 CXL.cachemem),每种 CXL 3.0 Flit Mode 又分为两种,其中 CXL.io 的 116B Payload 中包含有 4B DLP 。

跟 PCIe 6.0 及 CXL 3.0 原始 Flit 格式相匹配,UCIe 一对一地提供有 3 类(4 种)格式的操作模式:

- Format 3: Standard 256B Flit Mode for PCIe,即 PCIe 6.0 Flit Mode。其 Flit 数据格式如图 6 所示。鉴于UCIe PHY 有其基于 Sideband Message 的链路和功耗管理机制,原 PCIe 6.0 Flit 中跟 PCIe PHY 链路管理及功耗管理相关的 DLLP 均不再使用。UCIe 工作在 Standard 256B Flit Mode for PCIe 时,在原来 DLLP 位置插入 2B Flit_Hdr。由于

- Format 4: Standard 256B Flit Mode for CXL,即 CXL 3.0 的标准 Flit Mode。其 Flit 数据格式如图 7 所示。所有的 CXL 相关操作模式,不包括 Raw Mode,不管是 68B 还是 256B,其 Flit_Hdr 永远是在 Flit 最靠前的 2B 中,这也是其跟 Standard 256B Flit Mode for PCIe 的不同。

- Format 5/6: Latency-Optimized 256B Flit Mode。Format 5 和 Format 6 的唯一区别是 是否支持 Optional Bytes,Format 5 不支持 Optional Bytes,Format 6 支持 Optional Bytes。其 Flit 数据格式如图 8 所示。可见,CXL 3.0 Latency-Optimized Flit 将 Standard 256B Flit 一分为二,通过更小的 Flit Size 来更早地对 Flit 数据进行确认,从而更早地收集正确的 Flit 数据或对 Flit 错误进行处理,以此实现更低的传输时延。。

3. 协议及操作模式的协商

3.1 协议协商

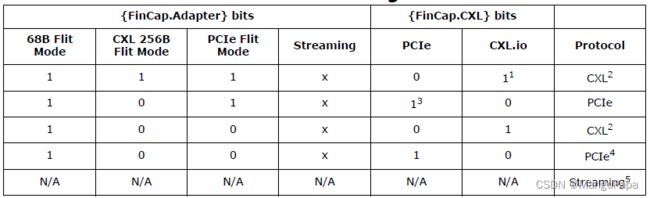

UCIe 链路初始化期间,两个 UCIe 通过 Sideband 互相交换 {AdvCap.Adapter}、{AdvCap.CXL} Message 来协商 UCIe 链路要采用的协议及操作模式。协商一致后反馈 {FinCap.Adapter}、{FinCap.CXL} Message,通过这两个字 Message 相关字段即可知晓当前采用的是 PCIe 还是 CXL 协议。如果协商来协商去,没有达成共识,那就不要回复 {FinCap.*} 默认是 Streaming Protocol、Raw Mode。

Spec 给了个协议协商结果判决的真值表,如表 2 所示,可以参考。一旦协商完成,除非再次进行链路训练再次协商,否则中途不能切换协议。

若两个 Protocol Layer 通过 Stack Mux 接在了同一组 Adapter 上,两个可以是不同的协议吗?比如 Stack0 是 PCIe 协议,Stack1 是 CXL 协议?根据 Spec 描述,两个协议层通过各自的 FDI 接口与 Adapter 链接,链路初始化过程中独立协商。按这个思路,两个 Stack 是可以走不同协议的。在接收对端发来的 Flit 时,通过解析 Flit_Hdr 中的相关 Bit 将 Flit 分发到对应的 Stack。那么,支持一个 Streaming Protocol 一个 PCIe 吗?支持两个 Streaming Protocol Stack 吗?(待讨论)讨论结果:支持。前提是 Streaming Procotol 采用的 Raw Mode Flit Header 跟标准的 Flit Header 一致,确保能过识别出 Flit 的来源和去向。

3.2 操作模式协商

跟协议协商同时进行的还要操作模式的协商。Spec 也给了个 UCIe 链路 Flit 格式协商判决真值表,如表 3 所示。表 3 有点难以看懂,整理为图 9 所示判决逻辑图。

4. 协议与操作模式的依赖关系

4.1 不同协议对 Flit Mode 的需求

Spec 中说到,①若建议 PCIe 协议(不一定采纳),必须支持 68B Flit Mode。还说到,②支持 PCIe 协议的时候必须支持 Standard 256B Flit Mode for PCIe。难道说,UCIe 链路采用 PCIe 协议的话,必须同时支持 68B Flit Mode 和 Standard 256B Flit Mode for PCIe 吗?这里多少有点让人疑惑。依据 Spec 提供的 UCIe 不同协议对 Flit Mode 的需求表(表 4),笔者认为,①的说法是无误的,只要 UCIe Module 支持 PCIe 协议,不论最终是否谈妥,其都应该支持 Non-Flit 的 68B Flit Mode,PCIe Standard 256B Flit Mode 则是可选项,毕竟不是所有的 PCIe 都支持 Flit Mode;对于 ② 中的 PCIe 协议,具体应指 PCIe 6.0 Flit Mode,所有支持 Flit Mode 的 PCIe 设备都有向前兼容 Non-Flit Mode。

根据表 4 还可以发现,只有 CXL 3.0 支持 CXL 256B Flit Mode,支持 CXL 256B Flit Mode 的话,必须向前兼容 PCIe 6.0 Flit Mode 及 68B Flit Mode。对于 CXL 2.0 设备,可以不支持 CXL 256B Flit Mode 或 PCIe 6.0 Flit Mode,但一定要支持CXL 2.0 68B Flit Mode(Format 2 + Format 7)。

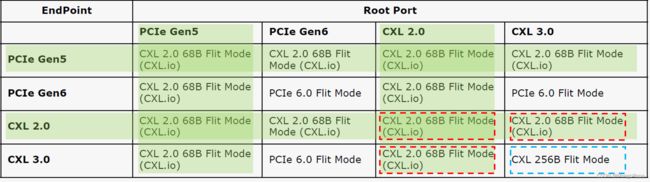

4.2 不同 RP、EP 互连时应采用的操作模式

UCIe 的一大宗旨就是“通用”,UCIe 链路连接的两个 UCIe Module 在能力方面不必完全匹配。当两个具备不同的协议版本、不同的协议、不同的操作模式的 UCIe Module 连接在一起时,该采用何种操作模式呢?Spec 中列了个表(表 5),相对清楚。

根据表 5,有以下结论:

- 只要链路中出现 PCIe Gen5 或 CXL 2.0 设备,即采用 CXL 2.0 68B Flit Mode。

- 链路两侧均为 CXL 3.0 时,采用 CXL 256B Flit Mode。

- 此外,采用 PCIe 6.0 Flit Mode。

表 5 中所述 CXL 2.0 68B Flit Mode 应是指广义上的 68B Flit Mode,包含 Format 2 (CXL 2.0 64B Flit Mode) 和 Format 7 (CXL 68B-Enhanced Flit Mode) 两种。当 ①链路两端含有 PCIe Gen5 时,或 ②链路两端为 PCIe、CXL 2.0 混合时,具体应指 Format 2;当链路两端均为 CXL 协议且较低版本为 CXL 2.0 时(红色虚线框内的),具体应指 Format 7。

根据表 5,当链路两端均为 CXL 3.0 时,应选用 CXL 256B Flit Mode。这里必须时 CXL 256B Flit Mode 吗?笔者认为,不尽然。CXL 3.0 向下兼容 CXL 2.0、PCIe Gen6,当然也可以采用 68B Flit Mode 和 PCIe 256B Flit Mode,有何不可呢?这表里只是提供性能最高的选择罢了。

5. 参考

- UCIe Spec r1.0, Chapter 2, 3

- 【UCIe】UCIe 协议层介绍

- MangoPapa: UCIe 协议层支持的协议、Flit Mode 及一些讨论

|

|

精选往期 UCIe 协议系列文章,请查看【 Chiplet 专栏】

⬆️ 返回顶部 ⬆️