《FPGA设计实战演练》学习笔记(一)FPGA板级基础五要素电路介绍及注意事项(最小系统)

目录

- 基础五要素(类似最小系统板)

-

- 电源电路

-

- 核心电压

- I/O电压

- 辅助电压

- 常见的供电方案

- GND的注意事项

- 时钟电路

- 复位电路

- 配置电路

- 外设电路

基础五要素(类似最小系统板)

电源电路

FPGA的电压需求有三类:核心电压、I/O电压、辅助电压。

核心电压

保证FPGA内部逻辑电路正常运行的基本电压,一般在官方提供的器件手册中找到。

I/O电压

FPGA的所有信号引脚基本可以作为普通I/O口使用,通常这些引脚会根据排列位置分为几个bank,同一个bank内的I/O引脚共用一个I/O电压,可以给不同的bank供给不同的电压,他们之间是不连通的。

书中举例Cyclone III 的某些bank支持LVDS差分电平标准(Low-Voltage Differential Signaling,低电压差分信号,这种标准采用极低的电压摆幅高速差动传输数据,可以实现点对点或一点对多点的连接,具有低功耗、低误码率、低串扰和低辐射等优点),一般器件手册会要求供给1.5v电压。

辅助电压

除了上面的两个,其他的都称为辅助电压。其中有一个重点是PLL(Phase Locked Loop,锁相环)功能块的供电电压,PLL是模拟电路,FPGA的其他部分是数字电路,所以PLL的输入电压有讲究,需要专门的电容电路做滤波处理。

常见的供电方案

有LDO稳压器、DC/DC芯片、电源模块。

LDO低纹波,电流输出能力较差,便宜、电路简单

DC/DC芯片保证较高的电源转化率,散热容易,输出电流也大。(最好选择)

电源模块稳定性能,价格贵,快捷简单。

参考的有:器件手册(handbook)、应用笔记(application notes)、白皮书(white paper)

GND的注意事项

统一公共接地,但要注意一些特殊应用是否有隔离的要求。

如果FPGA芯片的底部中央有接地焊盘,一定要接,否则FPGA可能不工作,这个地是连接FPGA内部的很多中间信号的地端,不和其他的地信号直接导通

时钟电路

FPGA器件的时钟信号源通常使用晶体振荡器(简称晶振)产生时钟信号。

在实际应用中,成百上千甚至更多的寄存器很可能共用一个时钟源,那么从时钟源到不同寄存器间的延时也可能存在较大偏差(通常称为时钟网络延时),这个时间差过大是很要命的。因此,FPGA 器件内部设计了一些称为“全局时钟网络”的走线池。通过这种专用时钟网络走线,同一时钟到达不同寄存器的时间差可以控制到很小的范围内。

所以一般将晶振产生的时钟信号连接到“全局时钟专用引脚”(GCLK)上。FPGA内部的高扇出控制信号(Fanout,即扇出,指模块直接调用的下级模块的个数)也要接到这个上。

时钟走线要尽可能短,有条件的要包地处理。

复位电路

一个低电平复位的输入信号,阻容复位电路和专用的复位芯片,

因为FPGA器件是基于RAM结构的,它通常需要一颗用于配置的外部ROM或Flash进行上电加软,待系统上电稳定后,FPGA器件首先需要足够的时间用于配置加载操作,只有在这个过程结束后,FPGA才能够进人正常的运行模式。

所以要把握好时间的长短,太长影响体验,太短复位时间不够。尽量使用专用的复位引脚。

配置电路

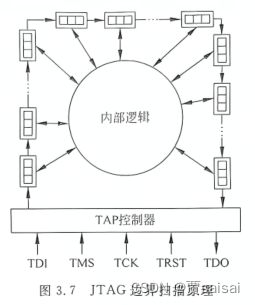

JTAG(joint test action group,联合测试行为组织)可编程芯片的在线系统编程

在FPGA器件内部,边界扫描寄存器由TDI信号作为数据输入﹐TDO信号作为数据输出,形成一个很大的移位寄存器链。而JTAG通过整个寄存器链,可以配置或者访问FPGA器件的内部逻辑状态或者各个I/O引脚的当前状态。

JTAG的4个信号TCK/TMS/TDI/TDO( TRST信号一般可以不用)以及电源、地连接到下载线即可。

FPGA一旦掉电,SRAM数据丢失,FPGA通常需要外挂一个用于保存当前配置数据流的PROM或Flash芯片,通常称为“配置芯片”。

注意:

·配置芯片尽量靠近FPGA。

·考虑配置信号的完整性问题,必要时增加阻抗匹配电阻。

·部分配置引脚可以被复用,但要谨慎使用,以免影响器件的上电配置过程。

外设电路

书中的注意事项:

·输人和输出时钟信号尽量分配到专用的引脚上。

·差分信号对必须分配到支持差分传输的专用引脚上。

·高速信号分配到支持高速传输的专用引脚上,如支持DDR的专用I/O接口。.一些硬核使用的引脚可能是固定的,千万不能随意分配。

·总线信号尽量分配到同一个bank或者相近的bank 中。

·一些可能产生噪声干扰的信号如时钟信号,尽量远离器件的配置信号和其他的敏感信号

·引脚分配时要尽可能减少交叉连接。