数字IC后端设计实现问答(附新年千元现金红包大奖)

数字IC后端设计实现问答(附新年千元现金红包大奖)

文章右侧广告为官方硬广告,与吾爱IC社区无关,用户勿点。点击进去后出现任何损失与社区无关。

农历新年就快到了,为了感谢各位粉丝朋友的支持和陪伴,吾爱 IC 社区将在农历三十当天发出千元现金红包大奖。本着公平公正的原则,小编今天抽空发布下活动细则。当然之前承诺各位新年的时候会搞一个知识星球门票的优惠活动,也会如期开展(老会员续费和新会员入会门票)。关于活动的细节,将会在文末做一个介绍。

如果仅仅是发布新年福利活动细则,未免显得太水了,不太像小编的风格。那么,今天小编将分享数字 IC 后端实现中几个经典问题。这些问题大都来源于知识星球上的问题主题。

- 提问:星主大大,请教个问题:后端像 Register to memory path 和 memory to Register path 这两种 Timing 路径前端,后端如何更好的让时序满足?谢谢

【点评】单纯从优化时序的角度看,主要有以下几种方法。

- 设置 Group_path

将有 timing violation 的点进行归类分组,设置 group_path,并为其设置一个合理的 weight。如果 group 比较多,还需要设置 priority 选项。

对于 group path 比较多的情况,可以考虑采用自动调整 weight 的策略。相应的脚本,知识星球上有直接能用的完整脚本。

- Create_bounds 法

将逻辑分布不太理想的模块,限制在某个范围内,来实现 timing 的最优化。关于 bounds 的使用,经验性要求还是比较高的。如果规划的 bounds 不好,timing 可能会比工具自动 placement 还要差。

对于高频设计实现模块,比如设计要求的周期为 1ns,而 memory 的 CK—>Q delay 往往就高达 800ps,那么从 memory 到寄存器数据端的 timing path 就很容易出现 timing violation。这个时候需要设置 set_clock_latency,而且是一个负值。

之前在微信群上看到有个朋友问到为何要设置 set_clock_latency 值,今天就顺便做一个延伸。其实目的就是为了借 timing,让 timing 能够符合设计要求。之所以设置负值是为了让工具进行最大程度的 data path 优化。

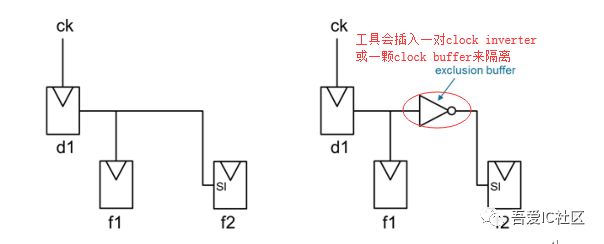

2.【典型的时钟树案例】已知 d1 为 generated clock 寄存器,d1 寄存器的输出分别到 f1 的 CK 和 f2 的 SI。这是一个 clock 和 data mix 的场景,在数字 IC 后端实现中非常常见。

此时,容易出现 SI 端的 max transition 问题,经常能看到若干 ns 的 violation。

常见处理方法

-

将 SI 端设置 exclude pin

-

将 SI 这段的 timing arc disable 掉

-

设置 set_clock_sense -stop_propgation 。值得注意的是图中的 exclusion buffer 其实是 clock buffer 或者 clock inverter,这个从工具做出来的 cts 结果可以看到。不要认为为何 data 上有 clock buffer,这颗 buffer 是用来隔离用的,一般也就是多这一级。

- 提问:星主,请问含有 occ 结构,分段做 tree,该从何入手?

【点评】先分析结构,然后在需要的地方,create_clock,并设上 floating pin 即可。

OCC 实现案例分享,请查阅这篇文章。数字后端设计实现之时钟树综合实践篇

- 提问:请教星主一个问题,怎么手解决 max fanout ,insert_buffer - divide_load 命令废弃了,我用的是 icc2016。

【点评】还记得我之前分享过关于修 max fanout,max transition 的万能方法吗?而且特别好用!那就是用add_buffer_on_route。需要提醒的是,当在跨 hierarchical 的地方使用该命令时,需要额外增加一个port_punch选项。因为设计中很多时候一个 driver 所带的 fanout,可能并不在同一 hierarchical 下,此时用 add_buffer_on_route 命令可以自动进行 fanout 的分组,从而解掉 max transition violation。

- 提问:请问星如何判定一个 CTS 的好坏,现在的 CTS 技术层出不穷,撇开 Timing 不说,只关注 CTS 本身。

【点评】时钟树综合质量问题当属数字 IC 后端实现中最难的专题之一。新手往往不知道如何入手,建议多查阅小编的文章,看完后相信一定会有一个相对清晰的思路。Qualify CTS 主要从以下四方面进行评判。

-

Clock latency 最短,clock skew 最小。

-

common clock path 尽量长。

-

uncommon clock path 最短。

-

各路时钟树走向符合 physical location 。

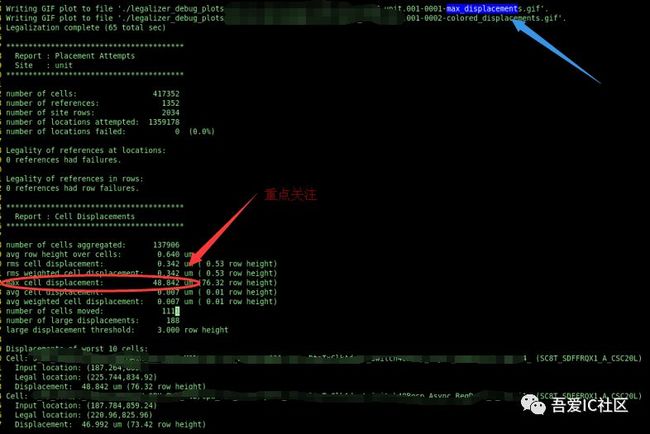

- 关于 ECO Route 阶段 leagalization 的 log,主要需要关注哪些信息?以及如何基于这些信息来判断 eco route 可能带来的影响?

【点评】不论是 fix timing 的 ECO Route,或者是 function eco 的 ECO Route,在工具做 leagalize 时,我们需要特别关注 cell 的max displacement(PR 实现各阶段其实都需要关注这个)。这个变量的值表征着 eco route 后可能所带来的的 timing 和绕线的影响程度。那么这个值多大是合理的呢?这个没有一个明确的数值,只能说越小越好,这样 eco route 后的影响是最小的。

对于高频电路设计实现来说,这个 max cell displacement 如果高于 50um,可能就会带来比较大的影响。但对于一个普通低频模块来说,可能它的数值超过 200um,它的绕线和时序都还是好的。不过有一点是肯定的,如果这个数值太大,往往会影响到 PR 工具和 PT 之间的 timing 一致性,从而影响到timing signoff 的迭代次数。

另外,我们还需要关注下 “avg cell displacement” 值,它是将所有 cell 移动的距离进行一个统计平均,没有被挪动的 cell 也参与了统计平均。因此,这个值正常都应该是在 0.00x—0.0xum 这个数量级。

新年福利

新年现金红包福利主要面向吾爱 IC 社区普通技术交流群和知识星球用户专用群。目前已经创建了一个知识星球会员专用群。由于该群人数已经超过 100 人,目前只能邀请加入了。凡是知识星球用户,可以私信小编微信(ic-backend2018),邀请入群。

抽奖日期:1 月 24 日

现金红包奖项设置

| 时间点 | 现金红包(元) | 数量(个) | 参与对象 |

| 12:00 | 20 | 6 | 所有 |

| 20:00 | 66 | 2 | 所有 |

| 21:00 | 88 | 2 | 知识星球会员 |

| 22:00 | 128 | 2 | 知识星球会员 |

| 23:00 | 168 | 2 | 知识星球会员 |

| 23:59 | 268 | 1 | 知识星球会员 |

抽奖方式

为了确保公平公正,现金抽奖方式仍然采用第三方抽奖工具,开奖方式为到指定时间自动开奖。邀请好友助力,可以大大增加获奖的概率。

抽奖条件

-

转发公众号或者知识星球任何两篇技术性文章或主题到朋友圈(中奖后再转发视为无效获奖)

-

不同时间节点,抽奖对象需要符合要求,否则视为无效。

-

同一个用户,允许重复获奖(即最高有机会获得千元现金红包大奖)。

抽奖二维码到时候会提前发布到微信群(提前一周左右放出抽奖二维码,请留意微信群通知)。主要有两个群,一个是普通技术交流群,另外一个是知识星球专用群。

除此之外,当天仍然会在两个微信群发放拼手气红包,希望大家踊跃参与。

知识星球活动

为了保证一个相对公平的环境,星球门票即日起临时从 228 元 / 年临时调整为 198 元 / 年,新用户可以通过长按下方二维码领取优惠券加入知识星球。名额有限,有需要的朋友,及时上车哦。

老用户续费

如果你是星球老用户,可以长按下方二维码领取优惠券进行续费。

小编知识星球简介(如果你渴望进步,期望高薪,喜欢交流,欢迎加入 ****):

在这里,目前已经规划并正着手做的事情:

-

ICC/ICC2 lab 的编写

-

基于 ARM CPU 的后端实现流程

-

利用 ICC 中 CCD(Concurrent Clock Data)实现高性能模块的设计实现

-

基于 ARM 四核 CPU 数字后端 Hierarchical Flow 实现教程

-

时钟树结构分析

-

低功耗设计实现

-

定期将项目中碰到的问题以案例的形式做技术分享

吾爱 IC 社区知识星球星主为公众号” 吾爱 IC 社区” 号主,从事数字 ic 后端设计实现工作近八年,拥有55nm,40nm,28nm,22nm,14nm等先进工艺节点成功流片经验,成功tapeout 过三十多颗芯片。

这里是一个数字 IC 设计实现高度垂直细分领域的知识社群,是数字 IC 设计实现领域中最大,最高端的知识交流和分享的社区,这里聚集了无数数字 ic 前端设计,后端实现,模拟 layout 工程师们。

在这里大家可以多建立连接,多交流,多拓展人脉圈,甚至可以组织线下活动。在这里你可以就数字 ic 后端设计实现领域的相关问题进行提问,也可以就职业发展规划问题进行咨询,也可以把困扰你的问题拿出来一起讨论交流。对于提问的问题尽量做到有问必答,如遇到不懂的,也会通过查阅资料或者请教专家来解答问题。在这里鼓励大家积极发表主题,提问,从而促进整个知识社群的良性循环。每个月小编会针对活跃用户进行打赏。

最重要的是在这里,能够借助这个知识社群,短期内实现年薪百万的梦想!不管你信不信,反正已经进来的朋友肯定是相信的!相遇是一种缘分,相识更是一种难能可贵的情分!如若有缘你我一定会相遇相识!知识星球二维码如下,可以扫描或者长按识别二维码进入。目前已经有415位星球成员,感谢这415**** 位童鞋的支持!欢迎各位渴望进步,期望高薪的铁杆粉丝加入!终极目标是打造实现本知识星球全员年薪百万的宏伟目标。

![]()

欢迎关注 “吾爱 IC 社区”

微信号:ic-backend2018

![]()

https://mp.weixin.qq.com/s/inO1_P65hFPjpKlwZOMolA