FPGA硬件工程师Verilog面试题(三)

✅作者简介:大家好我是:嵌入式基地,是一名嵌入式工程师,希望一起努力,一起进步!

个人主页:嵌入式基地

系列专栏:FPGA Verilog 习题专栏

网上关于嵌入式的面试练习网站很少,这里给大家推荐一款Verilog 在线刷题神器,从基础到大厂面试题点击跳转刷题网站进行注册学习

微信公众号:嵌入式基地

FPGA硬件工程师Verilog面试题(三)

- 习题一:4位数值比较器电路

- 习题二:4bit超前进位加法器电路

- 习题三:优先编码器电路

- 习题四:用优先编码器①实现键盘编码电路

- 习题五: 数据选择器实现逻辑电路

- 结束语

习题一:4位数值比较器电路

- 点击查看习题解析

描述

输入描述

- input [3:0] A

- input [3:0] B

输出描述

- output wire Y2 , //A>B

- output wire Y1 , //A=B

- output wire Y0 //A

代码实现

`timescale 1ns/1ns

module comparator_4(

input [3:0] A ,

input [3:0] B ,

output wire Y2 , //A>B

output wire Y1 , //A=B

output wire Y0 //A

);

wire W_y2[0:3];

wire W_y1[0:3];

wire W_y0[0:3];

genvar gen_i;

for (gen_i = 0; gen_i < 4; gen_i = gen_i + 1) begin

compare_1 compare_1_u(

.A (A[gen_i] ),

.B (B[gen_i] ),

.Y2(W_y2[gen_i]),//A>B

.Y1(W_y1[gen_i]),//A=B

.Y0(W_y0[gen_i]) //A

);

end

assign Y2 = W_y2[3] | ((W_y1[3]) & (W_y2[2])) | ((W_y1[3]) & (W_y1[2]) & (W_y2[1])) | ((W_y1[3]) & (W_y1[2]) & (W_y1[1]) & (W_y2[0]));

assign Y0 = W_y0[3] | ((W_y1[3]) & (W_y0[2])) | ((W_y1[3]) & (W_y1[2]) & (W_y0[1])) | ((W_y1[3]) & (W_y1[2]) & (W_y1[1]) & (W_y0[0]));

assign Y1 = W_y1[3] & W_y1[2] & W_y1[1] & W_y1[0];

endmodule

module compare_1(

input A,

input B,

output Y2,//A>B

output Y1,//A=B

output Y0 //A

);

assign Y2 = A & (!B);

assign Y0 = (!A) & B;

assign Y1 = !(Y2 | Y0);

endmodule

习题二:4bit超前进位加法器电路

- 点击查看习题解析

描述

输入描述

- 输入信号:

- A_in[3:0],

- B_in[3:0]

- C_1

- 类型:wire

输出描述

- 输出信号:

- S[3:0]

- CO

- 类型:wire

代码实现

module full_adder(

input A,

input B,

input C_i,

output S,

output C_o

);

assign S = A ^ B ^ C_i;

assign C_o = A & B | C_i&(a^b);

// assign C_o = A & B | A & C_i | B & C_i; // 也可以

endmodule

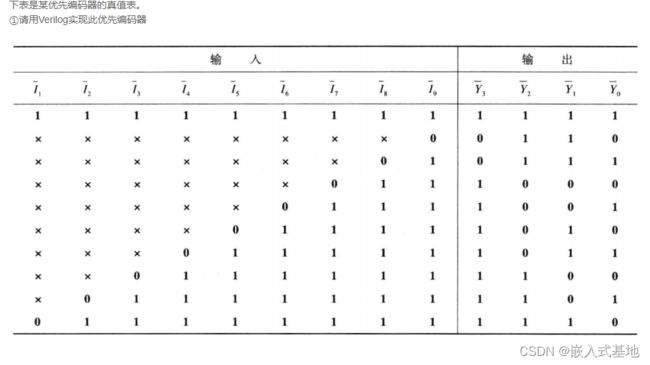

习题三:优先编码器电路

- 点击查看习题解析

描述

输入描述

- ①输入描述:

- input [8:0] I_n

输出描述

- ①输出描述:

- output reg [3:0] Y_n

代码实现

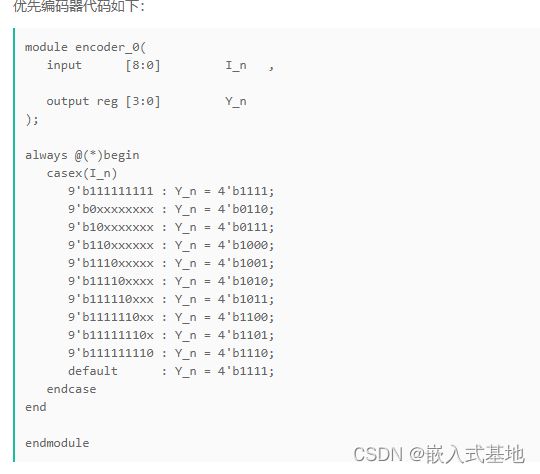

`timescale 1ns/1ns

module encoder_0(

input [8:0] I_n ,

output reg [3:0] Y_n

);

always@(*) begin

casez (I_n)

9'b1_1111_1111: Y_n = 4'b1111;

9'b0_????_????: Y_n = 4'b0110;

9'b1_0???_????: Y_n = 4'b0111;

9'b1_10??_????: Y_n = 4'b1000;

9'b1_110?_????: Y_n = 4'b1001;

9'b1_1110_????: Y_n = 4'b1010;

9'b1_1111_0???: Y_n = 4'b1011;

9'b1_1111_10??: Y_n = 4'b1100;

9'b1_1111_110?: Y_n = 4'b1101;

9'b1_1111_1110: Y_n = 4'b1110;

default: Y_n = 4'b0000;

endcase

end

endmodule

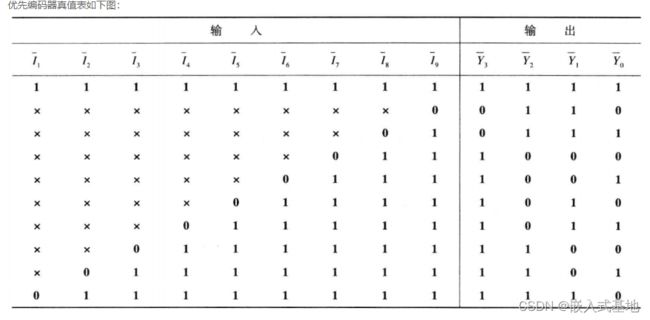

习题四:用优先编码器①实现键盘编码电路

- 点击查看习题解析

描述

-

请使用优先编码器①实现键盘编码电路,可添加并例化题目中已给出的优先编码器代码。

-

10个按键分别对应十进制数0-9,按键9的优先级别最高;按键悬空时,按键输出高电平,按键按下时,按键输出低电平;键盘编码电路的输出是8421BCD码。

-

要求:键盘编码电路要有工作状态标志,以区分没有按键按下和按键0按下两种情况。

输入描述

- input [9:0] S_n

输出描述

- output wire[3:0] L

- output wire GS

代码实现

`timescale 1ns/1ns

module encoder_0(

input [8:0] I_n ,

output reg [3:0] Y_n

);

always @(*)begin

casex(I_n)

9'b111111111 : Y_n = 4'b1111;

9'b0xxxxxxxx : Y_n = 4'b0110;

9'b10xxxxxxx : Y_n = 4'b0111;

9'b110xxxxxx : Y_n = 4'b1000;

9'b1110xxxxx : Y_n = 4'b1001;

9'b11110xxxx : Y_n = 4'b1010;

9'b111110xxx : Y_n = 4'b1011;

9'b1111110xx : Y_n = 4'b1100;

9'b11111110x : Y_n = 4'b1101;

9'b111111110 : Y_n = 4'b1110;

default : Y_n = 4'b1111;

endcase

end

endmodule

module key_encoder(

input [9:0] S_n ,

output wire[3:0] L ,

output wire GS

);

wire [3:0] L_temp;

encoder_0 encoder (S_n[9:1], L_temp);

assign GS = ~((&(~L)) & S_n[0]);

assign L = ~L_temp;

endmodule

习题五: 数据选择器实现逻辑电路

- 点击查看习题解析

描述

输入描述

- input A

- input B

- input C

输出描述

- output wire L

代码实现

`timescale 1ns/1ns

module data_sel(

input S0 ,

input S1 ,

input D0 ,

input D1 ,

input D2 ,

input D3 ,

output wire Y

);

assign Y = ~S1 & (~S0&D0 | S0&D1) | S1&(~S0&D2 | S0&D3);

endmodule

module sel_exp(

input A ,

input B ,

input C ,

output wire L

);

data_sel mySel(.S0(A), .S1(B), .D0(0), .D1(~C), .D2(C), .D3(1), .Y(L));

endmodule

结束语

你想要的牛客都有,各种大厂面试真题在等你哦!快快通过下方链接注册加入刷题大军吧!

刷题神器,从基础到大厂面试题点击跳转刷题网站