5、CPU Subsystem 01(5.1-5.7)

C297的框图

5、CPU Subsystem

本章描述在Aurix系列设备中找到的TriCore cpu的特定实现选项。

包括TriCore1.6P (TC1.6P)和TriCore1.6E (TC1.6E) cpu的详细信息。下表详细介绍了Aurix家族各个成员的CPU和本地内存配置。

本章应与TriCore架构手册一起阅读。

•建筑概述

•编程模型

•任务和职能

•中断处理

•陷阱

•内存保护系统

•时间保护系统

•浮点运算

•调试

•指令集

5.1 Aurix Family CPU configurations (Aurix家族CPU配置)

不同设备的CPU和本地内存配置的详细信息如下表所示:—

5.2 Central Processing Unit Features中央处理器特性

关键CPU功能包括:

•32位加载存储架构

•4g字节地址范围(232)

•16位和32位指令,减少代码大小

•数据类型:

-布尔型,带饱和的整数,位数组,有符号分数,字符,双字整数,有符号整数,无符号整数,IEEE-754单精度浮点数

•数据格式:

—位、字节(8位)、半字(16位)、字(32位)、双字(64位)

•字节和位寻址

数据、内存和CPU寄存器的小端字节顺序

•MAC指令:对偶16 × 16、16 × 32、32 × 32

•饱和整数算法

•包装数据

•寻址模式:

-绝对,循环,位反转,长+短,基+偏移与前和后更新

•指令类型:

-算术,地址算术,比较,地址比较,逻辑,MAC,移位,协处理器,位逻辑,分支,位域,加载/存储,打包数据,系统

通用寄存器集(GPRS):

—16个32位数据寄存器

- 16位地址寄存器

- 3个32位状态和程序计数器寄存器(PSW, PC, PCXI)

调试支持(OCDS):

- 1级,与CPS模块一起支持

- Level 3,配合MCDS块支持(仅限仿真设备)。

•灵活的记忆保护系统,提供多个保护集,每个保护集具有多个保护范围。

•时间保护系统,允许时间有限的实时操作

•大多数指令在一个周期内执行

•在1、2或3个周期内转移指令(使用动态转移预测)

•宽内存接口,快速上下文切换

•对于:子程序,中断,陷阱,自动保存和退出

•4个内存保护寄存器集

•双指令发布(并行到整数管道和加载/存储管道)

•仅用于循环指令的第三条管道(零开销循环)

•单精度浮点单元(兼容IEEE-754)

•Dedicated整数除法单位

•实现性能优化。

•16个数据保护范围,8个代码保护范围

•大多数指令在一个周期内执行

•在1或2个周期内转移指令(使用静态转移预测)

•宽内存接口,快速上下文切换

•对于:子程序,中断,陷阱,自动保存和退出

•4个内存保护寄存器集

•每个周期的单个指令问题

•单精度浮点单元(兼容IEEE-754)

•Dedicated整数除法单位

•实现优化的电源

•16个数据保护范围,8个代码保护范围

5.3 TC1.6P实现概述

5.3.1 CPU图表

CPU (Central Processing Unit)由指令取单元、执行单元、GPR (General Purpose Register File)、CPS (CPU Slave interface)和FPU (float Point Unit)组成。

5.3.2 Instruction Fetch Unit指令提取单元

指令提取单元预取来自64位程序内存接口(Program Memory Interface, PMI)的指令并对其进行对齐。在发布fifo中,指令按预测的程序顺序排列。发出fifo最多缓冲区六条指令,并将指令定向到适当的执行管道

指令保护单元检查对PMI的访问的有效性以及从PMI中获取的传入指令的完整性。

分支单元检查获取的指令是否具有分支条件,并根据先前的分支行为预测最有可能的执行路径。程序计数器单元(PC)负责更新程序计数器。

5.3.3执行单元

执行单元包含整数管道、加载/存储管道和循环管道。所有三条管道都是并行运行的,允许在一个时钟周期内执行多达三条指令。在执行单元中,所有指令都要经过一个解码阶段,然后是两个执行阶段。通过在管道阶段之间使用转发路径,允许一条指令的结果一旦可用,立即被下一条指令使用,从而将管道危险(停顿)降至最低。

5.3.4通用注册文件

CPU有一个通用寄存器(GPR)文件,分为地址寄存器文件(从A0到A15)和数据寄存器文件(从D0到D15)。向加载/存储管道发出指令的数据流通过地址寄存器文件进行引导。发送到/从Integer管道的指令和发送到load/store管道的数据加载/存储指令的数据流通过数据寄存器文件进行引导。

5.4 TC1.6E实现概述

5.4.1 CPU图表

CPU (Central Processing Unit)由指令取单元、执行单元、GPR (General Purpose Register File)、CPS (CPU Slave interface)和FPU (float Point Unit)组成。

5.4.2指令提取单元

指令提取单元预取来自32位程序内存接口(PMI)的传入指令半字并对其进行对齐。问题单元将单个对齐的指令指向适当的执行管道。指令保护单元检查对PMI的访问的有效性以及从PMI中获取的传入指令的完整性。程序计数器单元(PC)负责更新程序计数器。

5.4.3执行单元

执行单元包含整数管道和加载/存储管道。在TC1.6E中,循环指令总是由Load/Store管道执行。TC1.6E在每个时钟周期发出一条指令,因此在一个时钟周期内执行的指令不超过一条。在执行单元中,所有指令都要经过一个解码阶段,然后是两个执行阶段。通过在管道阶段之间使用转发路径,允许一条指令的结果一旦可用,立即被下一条指令使用,从而将管道危险(停顿)降至最低。

5.4.4通用注册文件

CPU有一个通用寄存器(GPR)文件,分为地址寄存器文件(从A0到A15)和数据寄存器文件(从D0到D15)。向加载/存储管道发出指令的数据流通过地址寄存器文件进行引导。发送到/从Integer管道的指令和发送到load/store管道的数据加载/存储指令的数据流通过数据寄存器文件进行引导

5.5 TC1.3.1功能变化总结

TC1.6P和TC1.6E cpu使用不同于TC1.3的管道组织。新管道组织的一个影响是将负荷-使用惩罚从0增加到1。这就需要重新调度代码以获得最佳性能。对现有TC1.3.1 CPU的其他重要调整如下:

•全流水线浮点单元(FPU)

-现在大多数浮点指令的重复率为1

•改进的调试系统-现在从保护系统解耦。

- 8个比较器证明多达4个范围,可选择的PC或负载存储地址

•扩展和增强的内存保护单元(MPU)

- 16个数据范围和8个代码范围。

•新的时间保护系统。

—防止任务运行时溢出。

•全新的安全保护系统。新PSW钻头安全识别的任务(PSW. s)

•改进中断和数据缓存操作支持的新指令。

-禁用,恢复,cachei。我

•快速整数除法的新指令

——DIV, DIV.U

•新的指示快速呼叫和返回与最低限度的状态保存。

——FCALLA FCALL FCALLI,烦恼

•引入长偏移寻址模式用于字节、半字和地址访问。

- ld.bu, ld.b, ld.hu, ld.h, st.b, st.h, st.a

•扩展范围的16位跳转

——JEQ JNE

•新的同步指令

——CMPSWAP。W, SWAPMSK。W

•新的CRC指令

——CRC32

•新的等待中断指令

- - - - - -等待

增加了系统地址映射的灵活性。

•完整的SECDED ECC保护所有刮痕,缓存和标签内存结构。

•Cache和Scratchpad内存系统现在完全分离。

-高速缓存内存可能被映射为额外的scratchpad。

•可选择的中断向量表大小(32字节/项,8字节/项)

5.6 CPU实现特性

介绍TC1.6P和TC1.6E cpu的具体实现特性。有关所有寄存器的完整描述,请参阅TriCore架构手册。

5.6.1环境保存区域/环境操作

CPU对函数调用、中断和陷阱使用统一的上下文切换方法。在所有情况下,任务的Upper Context是自动保存和恢复的硬件。保存和恢复较低的上下文可以选择执行软件。在TC1.6P中,上下文保存区域(CSA)和由显式上下文加载/存储指令(例如LDLCX)指定的地址可能被放置在DSPR或外部内存中(缓存或未缓存)。在TC1.6E中,上下文保存区域(CSA)和显式上下文加载/存储指令所指向的地址只能放在DSPR中。

CSA安置在DSPR

上下文操作的实际时间取决于上下文保存区域的位置。当将上下文保存区域放置在DSPR中时,可以获得最大的性能。在本例中,所有上下文保存和恢复操作需要四个周期。

CSA放置在缓存的外部内存(仅TC1.6P)

在这种情况下,时间也取决于数据缓存的状态。最好的情况是,当上下文保存不引起缓存线回写,并且上下文恢复命中数据缓存时,数据缓存操作发生。在本例中,所有上下文保存和恢复需要8个周期。

5.6.2程序计数器(PC)寄存器

程序计数器(PC)保存着当前被获取并转发到CPU管道的指令的地址。CPU自动处理PC的更新。软件可以使用PC的当前值进行各种任务,如执行代码地址计算。通过CPU执行的软件读取PC只能通过MFCR指令完成。这样的读取将返回MFCR指令本身的PC。不能通过MTCR指令显式地写入PC,因为CPU可能出现意外行为。只有当CPU停止运行时,PC才能被写入。

CPU不能执行Load/Store指令到Segment 15中PC的映射地址。此时会产生MEM trap。PC寄存器的0位是只读的,并且硬连线到0。

5.6.3存储缓冲区

为了提高性能,TC1.6P/E CPU实现了存储缓冲,将内存写操作与CPU指令执行分离开来。所有来自CPU的存储在写入本地内存或通过总线系统传输之前都被放置在存储缓冲区中。当目标内存或总线接口可用时,写入数据从存储缓冲区中取出并写入内存。在正常操作中,CPU将内存加载操作优先于存储操作,以提高性能,除非:

•存储缓冲区已满。

•加载到外围空间,存储到外围空间存在于存储缓冲区中。(按外围空间访问顺序)。

•加载或存储是原子操作的一部分。

通常,存储缓冲区的操作对最终用户是不可见的。如果在执行后续指令之前需要将数据写入内存,则可以使用DSYNC指令来刷新存储缓冲区。为了进一步提高性能,将对相同半字位置的连续字节写入合并到存储缓冲区中。TC1.6P CPU存储缓冲区最多可以保存6个存储的数据。TC1.6E CPU存储缓冲区可以容纳最多2个存储的数据。在设置SMACON时,可能会禁用存储缓冲区操作。IODT。在正常的执行中不应该这样做,因为这会严重限制性能。

5.6.4中断系统

中断请求可以由片上外设单元产生,也可以由外部事件产生。请求可以针对任何CPU。中断系统评估服务请求的优先级,并确定CPU是否应该接收请求。然后,最高优先级的服务请求通过中断的方式提交给CPU。

在接受一个中断时,CPU将向量到一个由中断优先级数和基本中断向量(BIV)生成的唯一PC。使用BIV[0],中断向量表中向量pc之间的间距可以选择为32字节或8字节。

TC1.6P和TC1.6E都实现了一个快速中断系统。这个系统避免了不必要的上下文保存和恢复操作,因此加快了中断程序的进入。快速中断被触发:

•中断正在等待

•从中断返回指令正在执行(RFE)

•挂起中断的优先级大于RFE执行时返回的优先级(ICR)。PIPN > PCXI.PCPN)。

•如果RFE被执行,中断将被启用。(PCXI。派= = 1)

•快速中断不会因为管道中存在MTCR指令或上下文操作而被禁用。

如果没有快速中断操作,RFE将导致上层上下文立即恢复,随后保存相同的上层上下文到完全相同的内存位置(最少8个周期)。快速中断系统用从保存的上下文负载PCXI/PSW/A10/A11(最小1周期)来替换这个冗余的恢复/保存序列。快速中断结束时的系统状态与标准的RFE/中断顺序相同。

5.6.5 Trap System陷阱系统

以下陷阱具有特定于实现的属性:

UOPC -未实现操作码(TIN 2)

UOPC陷阱在可选MMU指令,协处理器2和协处理器3指令上被引发。

OPD -无效操作数(TIN 3)

如果操作数说明符是奇数,CPU将对使用偶数寄存器对作为操作数的指令触发OPD陷阱。

数据访问同步错误(TIN 2)

DSE (Data Access Synchronous Bus Error) trap由DMI模块在CPU负载访问遇到某些错误条件时产生,例如总线错误或对DSPR的访问超出范围。当产生一个DSE陷阱时,错误的确切原因可以通过读取数据同步陷阱寄存器DSTR来确定。DSTR中可能出现的错误情况及对应的标志位请参见第5-103页“DMI Trap的产生”。

数据访问异步错误(TIN 3)

数据访问异步错误Trap (DAE)是由DMI模块产生的,当从CPU访问存储或缓存管理遇到某些错误条件时,如总线错误。当产生DAE陷阱时,可以通过读取Data Asynchronous trap Register (DATR)来确定错误的确切原因。关于DATR中可能出现的错误条件和相应的标志位,请参见第5-103页的“DMI Trap产生”。

PIE程序内存完整性错误(TIN 5)

当从本地内存或SRI总线取指令时检测到不可纠正的内存完整性错误时,将引发PIE陷阱。该陷阱与错误指令是同步的。陷阱是4类,TIN值为5。

在64位基础(TC1.6P)或32位基础(TC1.6E)上,程序内存被保护免于内存完整性错误。当试图执行来自任何包含内存完整性错误的取指令组的指令时,将引发PIE陷阱。可以询问PIEAR和PIETR寄存器来更精确地确定任何错误的来源。

DIE数据存储完整性错误(TIN 6)

当在对本地内存或SRI总线的数据访问中检测到不可纠正的内存完整性错误时,将引发DIE陷阱。陷阱是第4类,有6个TIN。DIE陷阱总是异步地独立于遇到错误的操作。如果装载/存储操作访问的任何内存半字(本地内存)或双字(SRI总线)包含不可纠正的错误,则会引发DIE陷阱。可以询问DIEAR和DIETR寄存器,以更精确地确定任何错误的来源。

MPX内存保护执行(TIN 4)

当一个程序试图从它没有执行权限的内存区域执行一条指令,并且启用了内存保护时,就会引发MPX陷阱。陷阱是第1类,TIN值为4。TC1.6E将指令的PC与内存保护系统定义的范围进行比较,以确定是否允许执行指令。TC1.6P将64位对齐的取组地址与内存保护系统定义的范围进行比较,以确定是否允许执行。

5.6.6内存完整性错误处理

TriCore cpu集成了对内存完整性错误检测和处理的支持。CPU中各种内存类型的内存完整性错误的处理如下:

5.6.6.1程序侧存储器

CPU的程序侧存储器由两种独立的存储器结构组成:-

程序暂存RAM (PSPR)和程序缓存(PCACHE)。在64位(TC1.6P)或32位(TC1.6E)的基础上,这两种内存结构都是ECC保护的,以防止内存完整性错误。PMI模块将从总线接口对PSPR的任何子宽度写访问转换为Read-Modify-Write序列。

程序随机存储器(PSPR)

CPU的Scratchpad RAM在64位(TC1.6P)或32位(TC1.6E)的基础上受到内存完整性错误的保护。ECC保护是通过MBIST ECCS寄存器启用的

对于从TriCore CPU到PSPR的指令取取请求,ECC位和数据位一起被读取,并和相应的指令一起传递给CPU。每当试图发出包含不可纠正的内存完整性错误的指令时,就会引发同步PIE陷阱。然后,陷阱处理程序负责纠正内存条目并重新启动程序执行。对于从总线接口(DMI模块或另一个总线主代理)读取操作的PSPR,如果访问导致检测到请求数据中的不可纠正的内存完整性错误,则会为总线事务返回一个总线错误。由于TriCore CPU可能不会参与事务,因此还会向SCU模块标记一个单独的错误,以可选地生成一个NMI陷阱返回给CPU。

对程序暂存板的写入只从总线接口执行。对于小于PSPR保护宽度的写操作,内存事务在PMI模块中被转换为一个读-修改-写序列。这样的写操作可能导致在读阶段检测到不可纠正的内存完整性错误,这些错误被作为标准读操作处理。

程序缓存(PCACHE)

CPU的Scratchpad RAM在64位(TC1.6P)或32位(TC1.6E)的基础上保护内存完整性错误。的ECC保护是通过MBIST ECCS寄存器启用的。从TriCore CPU取指令到PCACHE时,所有缓存方式的数据位和ECC位一起被读取,每一种缓存方式都产生一个不可纠正的错误信号。在标记命中的情况下,对应缓存方式的不可纠正错误信号连同它们的相应指令被传递给CPU。每当试图发出包含不可纠正错误的指令时,就会引发同步PIE陷阱。然后,陷阱处理程序负责检查内存完整性错误的来源。

程序标签(PTag)

ECC保护是通过MBIST ECCS寄存器启用的。对于从TriCore CPU到PCACHE的指令取请求,程序标记的ECC位与数据位一起被读取,并计算一个错误标志。点击触发方式只有在标签地址比较成功,有效位设置和ECC错误检测到相关标签的方式,任何其他结果被认为是一个小姐在正常情况下没有检测到错误的缓存方式高速缓存线路是正常/不停。在检测到错误的情况下,缓存控制器替换算法强制替换指示错误的方式。如果一种缓存方式标记缓存命中,而另一种缓存方式检测到不可纠正的ECC错误,则错误条件被掩盖,并且对内存完整性错误处理机制没有影响。

5.6.6.2数据侧存储器

TC1.6P CPU实现了数据暂存和数据缓存内存。TC1.6E实现了一个数据暂存内存,但将数据缓存替换为数据读缓冲区(DRB)。所有数据存储结构都是ECC保护,以每半字为基础,防止内存完整性错误。对DSPR或DCache (TC1.6P)的任何字节写访问都被转换为半字Read-Modify-Write序列。在正常操作中,对数据存储器独立的字节写事务不会导致额外的停止周期。

数据暂存存储器(DSPR)

TC1.6P和TC1.6E的DSPR内存在每半字的基础上都受到了内存完整性错误的保护。ECC保护是通过MBIST ECCS寄存器启用的。

从TriCore CPU向DSPR加载数据时,ECC位和数据位一起被读取,每个半字产生一个不可纠正的错误信号。如果检测到与传递给CPU的任何数据半字相关的错误,则会将错误标记到CPU。如果检测到这样的错误条件,将引发一个异步DIE陷阱。然后,陷阱处理程序负责纠正内存条目,或者在无法纠正数据时采取替代操作(如系统软复位)。对于从总线接口(PMI模块或另一个总线主代理)读取操作的DSPR,如果访问导致检测到所请求数据半字中的不可纠正错误,则会为总线事务返回一个总线错误。由于TriCore CPU可能不会参与事务,因此还会向SCU模块标记一个单独的错误,以可选地生成一个NMI陷阱返回给CPU。对于半字或大于半字的DSPR写操作,预先计算ECC位,并与数据位并行写入内存。对于字节写操作,内存事务在DMI模块内被转换为半字读-修改-写序列。因此,字节写操作可能会导致检测到不可纠正的内存完整性错误,这些错误按照标准的读操作进行处理。

数据缓存(DCache) -仅TC1.6P

ECC保护是通过MBIST ECCS寄存器启用的。

对于从TriCore CPU向DCache加载数据的请求,两种缓存方式的数据位同时读取ECC位,并为每种缓存方式的每个半字计算一个不可纠正的错误标志。在这种情况下,用缓存的方式检测到任何请求的数据半字有一个相应的标记命中,一个错误被标记到CPU。如果检测到这样的错误条件,将引发一个异步DIE陷阱。然后,陷阱处理程序负责纠正内存条目,或者在无法纠正数据时采取替代操作(如系统软复位)。

对于半字大小或更大的写操作,检查位被预先计算并与数据位并行地写入内存。对于字节写操作,内存事务在DMI模块内被转换为半字读-修改-写序列。因此,字节写操作可能导致检测到与读操作相同的不可纠正的内存完整性错误。

对于cache线回写,当脏数据被转移到存储缓冲区时,将执行不可纠正的错误检测。在所有情况下(正常缓存线回收,cachexxx指令),当在有效缓存线中检测到错误条件时,将引发DIE陷阱。

由于无法对数据进行校正,因此陷阱处理程序负责采取纠正措施(如系统软复位)

数据标签(DTag) -仅TC1.6P

ECC保护是通过MBIST ECCS寄存器启用的。

当TriCore CPU向DCache发送数据加载或存储请求时,数据标签的ECC位和数据位一起被读取,并计算一个不可纠正的错误标志。点击触发方式只有在标签地址比较成功,标签的位置是有效的,在相关的标签没有无法改正的错误检测,其他结果被认为是一个小姐在正常情况下均未检测到错误标签的方式高速缓存线路是正常/不停。在缓存丢失的情况下,当用一种标记方法检测到错误且缓存线不包含脏数据时,缓存控制器替换算法强制在重新填充操作返回时替换指示错误的方法。在一种缓存方法标记缓存命中,而另一种方法检测到不可纠正的错误的情况下,错误条件被掩盖,并且对内存完整性错误处理机制没有影响。如果发生缓存丢失,并且在相关的数据标记方式上检测到不可纠正的错误,并检测到脏数据,则向CPU发送异步DIE陷阱,并终止任何回写/重新填充序列。trap处理程序负责使高速缓存线路失效,并在可能的情况下处理任何相关的脏数据,或采取其他纠正措施。使用缓存操作指令对强制缓存回写采取了类似的操作。

5.6.6.3 Memory Initialisation内存初始化

为了避免产生假的ECC错误,PSPR必须在使用前完全初始化。这可以通过软件或硬件自动完成(详见PMU PROCOND寄存器)。无论为衍生产品生产的任何内存大小变体,第5.1章中详细描述的整个物理内存都必须初始化。

5.6.7 WAIT Instruction等待指令

WAIT指令将暂停执行,直到发生以下事件之一。

•屏敝中断

•异步陷阱

•闲置请求

•暂停请求

•异步调试暂停或Trap请求

5.6.8 Instruction Memory Range Limitations指令内存范围限制

为了确保处理器核心提供了一个恒定的指令流,指令提取单元将推测地从当前PC之前的64字节中提取指令。

如果当前PC在指令内存顶部的64字节内,指令提取单元可能尝试从物理内存范围以外的地方推测取指令。这可能会导致总线和存储系统触发错误条件和警报。

因此,建议任何内存的上64字节都不用于指令存储。

5.6.9 Atomicity of Data Accesses数据访问的单元性

数据对齐规则以及每种访问类型的总线事务数在下表中详细说明:-

当从任何总线主服务器查看数据时,单个访问导致单个总线事务的情况下会保留数据的原子性。如果单个访问导致多个总线事务(在上表中标记为“*”),则需要考虑单元性。在这些访问中,另一个总线主程序可以在完成访问所需的总线事务之间读取或写入目标内存位置。

在对SRI总线的字和双字访问的情况下,对于自然对齐的数据值,总线事务的数量将为1,因此原子性将被保留。

5.6.10 A11用法

在正常使用中,A11总是包含下一个RET或RFE指令的目标。处理器利用这个事实在执行RET/RFE指令之前推测地加载返回目标。修改A11的代码(例如测试代码)应该知道存储在A11中的任何值都可能被用作这种推测的目标。如果A11中的值不是一个有效地址,推测可能会导致总线和存储系统触发错误条件和警报。

因此,建议A11只包含有效的地址值。

5.7 Memory Addressing内存寻址

本章详细介绍了CPU的具体寻址。

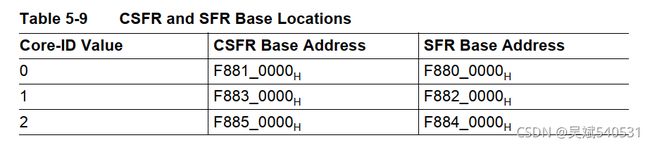

5.7.1 CSFR and SFR base Locations CSFR和SFR位置

每个CPU都有一组专用的控制寄存器和状态寄存器,这些寄存器访问的地址如下表所示。这些寄存器分为特殊功能寄存器(SFRs)和核心特殊功能寄存器(csfr)。

CPU必须使用MTCR和MFCR指令访问自己的CSFR寄存器。其他cpu的CSFR寄存器可以通过XBAR_SRI使用加载和存储指令来访问。

任何CPU的SFR寄存器只能通过XBAR_SRI使用加载和存储指令来访问。目前,CPUx的覆盖控制寄存器和访问保护寄存器被映射到CPUx SFR地址范围。

TC1.6P和TC1.6E SFR和CSFR寄存器的基本位置如下:-

5.7.2 Local and Global Addressing本地和全局寻址

TriCore架构支持紧密耦合的程序和数据SRAM存储器,称为程序Scratch Pad RAM (PSPR)和数据Scratch Pad RAM (DSPR)。本地PSPR内存总是位于C0000000H。本地DSPR始终位于D0000000H。

在多处理器系统中,本地的临时存储器出现在全局地址映射中的以下位置:-

cpu总是将全局地址用于总线事务。因此,从C0000000H (cpu本地PSPR)加载数据将导致一个地址范围为50100000H - 701FFFFFH的总线事务,具体取决于处理器的Core-ID值。

类似地,从D0000000H (cpu本地DSPR)获取代码将导致一个地址范围为50000000H - 700FFFFFH的总线事务,具体取决于处理器的Core-ID值。

5.7.3缓存访问

缓存和标记内存可以映射到cpu地址空间。当映射时,高速缓存存储器与DSPR/PSPR存储器相连,具体如下表所示。当映射时,高速缓存存储器的行为与PSPR/DSPR存储器相同,可以用作标准存储器。

缓存和标记内存到TriCore地址空间的映射是由MTU_MEMMAP寄存器控制的。详细信息请参见MTU章节。