DNNBuilder: an Automated Tool for Building High-Performance DNN Hardware Accelerators for FPGAs

题目:DNNBuilder: an Automated Tool for Building High-Performance DNN Hardware Accelerators for FPGAs

时间&会议: 2018 IEEE/ACM International Conference on Computer-Aided Design (ICCAD)

开源代码:IBM/AccDNN: A compiler from AI model to RTL (Verilog) accelerator in FPGA hardware with auto design space exploration. (github.com)

This work was published in ICCAD’18, and won the Best Paper Award for Front-end

加速器的设计策略分两种:基于循环的架构(统一的计算单元在不同的时间被不同的层利用);基于流水线的架构(网络中的每个层是一个单独的流水线阶段)

选择流水线架构的原因:

- 边缘设备没有足够的内存和带宽缓存基于循环架构中的中间数据

- 循环架构中的统一架构不够灵活,需要对不同层进行转换降低了性能

- 流水线架构可以更好的分配资源实现高吞吐量以便支持流输入

比较独特的贡献:

-

细粒度基于层的流水线架构减少流水线架构启动延迟;(有多细?怎么减少延迟?)

-

基于列的缓存方案减少阶段间的缓存空间开销;(基于列是什么?有什么好处?)

为高清图像/视频输入提供毫秒级的响应,可在延迟敏感的系统上部署DNNBuilder生成的DNN加速器成为可能(之前的加速器不行吗?)

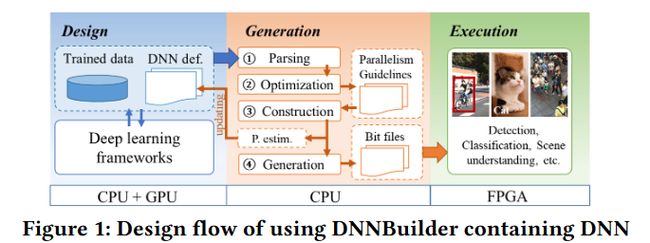

Automation Design flow

- Design step: 使用深度学习框架设计网络并训练得到网络的定义文件(“

DNN def.”)和训练得到的权重;- 设计阶段里的一个重要的特征是接受了来自Generation阶段对性能进行评估的feedback结果(“

P. estm.”),当运行速度或资源花销达不到我们预期,我们就要通过调整量化方案或者网络模型等方法达到我们的性能要求。

- 设计阶段里的一个重要的特征是接受了来自Generation阶段对性能进行评估的feedback结果(“

- Generation step: 脚本文件进行network parsing, map to pre-built RTL components ⟹ \Longrightarrow ⟹ automatic resource allocation scheme to balance pipeline(kernel/channel parallel factors and buffer sizes) ⟹ \Longrightarrow ⟹ network construction:根据RTL网络组件、数据流控制器和内存实例构建DNN实现 ⟹ \Longrightarrow ⟹ Code generation:生成FPGA上的加速器实例(bit流文件)

- Execution step: 实例化的加速器有FIFO类似的输入输出的数据接口和权重接口连接片外存储控制器,通过这些接口执行模型加速器得到结果

Accelerator Architecture Design

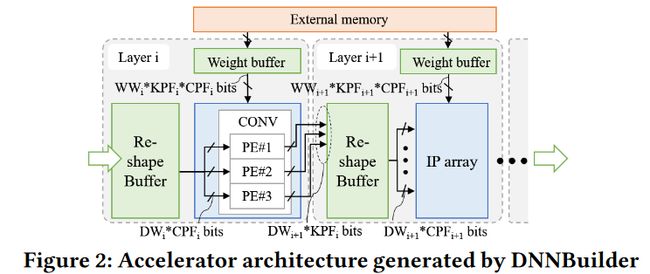

两层conv的例子:

一些概念:

-

Channel Parallelism Factor (CPF) :特征图的通道并行因子(通道数量)

-

Kernel Parallelism Factor (KPF):卷积核并行因子(卷积核的数量)

-

D W i DW_i DWi : input data bit-width

-

W W i WW_i WWi: weight bit-width

Computation Engine Design

不同的卷积核进行并行计算,每个卷积核安排一个MUL&ADD, 同时输出通道方向上的output

之前的工作:

- 同一个卷积核在特征图水平方向上的不同特征点卷积,同时输出水平方向上的output

- 所以存在PE之间水平方向的data forward

- 以及PE内部列方向上的data fifo缓存数据

ON-Chip/Off-Chip Memory Management

基于列的缓存方案:

-

特征图上一个卷积核width数量的Slice是一个Column

-

DNNBuilder 至少缓存两列,这样在完成一列后可以立即开始第二列的滑动窗口的计算

-

Slice1空间释放后,Slice5将被缓存形成下一个Column

这样做的优势?

- 大多数输入的图像的高度小于宽度,在列方向缓存Slice有利于节省on-chip存储(行方向缓存,宽度大,数据长就需要存的数据更多;我把图片转90度输入岂不是基于行的缓存方案?)

- 提高了低computation-to-communication (CTC) ratio的层的性能,例如小特征图输入的卷积层、FC层,它们存取数据的花销大,计算的花销小

自适应存储层次系统:

-

权重缓冲区:dual-port RAMs in FPGA

-

reshape buffer: 提供特征图输入

-

external memory:提供片外存储

-

ping-pong buffers:在层的输入处提供可选的乒乓缓冲区;

- 所需的权重超过一定的阈值,数据需要片外存储,自动生成乒乓缓冲区,克服从外部存储器获取数据时的数据短缺问题

- 反之,当用户开发一个低位宽量化DNN时,当所需数据的大小低于阈值时,将不会产生乒乓。

- (乒乓缓冲区是什么?数据流控制的处理技巧,一个缓冲区用于存放输入,一个缓冲区用于取出输出)

Automatic Resource Allocation

通过考虑网络的复杂性,片外存储访问带宽和数据重用,给每个层生成并行方案(决定CPF和KFP的值)以及数据缓冲区的大小

Theoretical Guideline

需要的计算资源: C i C_i Ci

分配的资源(dsp的数量): R i R_i Ri

硬件工作频率相关的比例常数: α \alpha α

第 i i i 层的延迟: L i L_i Li

公式(1)说明分配的资源越多,层的延迟越小

整体吞吐量throughput: T P TP TP

公式(2)说明整体吞吐量取决于延迟最大的那个层(瓶颈)

公式(3)提供了最理想的状况:所有层的延迟相同,工作负载完全相同,吞吐量最大

Memory Bandwidth Adjustment

斜率是带宽

计算通信比(CTC)小的时候,蓝色部分;性能受限于存储访问的延迟,通信需求大,计算需求小,数据复用少

CTC大的时候,灰色部分,性能受限于计算资源,计算需求大,数据复用多,带宽不是瓶颈。

优化设计的目标是:用最少的带宽资源和要求的CTC达到最大吞吐量

优化的方案:通过调整数据重用的行为改变CTC,从而缓解带宽的要求

首先按照公式(3)求出分配的计算资源 R i R_i Ri,根据DNN各层的数据重用行为确定CTC比

(a)先给FC分配带宽,如果带宽无法满足,需要feedback步骤重设计采取更激进的量化方案;

(b)剩下的带宽给CONV层分配

©CONV i&j层被存储访问的延迟限制了,就需要缓存更多的column,得到更高的CTC后CONV层就被计算资源限制

(d)CONV i&j层没有被存储限制但是被带宽限制了,调整带宽需求最高的层(CONV i),通过缓存相应特征映射的更多列来减少其带宽使用(斜率变缓)

Allocation Algorithm in DNNBuilder

计算资源分配算法:

并行系数必须是2的幂,对瓶颈层j分配多一倍的计算资源

根据Ri计算CPF和KPF

存储带宽资源分配算法:

- 初始化

卷积剩余可用存储带宽 B W t o t a l c o n v BW_{total}^{conv} BWtotalconv

特征图reshape可用片上存储资源 m e m t o t a l r b mem^{rb}_{total} memtotalrb

单个DSP的带宽 B W R BW_R BWR

PF表示并行因子等于Ri

- 首先满足分配计算资源的带宽需求:

R i × B W R R_i\times BW_R Ri×BWR :dsp数量与单个dsp的带宽相乘得到带宽总和

H i o u t × C o l i H_i^{out}\times Col_i Hiout×Coli : 特征图高度与缓存列数(宽度)相乘,特征图的数据在这两个方向上复用了

它们相除得到根据计算资源Ri分配所需的深度方向的带宽

- 要求的带宽超过总可用带宽:while1循环

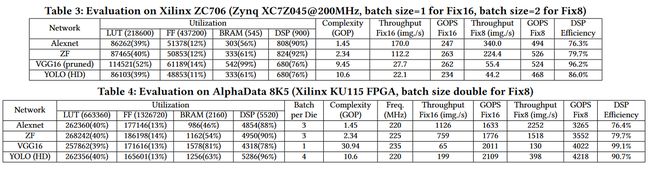

Experiment

FPGA

-

XC7Z045 in Xilinx ZC706,

-

KU115 in AlphaData 8K5

Test DNN model: Alexnet ZF VGG16 YOLO

为了满足实时性VGG16砍掉了一半的卷积和池化层且使用4bit位宽量化权重

准确率:

f.t表示feedback,()内箭头表示正则化后的提升

资源利用率和性能:

性能峰值在嵌入式FPGA中为526个GOPS,在高端FPGA中为4218个GOPS

引入DSP效率来展示所分配的DSP的实际和理论最大性能之比:

分母等于在给定频率下分配的DSP提供的理论最佳性能。分子表示实际实现的性能(GOPS);VGG16加速器DSP效率最高:VGG16具有统一的CONV (3×3 with stride 1)和pooling pattern (2×2 with stride 2),使得在Ri为2的幂的约束下,方程(3)完全满足。每层时延越均衡,DSP效率越高

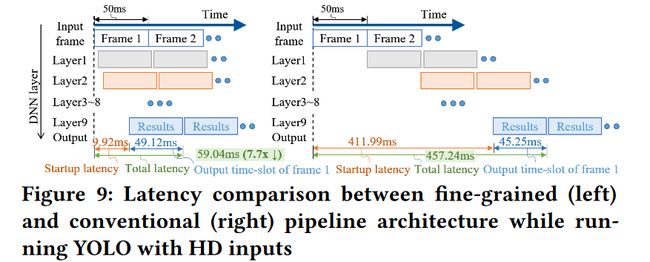

20FPS(frame delay=50ms),1280×384相机的实施输入

startup latency is 9.92ms,

keeps generating outputs until 9.04ms

output time-slot” which lasts 50+9.04-9.92=49.12ms

细粒度的基于层的管道架构的优点:

隐藏数据传输延迟(在第一个帧仍在加载时生成输出),并交付一个小的启动延迟(在本例中为9.92ms)

传统的管道架构(右图)具有20帧/秒的总体吞吐量,承受457.24毫秒的延迟

在收集i层的几列输出特征图后开始运行第i + 1层管道阶段,我们的延迟为59.04ms,实现7.7倍减少

基于列的缓存的优势:

显著降低了保存DNN特征图所需的BRAM;YOLO加速器中只实例化了137个bram,而不是在传统的管道设计中实例化5920个bram,总体BRAM减少为5920 ÷ 137 = 43x

Comparison to FPGA & GPU Accelerators

[1] J. Qiu et al. Going deeper with embedded FPGA platform for convolutional neural network. In FPGA, 2016.

[2] Q. Xiao et al. Exploring heterogeneous algorithms for accelerating deep convolutional neural networks on FPGAs. In DAC, 2017.

[5] U. Aydonat et al. An OpenCL deep learning accelerator on Arria 10. In FPGA, 2017.

[6] J. Zhang et al. Improving the performance of OpenCL-based FPGA accelerator for convolutional neural network. In FPGA, 2017.