ICC---data setup

ICC—data setup

数据准备

ICC开始布局布线之前,应该检查输入数据准备是否完整,主要包括:

- MilkWay参考库

信息是以被称为“views”的形式存储的,例如:

- CEL:完整的版图信息

- FRAM: 用于布局布线的抽象化的版图物理信息(只有单元大小,端口名称,端口位置等简单的物理信息)

- LM: 带有时序和功耗信息的逻辑模型(可选*),该文件对于后端布局布线不是必须的,ICC只是通过link_library变量读取指定的(.db)格式的逻辑库。

对于那些标准单元库,IO库,Memory或者其他macro,如果设计中没有CEL View以及FRAM view,则可以在Milkway软件中通过简单的read_def文件的方式生成这些文件。

- 工艺库文件(.tf file)

每种工艺对应一个唯一的工艺文件,包含金属层次对应的工艺参数:

- 每个层次/via对应的编号以及名字

- 工艺的介电常数

- 每个冗层次/via的物理和电学特性

- 每个层次/via的设计规则(最小线宽以及最小线间距等)

- 单位及精度

- 用于显示的每层对应的颜色及模式

- TLUplus文件

寄生RC查找表,ICC使用网络几何形状以及该文件来计算互联电阻电容。

若tluplus文件没有时,可由foundry给的.itf转成tluplus。使用的是Synopsys公司的star_RC. - db文件(.db file)

用于提供STD Cell,IO, Macro的时序.功耗.面积等信息。 - 门级网表(.v file)

- 时序约束文件(.sdc file)

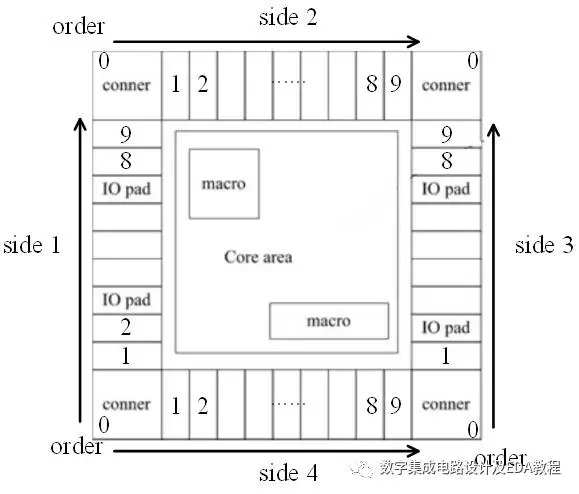

管脚排列文件(.tdf file)

该文件主要用来定义设计中所有IO以及IO Corner的位置(上下左右的方位以及排列顺序,也可以定义具体的坐标)。

该文件可以参照ICC中的set_pad_physical_constraints命令的文件语法进行编写,也可以在ICC中导出一个该文件进行手工修改。

库设置文件(.synopsys_dc.setup)

g该文件可以放置在ICC软件启动目录,软件在启动时会自动加载search_path,target_library,link_library这些库,或者可以将这些设置单独存为一个脚本,在每次打开ICC的时候都手动source该脚本,该脚本内容与DC中用的启动文件完全一样.

参考库的创建—Milkway软件

在开始后端布局布线之前准备好各种参考库文件,所有的文件均为Milkway格式。参考库的创建可以使用synopsys的Milkway来实现。在Milkway中用read LEF文件的方式创建Milkway参考库。

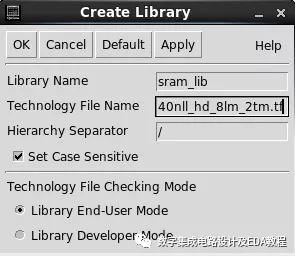

首先,创建库,在菜单栏中选中

“library”--->"Create",在“library Name”中填入创建参考库的名字,“technology file name”中填写工艺库文件的路径,并选中“setCase Sensitive”区分大小写。

菜单栏中选择“Cell Library”⟶“LEF In”,“Library Name”后边通过点击“Browse”选择刚才创建的参考库,“Tech LEF Files”选择工艺的LEF文件路径,“Cell LEF Files”选择Cell的LEF文件。其他选项默认即可。点击OK之后就会在参考库目录内生成CEL和FRAM两个文件夹,这两个便是创建的CEL View和FRAM View。

OK之后,将会在参考库目录下生成CEL和FRAM两个文件夹,这两个文件夹便是创建CEL View和FRAM view。

随后,进行电源地端口的声明,即输入命令:dbSetCellPortType “libname” “cellname” ‘({(“portName” {“type”}..)…}) append ?

下面以一个SRAM为列子提供创建参考库的脚本:

################################################

cmCreateLib

setFormField"Create Library" "Library Name" "sram_lib"

setFormField"Create Library" "Technology File Name""scc40nll_hd_8lm_2tm.tf"

setFormField"Create Library" "Set Case Sensitive" "1"

formOK "CreateLibrary"

read_lef

formButton "ReadLEF" "browse..."

setFormField "ReadLEF" "Library Name" "sram_lib"

setFormField "ReadLEF" "Tech LEF Files" "scc40nll_8lm_2tm.lef"

setFormField "ReadLEF" "Cell LEF Files""sadslsck41p1568x32m8b1w0c0p0d0t0.plef"

formOK "ReadLEF"

dbSetCellPortTypes"sram_lib" "sadslsck41p1658x32m4b1w0c0p0d0t0"'(("VDD""Power")("VSS" "Ground")) 常用文件格式说明

- GDSII:

它是用来描述掩模几何图形的标准,是二进制格式,内容包括层和几何图形。 - CIF:

(Caltechintermediate format),叫caltech中介格式,是另一种基本文本的掩模描述语言。 - LEF:

(Library exchangeformat),叫库交换格式,它描述了库单元的物理属性,包括端口位置、层定义和通孔定义。它抽象了单元的底层几何细节,提供了足够的信息,以便允许布线器在不对内部单元约束来进行修订的基础上进行单元连接。它包含了工艺的技术信息,如布线的层数、最小的线宽、线与线之间的最小距离以及每个被选用cell,BLOCK,PAD的大小和pin的实际位置。cell,PAD的这些信息由厂家提供的LEF文件给出,自己定制的BLOCK的LEF文件描述经ABSTRACT后生成,只要把这两个LEF文件整合起来就可以了。 - DEF:

(Design exchangeformat),叫设计交换格式,是ASCII格式的文件,它描述的是实际的设计,对库单元及它们的位置和连接关系进行了列表,使用DEF来在不同的设计系统间传递设计,同时又可以保持设计的内容不变。DEF与只传递几何信息的GDSII不一样。它可以将设计的逻辑信息和物理信息传递给布局布线工具。逻辑信息包括逻辑连接关系(由网表表示)、grouping信息以及物理约束。物理信息包括布局规划、布局位置及方向、绕线几何数据。 - SDF:

(Standard delayformat),叫标准延时格式,是IEEE标准,它描述设计中的时序信息,指明了模块管脚和管脚之间的延迟、时钟到数据的延迟和内部连接延迟。 - SDC:

(Synopsys delayconstraint),叫Synopsys延时约束文件。 - DSPF、RSPF、SBPF和SPEF:

DSPF(detailed standard parasitic format),叫详细标准寄生格式,属于CADENCE公司的文件格式。

RSPF(reducedstandard parasitic format),叫精简标准寄生格式,属于CADENCE公司的文件格式。

SBPF(synopsys binary parasitic format),叫Synopsys二进制寄生格式,属于SYNOPSYS公司的文件格式。

SPEF(standard parasitic exchange format),叫标准寄生交换格式,属于IEEE国际标准文件格式。

以上四种文件格式都是从版图中提取出来的寄生RC信息,是在寄生参数提取工具与时序验证工具之间传递RC信息的文件格式。 - ALF:

(Advanvedlibrary format),叫先进库格式,是一种用于描述基本库单元的格式,它包含电性能参数。 - PDEF:

(Physical designexchange format),叫物理设计交换格式。它是SYNOPSYS公司用在前端和后端工具之间传递信息的文件格式。描述了与单元层次分组相关的互连信息。这种文件格式只有在使用SYNOPSYS公司的Physical Compiler工具才会用到,而且130 nm以下工艺基本都会用到该工具。

Milkway数据库

Milkway库文件包括

- 技术文件 technology file

- CLF (Cell library Format)

- TDF文件,通常包括pin和port

- GDSII文件

- 网表文件,verilog, VHDL,EDIF

- SDC文件(Synopsys design Constraints),时序约束文件

- 设计数据库文件,标准的Synopsys.db文件,包括网表,时序和设计规则约束

- 综合库文件.lib或.db,包含单元时序和功能信息

Milkway库目录

Lib二进制文件,可以通过geCreateLib命令或Library>Create来产生,这个文件包括了该数据库中其它元素的目录。工具可以通过这个文件来跟踪库结构和内容。该文件不能够被编辑但是可以通过Milkyway命令来加载和去除文件,如技术文件和CLF文件。

Milkyway库可分为以下几类

1. 几何物理数据 :

- CEL 物理数据,该目录包含所有导入到该数据库中的物理数据,或者是有Astro产生的物理数据

- FRAM 从CEL中提取出的Placement和routing的数据

- SMASH 打平的CEL物理版图数据

- HTV CEL的层次时序信息,类似于其它Synopsys工具中的接口逻辑模型

2. 时序, 功耗和逻辑

- LM 时序,功耗和逻辑信息

- PWR 功耗信息

- TIM 时序信息

3. 网表

- LOGIC 时序约束时钟定义,来自于DC综合的网表信息

- NETL 层次化的网表信息输入进来的Verilog网表中的每个模块被以二进制文件的形式存储在NETL目录中,或是等效于VHDL或EDIF网表

- EXP 打平的flattened,网表数据

- HNET 层次化的网表信息

4. 其它

- PARA 寄生RC数据来自于Astro ,Star-RCXT或第三方的提取工具的RC寄生参数

- CONN 内部宏单元电源和地的互连信息。

- ERR 来自于DRC和LVS的结果文件

- FILL 布线填充fill数据

- GAP 布线间隙gap数据

- NOTC 布线槽数据

- ROUTE astro分布式布线产生的布线结果数据

IO库与标准单元库中特殊单元

- 填充单元 Fill Cell IO Filler是用来填充I/O单元和I/O单元之间的间隙。 对于 标准单元则同样有标准填充单元(STD fillercell),它也是单元库中定义的与逻辑无关的填充物,它的作用主要是把扩散层连接起来满足DRC规则和设计需要,并形成电源线和地线轨道(power rails)。

- 电压钳位单元 TIE Cell 数字电路中某些信号端口,或闲置信号端口需要钳位在固定的逻辑电平上,电压钳位单元按逻辑功能要求把这些钳位信号通过钳高单元(tie-high)与Vdd相连,或通过钳低单元(tie-low)与Vss相连使其维持在确定的电位上。用来对那些需要接到固定逻辑电平上的MOS管的栅极进行ESD保护。

- 二极管单元 为避免芯片加工过程中的天线效应导致器件栅氧击穿,通常布线完成后需要在违反天线效应规则的栅输入端加入反偏二极管,这些二极管可以把加工过程中金属层积累的电荷释放到地端以避免器件失效。

- 去耦单元 当电路中大量单元同时翻转时会导致充放电瞬间电流增大,使得电路动态供电电压下降或地线电压升高,引起动态电压降(IR-drop),为避免动态电压降对电路性能的影响,通常在电源和地线之间放置由MOS管构成的电容,这种电容被称为 去耦电容或去耦单元(decap cell),他的作用是在瞬态电流增大、电压下降时给电路补充电流以保持电源和地线之间的电压稳定,防止电源线的电压降和地线电压的升高。去耦单元是与逻辑无关的附加单元。

- 时钟缓冲单元 时序电路设计的一个关键问题是对时钟树的设计,芯片中的时钟信号需要传送到电路中的所有时序单元。为了保证时钟沿到达各个触发器的时间偏差(skew)尽可能地小,需要插入时钟缓冲器减小负载和平衡延时,在标准单元库中专门设计了供时钟树选用的时钟缓冲单元(clock buffer)和时钟反向器单元(clock inverter),时钟树综合工具根据指定的时钟缓冲单元去自动构建满足时序要求的时钟网络。时钟缓冲单元是专用的逻辑单元。

- 延时缓冲单元 延时缓冲单元的作用与时钟缓冲单元相类似,它是为了调节电路中的一些路径的延时以符合时序电路的要求而设计。例如:在同步电路设计中通常采用添加延时缓冲单元的方法来保证复位信号到达各个触发器的时间相同,避免因复位信号不一致而导致系统逻辑的混乱。同时在后端设计中如果存在保持时间的违反,也可以插入该单元来解决。

- 阱连接单元(well-tap cell)阱连接单元属纯物理单元,没有任何逻辑功能和时序约束,主要用于限制电源或地与衬底之间的电阻大小,减小闩锁效应。它是近年来在130 nm或更加先进的工艺低功耗设计中新增加的一种特殊单元。

- 电压转换单元 电压转换单元(level shifter)是近年来在90 nm或更加先进的低功耗设计中新增加的一种特殊单元,用于低功耗多供电电压设计中芯片不同电压域模块之间信号电压转换。种类包括低到高、高到低以及双向电压转换三种,一般低到高电压转换单元有高电压和低电压两个供电端口,此外该单元放置在电压域的边界处。

- 隔离单元(isolation) 隔离单元专门用于低功耗设计,它可以和上述的电平转换单元结合在一起,做成具有双重功能的单元。

- 开关单元 开关单元专门用于低功耗的,当电路中的某些模块不需要工作时将其电源关掉,从而消除该模块的静态功耗。它有精细结构和粗制结构两种,前者目前较少用,形状上有环状和列状两种。环状开关单元由SRPG(StateRetention Power Gating)单元来实现,列状开关单元可以用门控单元实现。

- 备用单元(Spare cell)

Foundry提供一种服务,允许客户在量产工艺加工进行到某个阶段的时候,让部分wafer暂时停止,而部分wafer继续加工。这样的话,客户可以在加工到poly层以及M1层时(后面的金属层还没有做),停止大部分wafer的进程,而让少量wafer继续加工到完成,然后对这些已完成的wafer上的die进行测试,如果发现有功能或时序上的问题,就可能通过预先布在die上的Spare cell来解决。只是改动几层金属层光罩就可以完成std cell重新连接,而不用改动std cell的布局(即,不用改poly层之前的所有光罩)。那些暂停加工的wafer这时就可以用新的金属层光罩往后加工,于是在silicon和光罩两方面都降低了成本。流片过程是先光刻base层和M1层的片子,这个是最贵的,这个需要一两个星期。这段时间,要是验证过程中发现了功能和metal error,就改变M2以及以上金属层的连线,连接备用cell去修。代工厂再继续做M2以及以上金属层的片子。这样就可以不需要修改place只改指定metal的routing就可以了。

RC抽取的几种工艺文件

ICC与Encounter所需文件的区别以及文件之间的转换

ICC与Encounter所需文件的区别以及文件之间的转换

| Data Library | ICC | Encounter |

|---|---|---|

| Physical Library | Milkyway | Lef |

| Logic Library | db | Lib |

| RC Extraction | Tluplus | Itf |

| Technology File | Tf | Lef |

| Cadence | Synopsys | ||

|---|---|---|---|

| ict | <——> | icf | process file |

| captable | <—–> | tluplus | rc model for APR tools |

| qrcTech file | <——> | nxtgrd | rc model for standard alone RC Ext,tool |

相互之间的转换:

1. lib转换成db

2. itf转换为tluplus

3. cell.lef转换为Milkway,同时tech.lef转换为tech.lef转换为tf