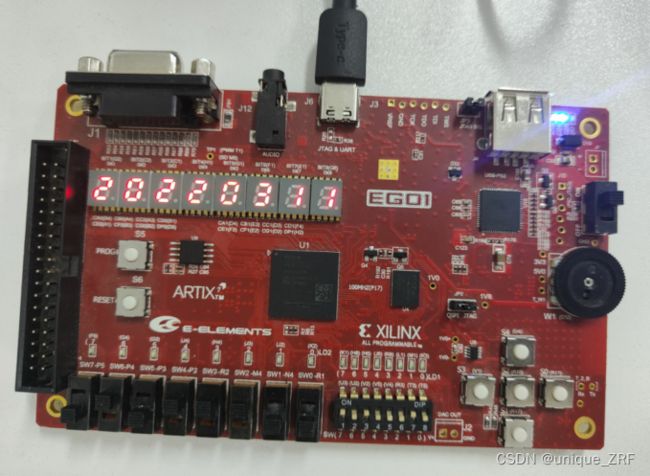

EGO1—实现拨码开关控制数码管显示数值

使用软件: Vivado

开发板: EGO1采用Xilinx Artix-7系列XC7A35T-1CSG324C FPGA

实现功能

16个拨码开关,每两个控制一个数码管的数值变化

开发板配置

七段数码管

数码管为共阴极数码管,即公共极输入低电平。共阴极由三极管驱动,FPGA需要提供正向信号。同时段选端连接高电平,数码管上的对应位置才可以被点亮。因此,FPGA 输出有效的片选信号和段选信号都应该是高电平。

管脚约束

A0~DP0控制DN0_K1 — DN0_K4的数码管的段选

A1~DP1控制DN1_K1—DN1_K4的数码管的段选

代码

verilog代码

module v_smg_1(

input clk,

input rst,

input[15:0] sw, //开关

output[7:0] seg,//段选,高有效

output[7:0] seg1,

output[7:0] an //位选,低有效

);

reg[18:0] divclk_cnt = 0;//分频计数器

reg divclk = 0;//分频后的时钟

reg[7:0] seg=0;//段码

reg[7:0] seg1=0;

reg[7:0] an=8'b00000001;//位码

reg[3:0] disp_dat=0;//要显示的数据

reg[2:0] disp_bit=0;//要显示的位

parameter maxcnt = 50000;// 周期:50000*2/100M

always@(posedge clk)

begin

if(divclk_cnt==maxcnt)

begin

divclk=~divclk;

divclk_cnt=0;

end

else

begin

divclk_cnt=divclk_cnt+1'b1;

end

end

always@(posedge divclk) begin

if(disp_bit >= 7)

disp_bit=0;

else

disp_bit=disp_bit+1'b1;

case (disp_bit)

3'b000 :

begin

disp_dat=sw[1:0];

an=8'b00000001;//显示第一个数码管,高电平有效

end

3'b001 :

begin

disp_dat=sw[3:2];

an=8'b00000010;//显示第二个数码管,低电平有效

end

3'b010 :

begin

disp_dat=sw[5:4];

an=8'b00000100;//显示第三个数码管,低电平有效

end

3'b011 :

begin

disp_dat=sw[7:6];

an=8'b00001000;//显示第四个数码管,低电平有效

end

3'b100 :

begin

disp_dat=sw[9:8];

an=8'b00010000;//显示第五个数码管,低电平有效

end

3'b101 :

begin

disp_dat=sw[11:10];

an=8'b00100000;//显示第六个数码管,低电平有效

end

3'b110 :

begin

disp_dat=sw[13:12];

an=8'b01000000;//显示第七个数码管,低电平有效

end

3'b111 :

begin

disp_dat=sw[15:14];

an=8'b10000000;//显示第八个数码管,低电平有效

end

default:

begin

disp_dat=0;

an=8'b00000000;

end

endcase

end

always@(disp_dat)

begin

if(an > 8'b00001000) begin

case (disp_dat)

//显示0—F

4'h0 : seg = 8'hfc;

4'h1 : seg = 8'h60;

4'h2 : seg = 8'hda;

4'h3 : seg = 8'hf2;

4'h4 : seg = 8'h66;

4'h5 : seg = 8'hb6;

4'h6 : seg = 8'hbe;

4'h7 : seg = 8'he0;

4'h8 : seg = 8'hfe;

4'h9 : seg = 8'hf6;

4'ha : seg = 8'hee;

4'hb : seg = 8'h3e;

4'hc : seg = 8'h9c;

4'hd : seg = 8'h7a;

4'he : seg = 8'h9e;

4'hf : seg = 8'h8e;

endcase

end

else begin

case (disp_dat)

//显示0-F

4'h0 : seg1 = 8'hfc;

4'h1 : seg1 = 8'h60;

4'h2 : seg1 = 8'hda;

4'h3 : seg1 = 8'hf2;

4'h4 : seg1 = 8'h66;

4'h5 : seg1 = 8'hb6;

4'h6 : seg1 = 8'hbe;

4'h7 : seg1 = 8'he0;

4'h8 : seg1 = 8'hfe;

4'h9 : seg1 = 8'hf6;

4'ha : seg1 = 8'hee;

4'hb : seg1 = 8'h3e;

4'hc : seg1 = 8'h9c;

4'hd : seg1 = 8'h7a;

4'he : seg1 = 8'h9e;

4'hf : seg1 = 8'h8e;

endcase

end

end

endmodule

约束文件

## clk

set_property PACKAGE_PIN P17 [get_ports clk]

set_property IOSTANDARD LVCMOS33 [get_ports clk]

## switch

set_property PACKAGE_PIN P5 [get_ports {sw[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[1]}]

set_property PACKAGE_PIN P4 [get_ports {sw[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[0]}]

set_property PACKAGE_PIN P3 [get_ports {sw[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[3]}]

set_property PACKAGE_PIN P2 [get_ports {sw[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[2]}]

set_property PACKAGE_PIN R2 [get_ports {sw[5]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[5]}]

set_property PACKAGE_PIN M4 [get_ports {sw[4]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[4]}]

set_property PACKAGE_PIN N4 [get_ports {sw[7]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[7]}]

set_property PACKAGE_PIN R1 [get_ports {sw[6]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[6]}]

set_property PACKAGE_PIN U3 [get_ports {sw[9]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[9]}]

set_property PACKAGE_PIN U2 [get_ports {sw[8]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[8]}]

set_property PACKAGE_PIN V2 [get_ports {sw[11]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[11]}]

set_property PACKAGE_PIN V5 [get_ports {sw[10]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[10]}]

set_property PACKAGE_PIN V4 [get_ports {sw[13]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[13]}]

set_property PACKAGE_PIN R3 [get_ports {sw[12]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[12]}]

set_property PACKAGE_PIN T3 [get_ports {sw[15]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[15]}]

set_property PACKAGE_PIN T5 [get_ports {sw[14]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[14]}]

##smg位码

set_property PACKAGE_PIN G2 [get_ports an[7]]

set_property IOSTANDARD LVCMOS33 [get_ports an[7]]

set_property PACKAGE_PIN C2 [get_ports an[6]]

set_property IOSTANDARD LVCMOS33 [get_ports an[6]]

set_property PACKAGE_PIN C1 [get_ports an[5]]

set_property IOSTANDARD LVCMOS33 [get_ports an[5]]

set_property PACKAGE_PIN H1 [get_ports an[4]]

set_property IOSTANDARD LVCMOS33 [get_ports an[4]]

set_property PACKAGE_PIN G1 [get_ports an[3]]

set_property IOSTANDARD LVCMOS33 [get_ports an[3]]

set_property PACKAGE_PIN F1 [get_ports an[2]]

set_property IOSTANDARD LVCMOS33 [get_ports an[2]]

set_property PACKAGE_PIN E1 [get_ports an[1]]

set_property IOSTANDARD LVCMOS33 [get_ports an[1]]

set_property PACKAGE_PIN G6 [get_ports an[0]]

set_property IOSTANDARD LVCMOS33 [get_ports an[0]]

## 段码

set_property PACKAGE_PIN B4 [get_ports {seg[7]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg[7]}]

set_property PACKAGE_PIN A4 [get_ports {seg[6]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg[6]}]

set_property PACKAGE_PIN A3 [get_ports {seg[5]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg[5]}]

set_property PACKAGE_PIN B1 [get_ports {seg[4]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg[4]}]

set_property PACKAGE_PIN A1 [get_ports {seg[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg[3]}]

set_property PACKAGE_PIN B3 [get_ports {seg[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg[2]}]

set_property PACKAGE_PIN B2 [get_ports {seg[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg[1]}]

set_property PACKAGE_PIN D5 [get_ports {seg[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg[0]}]

# 段码2

set_property PACKAGE_PIN D4 [get_ports {seg1[7]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg1[7]}]

set_property PACKAGE_PIN E3 [get_ports {seg1[6]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg1[6]}]

set_property PACKAGE_PIN D3 [get_ports {seg1[5]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg1[5]}]

set_property PACKAGE_PIN F4 [get_ports {seg1[4]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg1[4]}]

set_property PACKAGE_PIN F3 [get_ports {seg1[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg1[3]}]

set_property PACKAGE_PIN E2 [get_ports {seg1[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg1[2]}]

set_property PACKAGE_PIN D2 [get_ports {seg1[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg1[1]}]

set_property PACKAGE_PIN H2 [get_ports {seg1[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg1[0]}]