ADC相关电路的总结及提高ADC采样精度的方法(以STM32F系列为例)

ADC基本原理简介

逐次逼近寄存器型模数转换器(SAR ADC)占据着大部分的中等至高分辨率ADC市场。SAR ADC的采样速率最高可达5Msps,分辨率为8位至18位。SAR架构允许高性能、低功耗ADC采用小尺寸封装,适合对尺寸要求严格的系统。

ADC转换包括采样、保持、量化、编码四个步骤。采样阶段需要在规定的采样时间内将外部信号的电压完整无误的采样到ADC的采样电容上,即在采样开关SW关闭的过程中,外部输入信号通过外部的输入电阻RAIN和以及ADC采样电阻RADC对采样电容CADC充电。如图下图所示。

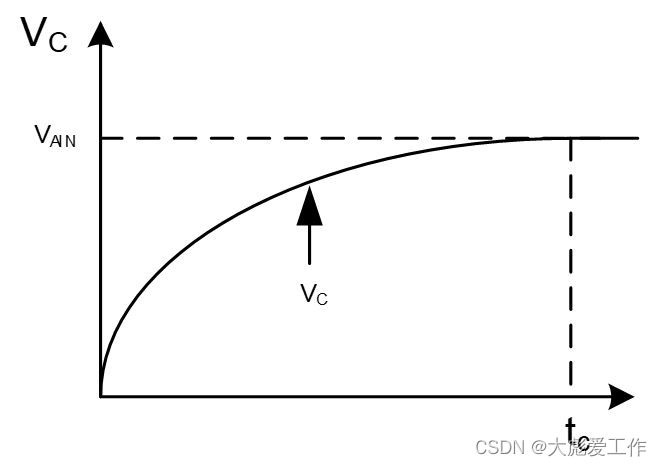

每次采样过程可以简化为外部信号通过输入阻抗以及采样电阻对采样电容的充电(即采样电容零状态的单位阶跃响应),ADC采样阶段单位阶跃响应如下图所示。

当采样时间结束后,采样误差表示为采样电容上的电压与信号源上的电压差值。在一次理想的采样过程中,这个电压差值应该保持在0.5LSB以内(LSB为SAR ADC的最小的电压分辨率,0.5LSB为SAR ADC的量化误差)。

量化阶段,将采样开关SW打开,然后由ADC时钟驱动,基于切换电容技术,将ADC采样电容上的电压逐次与不同权重的参考电压做比较,逐位确定N位数据每一位上的值(N为ADC的采样位数),然后编码输出数字码值。在量化过程中,参考电压VREF+需要对切换电容网络进行充电。VREF+基准需要在量化过程中保持稳定。

ADC准确性指标

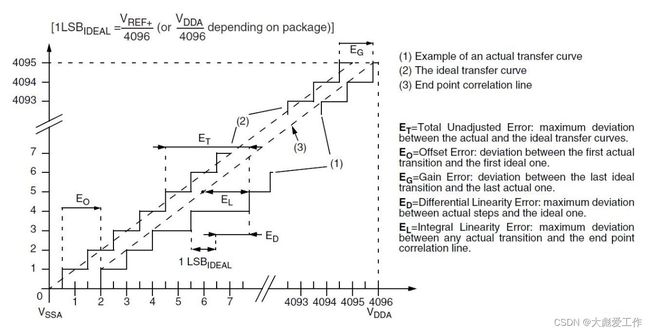

ET(Total Unadjusted Error)总不可调整误差:实际转换曲线与理想转换曲线之间最大的偏离。在最糟糕的一点,通过ADC得到的电压,与实际电压的差值。通俗讲就是最不准的一点差多少。

EO(Offset Error)偏置误差: ADC的偏置误差定义为第一个码字转换(从0x00到0x01)所对应的实际电压偏离理想电压位置的差值。

EG(Gain Error)增益误差:ADC的增益误差是指最后一次码字转换中实际转换与理想转换点电压之间(对于12bit ADC来说,即从0xFFE到0xFFF)的差值。

ED(Differential Linearity Error)微分非线性误差:微分非线性误差定义为实际量化台阶宽度与对应于1LSB的理想电压值之间的差异。指每一个码字宽度偏离理想的1LSB的程度。计算方法为每个码字模拟量的宽度减去一个LSB的值,当码字宽度大于一个LSB宽度时,ED为正值,反之,ED为负值。

EL(Integral Linearity Error)积分非线性误差:积分非线性误差是指一个码字的实际输入点与传输函数线上理想输入之间的偏移。传输函数线可以定义为第一次实际转换与最后一次实际转换所连接的线,即ADC的偏置和增益误差点之间的一条直线。

ADC经典结构图

以STM32F10x为例的ADC经典结构图如上图所示。其中,IO引脚上下两个二极管的作用为防止引脚外部过高、过低的电压输入。当引脚电压高于VDD+0.6V时,上方二极管导通;当引脚电压低于-0.6V时,下方二极管导通,防止不正常电压引入芯片导致芯片烧毁。IL是指输入漏电流,即流入流出ADC输入端的直流电流,这个电流由器件内部的ESD保护和其他参数引入,通常为微安或纳安级别,图例中显示输入漏电流的范围为±1uA。外部输入信号通过外部的输入电阻RAIN和以及ADC采样电阻RADC对采样电容CADC充电,每次采样过程可以简化为外部信号通过输入阻抗以及采样电阻对采样电容的充电。

提高ADC采样精度的方法

1.稳定参考电压

ADC转换结果为输入电压与参考电压的比值,如果参考电压不准确,转换结果也会不准确。

由于在量化编码的过程中,VREF+需要对转化电容网络充电,在量化过程中,也会有对基准源抽取电荷的动作,因此,如果没有其他的去耦措施,一个稳健且干净的VREF+基准会显著影响ADC量化的精度,我们建议对于这两个电源采用纹波噪声系数更小的LDO来供电。对于VREF+基准源,我们建议靠近引脚并联一个uF级以及一个nF级的去耦电容,一方面可以滤除来自外部低频与高频的电源噪声,另一方面,也可使ADC在量化编码过程的基准源更加稳定。

在layout过程中,相关电源线的走线上,我们推荐加宽电源迹线,以减小迹线的ESR,在量化阶段,减小转化电容网络瞬间充电对输入基准源的影响。

相同的情况,在一些场景中,VDD与VREF+来自同一颗LDO,然后在LDO与VREF+之间串联一颗磁珠,如下图VREF+串联磁珠图所示,以屏蔽外部电源对于VREF+的影响。

这里需要注意选择磁珠时,需要关注磁珠的RDC(直流电阻)参数,应当优先选取RDC小的型号,以减小在磁珠上造成的直流压降。直流电阻小,通常磁珠的高频处的阻抗也会小,因此这也是一个抗干扰与采样精度的权衡过程。另外,通常不建议在此处将磁珠换成电感,由于VREF+在量化编码过程中,会存在高频的脉冲电流,如果靠近VREF+引脚的去耦电容设置不合适,则比较容易引起VREF+电压的震荡,影响ADC的精度。

微控制器在执行指令时会在内部电源网络上产生一些不容忽视的噪声,降低系统噪声可关注一下几点:在即将开始ADC转换时,避免启动任何通信外设的数据传输,IO的切换可能会在供电电压中产生噪声;避免切换高灌电流IO,因为会在电源中产生噪声纹波;避免在同一IO端口上切换数字输出,因为A/D输入正在被转换,这会引入切换噪声。

2.合理设置ADC参考电压

根据ADC输入信号幅值范围设置合理的VREF+,或者根据配置完毕的VREF+设置合理的ADC信号输入范围。

举个例子:

当输入信号电压范围为0-2.6 V时,若设置VREF+为3.6 V,采样信号进入GD32 MCU 12bit ADC,在忽略采样误差的前提下,可以得出采样结果数字量范围为0-2958,采样结果能够分辨出0.9 mV的电压,然而对于2759-4095之间的采样码值均未出现;若改版硬件,使得VREF+为2.6 V,此时,采样结果数字量范围为0-4095,ADC能够分辨出的最小电压为0.6 mV。显然后者均有更高的采样精度。

因此在项目的硬件设计阶段,如果对于采样精度有要求的前提下,我们需要评估下ADC输入信号的电压范围,配置输入信号电压的最大值略小于VREF+,以提高采样精度。

3.合理设置输入阻抗与采样周期

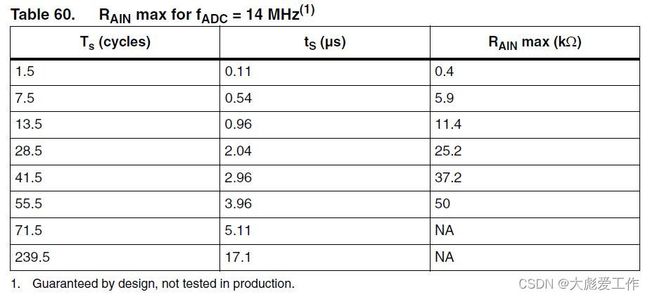

从前文理论分析可知,SAR ADC采样对于信号的输入电阻是有明确要求的,对于一个具体的ADC,其采样电阻RADC与采样电容CADC已经不可更改,当ADC的采样时钟,采样周期等可配置参数配置完毕时,则外部信号的输入阻抗则是有一个范围要求,当要求误差范围小鱼0.5LSB时,即公式:

RAINmax 配置的不同的采样周期所对应的最大输入电阻,在对应MCU型号datasheet中会给出。 例如,STM32F103系列datasheet中有: 4.软件提高ADC采样精度 取平均值有助于消除模拟输入上的噪声或错误转换的影响,当使用此方法时,采样数最好为2的倍数,这会使平均计算更有效率,因为对转换值之和求平均时的除法可通过右移做到,这样可以节省CPU时间和执行除法算法所需要的代码存储器(在Cortex-Mx内核中,右移操作仅需要1个CPU周期)。 有部分系列MCU中具有片上硬件过采样功能,硬件过采样单元执行数据预处理以减轻CPU负担。同样的,片上硬件过采样单元执行两个功能:求和和位右移。