计算机组成与结构课内实验:16位模型机的设计

我们当时是有两个实验的。一个是计组课内的实验:16位模型机的设计、还有一个是计组的最终大课设:计算机组成与结构综合实验,另一篇文章我将给出综合实验的报告

第一个是课内的设计实验:

- 引言

1.1 设计目的

(1)掌握计算机的基本组成和工作原理;

(2)掌握计算机主要功能部件的功能与设计方法;

(3)掌握MIPS指令集各类指令的功能和执行流程;

(4)综合运用所学知识,在掌握部件单元电路设计的基础上,进一步设计一台16位的

CPU,建立计算机整机概念;

(5)通过本次设计,理论联系实践,进一步加强学生分析问题、解决问题的能力,提高自身硬件设计水平。

1.2 设计任务

对内存中存放的一个数组,计算所有元素之和,然后将和存回内存中。

分析:

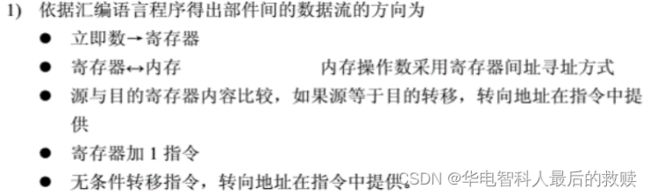

即得出数据流动的方向为:立即数→内存,内存→寄存器,寄存器→寄存器,操作数采用寄存器间接寻址方式,寄存器变址寻址方式,每通过寻址进行一次数组元素相加,则将地址增加两个字节循环次数为数组长度。

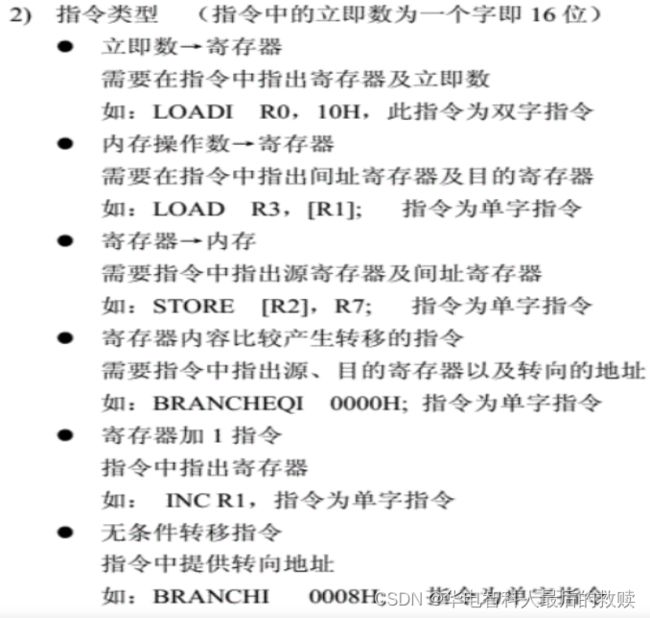

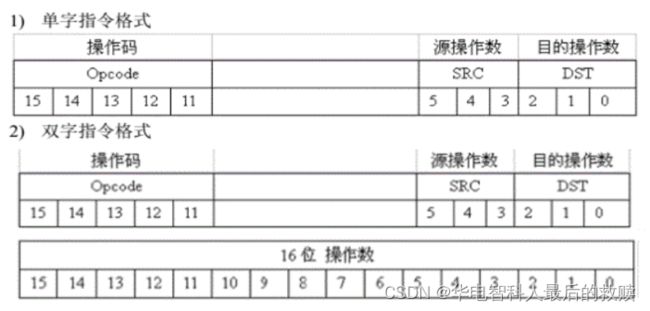

即单指令单操作数:INC BRANCHI

单指令双操作数:mov load store LOADI

双字三操作数:BRANCHEQI BRANCHGTI

2.3 操作码及功能码的编码

将主存中数据累加并存储到内存单元中的程序如下:

地址 机器码 指令

0000h 2001h 0000h Mov ax,0000h

0002h 2003h 0006h Mov cx,0006h

0004h 4002h 1232h Lea bx,a

0006h 4004h 1232h aaa:Mov, dx,[bx]

0008h 3014h Add ax,dx

0009h 1002h Inc bx

000ah 5000h Loop aaa

000ch 4002h 1323h Lea bx,b

000eh 11323h 001h Mov [bx],ax

0010h 2001h 004ch Mov ah,4ch

0012h 6000h 0021h Int 21h

依据以上的指令系统,将主存中数据累加并存储到内存单元中的程序:

分析:系统中所有向数据总线输出数据的模块,其输出口必须使用三态控制器。

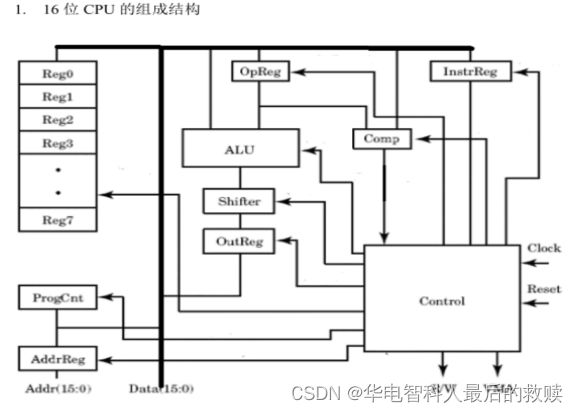

且采用单总线结构的16位CPU结构图,包含了基本的功能模块,由寄存器阵列构成的8个16位寄存器Reg0----Reg7;工作寄存器OpReg;算术逻辑运算部件ALU;移位器Shifter;输出寄存器OutReg;比较器Comp;指令寄存器InstrReg:程序计数器ProgCnt;地址寄存器AddrReg。所有功能模块共用16位的三态数据总线进行信息的传送。

控制器模块由状态机实现,控制器依据指令、数据通路通过控制线向各功能模块发出控制命令。

寄存器阵列构成的8个16位寄存器Reg0----Reg7的优点是节省资源、使用方便。它们共用一个三态开关,由控制器选择与数据总线的连接。

工作寄存器OpReg可为ALU、比较器Comp提供一个操作数,而 ALU、比较器的另一操作数直接来自数据总线。

将ALU、移位器Shifter、输出寄存器OutReg串接起来,由控制器统一控制来共同完成一些复杂的操作,由输出寄存器OutReg存储结果,输出寄存器OutReg向总线的输出端含有三态开关。

比较器Comp 由控制器直接控制,比较的结果进入控制器。

地址寄存器AddrReg提供要访问的主存单元的地址,本设计中将程序和数据放在同一存储器中。

程序计数器ProgCnt,不具备清零和+1的功能,存放CPU要执行的下一条指令的地址。

指令寄存器InstrReg存放CPU正在执行的指令。

工作寄存器OpReg,输出寄存器OutReg,指令寄存器InstrReg,程序计数器ProgCnt,地址寄存器AddrReg,均为最基本的寄存器。

为了验证CPU的功能,增加存储器,存储器中存入完成数据块传送所需的程序和数据。

3.2 指令流程以及微操作控制信号

先完成了实验指导书上的七条指令设计(优先给出):

这里因为篇幅只给出ADDU,ADDIU,SW三指令的

1)ADDU指令

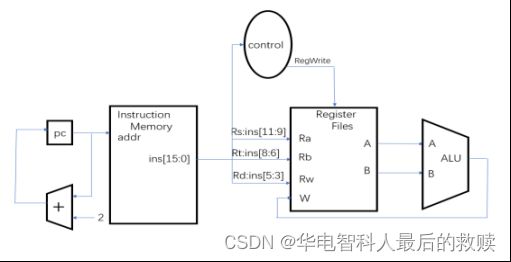

数据通路图及控制信号(蓝)如下:

数据通路分析过程:

①取指阶段:需要从程序寄存器PC中取出当前指令地址送给指令存储器InstructionMemory的地址输入端,然后从指令存储器数据输出端口得到指令内容以便下一周期译码,同时要将PC当前内容加2送给PC寄存器,使其指向下一条指令。

②译码阶段:需要从指令中得到Rs寄存器和Rt寄存器的编号,送给寄存器组RegisterFiles的Ra和Rb输入端,从输出端A、B取出其中内容即源操作数,送给运算器输入端以便于下一步进行加法运算,同时需要从指令中取出Rd寄存器编号送给寄存器组Rw输入端作为目的地址,以便之后将运算器运算结果送给寄存器组的输入端W,写入寄存器Rd。

③计算阶段:A、B通过运算部件ALU进行加法运算。

④写回寄存器阶段:将ALU输出端得到的运算结果送给寄存器组的输入端W,写入寄存器Rd。

控制信号:

RegWrite:由于加法功能需要读出寄存器Ra和Rb的内容还需要向Rw寄存器写入内容,所以需要增加一个控制信号控制寄存器组的读/写。

2)ADDIU指令

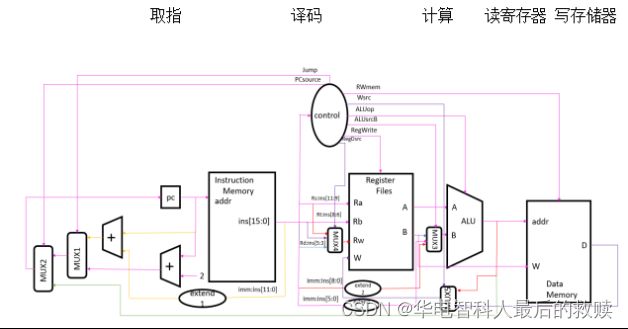

数据通路及控制信号(红色)如下:

功能:对立即数immediate进行符号扩展后与寄存器Rs的值求和,结果保存到寄存器Rs中.

数据通路分析过程:

①取指阶段:需要从程序寄存器PC中取出当前指令地址送给指令存储器InstructionMemory的地址输入端,然后从指令存储器数据输出端口得到指令内容以便下一周期译码,同时将PC加2送给PC,指向下一条指令。

②译码阶段:需要从指令中的第11位到第9位取出Rs寄存器编号送给寄存器组Ra输入端,从输出端A取出Rs寄存器内容送给运算器A输入端,第11位到第9位取出Rs寄存器编号还要送给Rw输入端作为运算后的目的寄存器编号,取出指令的8到0位送给运算器B输入端,。

③计算阶段:A、B输入的内容送给运算器进行加法运算。

④写回阶段:ALU输出内容送给寄存器组W输入端写回Rw所存的编号的寄存器。

控制信号:

ALUop:控制选择ALU功能为加法。

ALUsrcB:控制选择运算器B输入端的内容来源,本指令中来源于指令低9位扩展到16位后的立即数。

RegWrite:控制寄存器组的读出和写入。

RegDsrc:控制选择寄存器组Rw输入端的来源,本指令中应选择指令11到9位作为寄存器编号。

Jump、PCsource:控制下一条指令的转移。

3)SW指令

功能:寄存器中内容回写到主存

数据通路图及控制信号(粉)如下:

数据通路分析过程:

①取指阶段:需要从程序寄存器PC中取出当前指令地址送给指令存储器InstructionMemory的地址输入端,然后从指令存储器数据输出端口得到指令内容以便下一周期译码,同时将PC加2送给PC,指向下一条指令。

②译码阶段:需要从指令中的第11位到第9位取出Rs寄存器编号送给寄存器组Ra输入端,从输出端A取出Rs寄存器内容送给运算器A输入端,第5位到第0位取出6位立即数经过扩展送给运算器B输入端,同时还要将指令第8位到第6位送给Rb输入端作为输入数据寄存器编号。

③计算阶段:运算器对A、B输入的内容进行加法运算,运算后结果为目的地址需要送给数据存储器地址端addr。

④读寄存器:寄存器组B输出端内容输入数据,将其送给数据存储器数据输入端W。

⑤写回存储器:将数据存储器输入端W的数据写入目的地址addr。

控制信号:

ALUop:控制选择ALU功能为加法。

ALUsrcB:控制选择运算器B输入端的内容来源,本指令中来源于指令低6位扩展到16位后的立即数。

RegWrite:控制寄存器组的读出和写入。

Jump、PCsource:控制下一条指令的转移。

RWmem:控制数据存储器的读出和写入。

Wsrc:控制选择写入寄存器的数据来源,本指令来源于数据存储器输出数据。

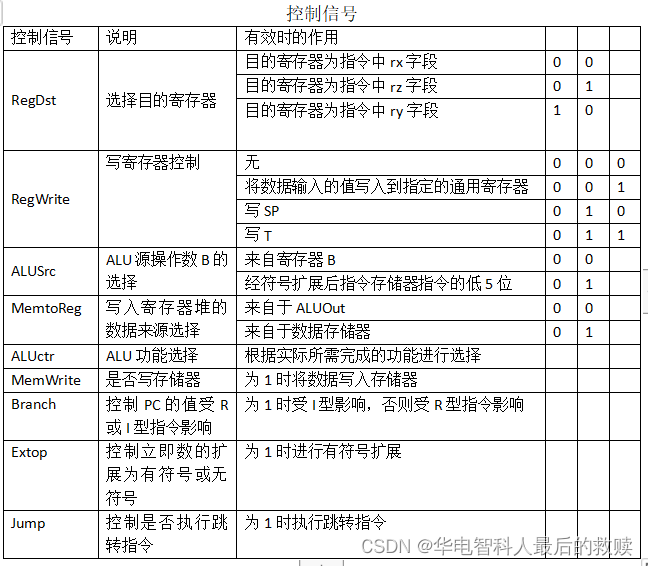

每条指令在每个周期控制信号的值:(只给出上面的三条)

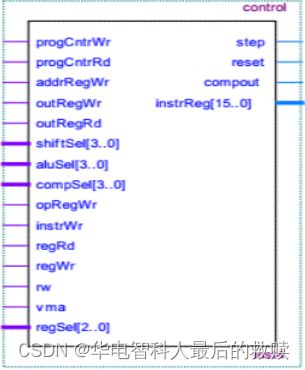

下面给出针对此次解决问题的控制器设计:

3.3 解决此次问题的控制器设计

图片如下:

控制器

寄存器r0-r7共用一个三态开关,由控制器选择与总线的连接。Alu,shifter,outreg串接起来,控制器进行统一控制,以共同完成一些复杂的操作,由outreg存储结果。比较寄存器直接由控制器控制,比较结果送入控制器。

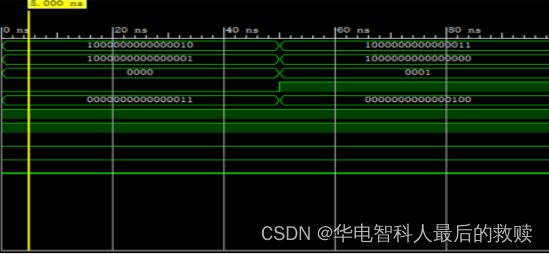

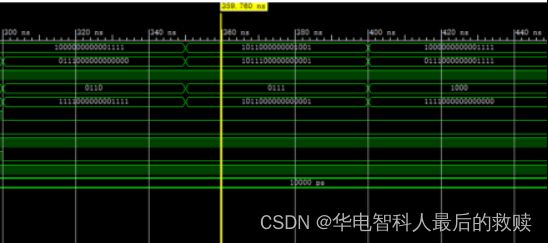

几个指令的仿真波形:

最后一个是BRANCHEQI 0000H,R1=R6时,转0000H

- 总结

4.1 实验难点

本次实验最让我抓狂的地方是智科专业没有学过《汇编语言》这门课程,导致我的汇编指令不太明白,还好百度查了资料,才明白一些汇编指令对这次实验的作用。还需要对控制器的设计充分熟悉,甚至要到每条指令的执行流程,并对通路图中各个部件的功能有更高的理解,感觉课上学到的知识不能支撑我完成此次实验,不过确是此次实验的基础,课外还需要查询大量的资料,和同学进行讨论,才可以克服这次十六位模型机的设计困难。

(报告心得体会重点:克服困难的过程,感谢老师一定要有,常怀感恩的心很重要!一个人再牛逼,也是别人带出来的,无论老师还是同学,白嫖这种事情,咱们智科牛马不可取)

4.2 心得体会

这个16位模型机对我们理解计组,理解VHDL,理解硬件有很大的引导帮助,非常感谢老师的悉心教导,特别是在CPU总数据通路图设计控制器的实验过程中,我深刻体会到控制器功能的全面以及强大,为今后继续学习计算机的各类知识打下了良好的基础。而且在自主完成实验的过程中,学习到了许多新知识,巩固了计算机的专业知识,同时培养了自己的动手能力。而且在写报告的过程中,需要很大的耐心去截图,去编辑和思考自己的实验报告结构,这对以后的论文编写也提供了一个很好的锻炼机会。

参考文献

白中英,计算机组成原理(第五版). 北京:科学出版社

佚名,16位模型机的设计.石家庄经济学院 2014年1月

Sailist,微程序控制的简单模型机设计,CSDN(https://blog.csdn.net/sailist)