基于FPGA的AFDX端系统协议栈虚链路层的研究与实现

随着航电系统复杂性的增加,无论是飞行关键任务还是乘客娱乐项目,都对机载数据总线的带宽提出了更高的要求。而ARINC429最大带宽为100Kbps,MIL—STD-1553为1Mbps,已不能满足下一代航电系统对数据通信的要求。

AFDX(航空电子全双工交换式以太网)是在以太网的基础上经过适用性改造而适用于航空电子系统互连的网络技术。它的优势有:(1)传输速率是ARINC429的一千倍,MIL-STD-1553的一百倍; (2)可大大减少导线的长度和重量; (3)可很容易地映射到ARINC429和MIL-STDl553;(4)AFDX在以太网的基础上充分应用COTS技术和开放式标准,可以借鉴成熟技术、缩短开发周期、降低研发成本。

端系统作为AFDX网络的重要组成部分,其设计中最重要的部分就是要实现AFDX协议栈。AFDX协议栈包括发送和接收两部分,分别用于发送、接收时对数据进行封装和解析,并进行相应的控制。协议层可进一步细分为AFDX通讯服务层、UDP传输层、IP网络层和链路(虚链路)服务层,其中UDP、IP层的功能与普通以太网相同,而虚链路层则加入了新的功能,以消除网络的不确定性,是端系统设计的重点。

本文将对AFDX协议栈的虚链路层进行研究,并对其设计及实现进行探讨,以促进AFDX端系统的研制。

1.1 发送协议栈

端系统的发送协议栈如图1所示。当一个消息被发往AFDX端口时,发送协议过程开始。

UDP传输层负责添加UDP包头,包括源和目标UDP端口号。

IP网络层接收UDP数据包,并根据该包对应虚链路的最大帧长判断是否需对其进行分段,之后,为各分段添加IP包头,并计算IP校验和。IP网络层还负责为IP包添加以太网头。

虚链路层负责:调度待发的以太网帧、添加序列号(基于虚链路),并将帧传递到发送冗余管理单元。再发送冗余管理单元,复制待发帧,并按发送帧的物理端口ID更新以太网源地址。

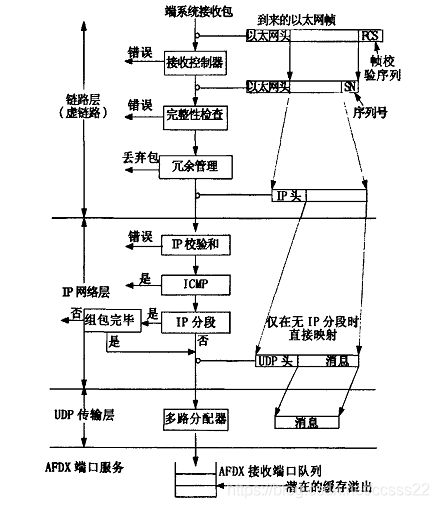

接收和发送的过程正好相反,接收协议栈如图2所示。

当接收到一个以太网帧时,接收过程开始。使用帧校验序列(FCS)来检查其正确性,若FCS正确,则将其分离,然后根据序列号(SN)对帧进行完整性检查;若SN正确,则接着对帧进行接收冗余处理。以上功能在虚链路层实现。

IP网络层对“IP校验和”进行检查,如果需要,还需将多个IP分段重组成UDP包,并将其传递到UDP传输层。

在UDP传输层,由多路分配器将属于不同端口的消息分发到其对应的AFDX端口。

图2 AFDX接收协议栈

2 协议栈虚链路层研究

下面对AFDX端系统协议栈虚链路层的功能进行研究,在此对以太网MAC层原有功能不再讨论,而专注于AFDX在以太网基础上二加入的、用于保证系统可靠性的主要技术、功能。

2.1 虚链路

虚链路(VL)是一种概念化的通信对象,物理上,很多条虚链路共用一条以太网物理链路。虚链路具有以下特点:

(1)虚链路定义一条从一个源端系统到多个目标端系统之间的单向逻辑连接;

(2)每条虚链路有确定的最大带宽;

(3)虚链路用16位短整数来标识。

端系统确保所有虚链路之问实现逻辑的独立,不论应用程序如何应用虚链路,都不会对其他虚链路产生影响;端系统的每条虚链路不论是接收还是发送,数据的顺序都必须与源端应用程序注入数据的顺序保持一致;端系统采用流量控制机制调整每条虚链路的数据流。

2.2 发送协议栈虚链路层需实现的功能

2.2.1 流量规整与多路复用

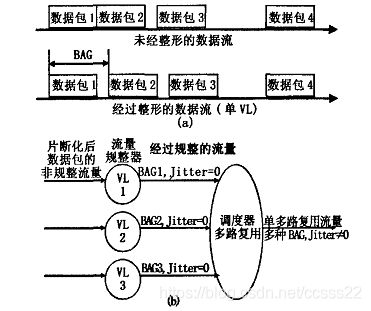

一个端系统可以有多条虚链路,发送协议栈的虚链路层需要对各条虚链路的流量进行规整。流量规整可以使数据流以比较均匀的速度向外发送,限制虚链路上的突发流量,将消息的传输延迟控制在某个范围之内,为网络的确定性提供保障。图3(a)所示即为对一条虚链路进行的流量规整。

图3 流量规整与多路复用

将端系统中各条虚链路经过流量规整后的流量合并到一条物理链路上进行发送,以复用物理链路,即为多路复用。在图3(b)中,3条规整后的虚链路流量合并为一条物理链路流量。

2.2.2 发送冗余管理

AFDX通过互为冗余的两个网络来提高系统的可靠性。发送端系统的虚链路层需以虚链路为单位对待发送的帧进行编号,即为每条虚链路的帧添加帧序号SN。然后根据配置信息中各条虚链路的冗余状态,将其帧发往MAC A、MAC B模块。

2.3 接收协议栈虚链路层需实现的功能

2.3.1 完整性检查

接收端系统在每条虚链路内按顺序检查序列号SN,即为完整性检查。完整性检查在[PSN+1,PSN+2]范围内检查帧,PSN为接收到的前一个帧的序列号。根据帧的编号可以轻易地判断同样编号的帧到达的顺序,避免帧的重复。对于无故障的网络来说,完整性检查的任务就是将帧传递到冗余管理部分;对于有故障的网络来说,完整性检查是要消除无效帧并通知网络管理部分。

2.3.2 接收冗余管理

完整性检查之后,接收端系统将根据帧的序列号消除冗余帧,这一过程就是接收冗余管理。接收冗余管理使用“先有效者胜出”规则。也就是说若两个副本均被正常接收,后到的帧将被丢弃;若其中一个帧出现传输错误,则用另一个相同的有效帧帧替代。使用这种方法,应用程序察觉不到网络冗余的存在。

3 协议栈虚链路层的设计与实现

虚链路层功能由发送模块和接收模块及MAC模块实现。发送模块和接收模块实现AFDX为保证网络确定性而新加入的功能;MAC模块实现以太网原有的MAC层功能。

3.1 发送模块设计与实现

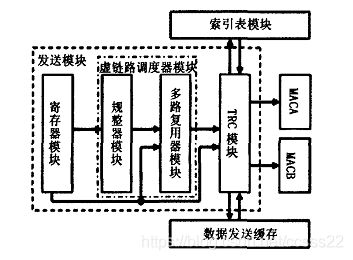

发送模块实现2.2节提到的流量规整、多路复用与发送冗余管理(TRC)功能。发送模块内部逻辑如图4所示。

图4发送模块内部逻辑框图

1)寄存器模块:该模块存储发送模块用到的信息,如VL的BAG值(带宽分配间隔)、Lmax值(最大帧长度)、Jitter值(抖动)、冗余管理状态(是向A网、B网还是向AB网同时发送)等信息。

2)虚链路调度器模块:该模块由规整器和多路复用器组成。本文的调度器实现方案是在文献[5]的基础上,并参考文献[6—11]得出的,具体如下:

(1)使用静态调度方法,端系统配置完成后,虚链路的调度表即已产生,每条虚链路仅在其相应的时间槽内发送数据;

(2)使用125us的调度周期,即将lms划分为8个时间槽;

(3)允许每一帧在下一个可用的时间槽中被发送,不提供无阻塞的通道,但不需要时间槽的指派。

该方案使端系统具有较大的带宽,且静态调度方法保证了系统的确定性,适合于有较多VL或VL的带宽要求较大的端系统。接着对规整器模块和多路复用模块进行介绍。

(1)规整器模块

规整器模块根据每条VL的BAG、Lmax值,对其数据流进行规整。具体方式为,根据各条VL的BAG Timer、Jitter Timer的状态更新该VL的FTT(Free To Transmit flag)标识。当该VL的BAG时问达到,且Jitter在最大抖动的范围内、帧长小于Lmax,则置FTT标识有效,通知多路复用器模块,该VL已具备发送条件,申请对该VL进行调度;当上述条件不满足时,置FTT标识为无效状态,通知多路复用模块,因条件不满足,不能对该VL进行调度。

(2)多路复用器模块

多路复用器对规整器的多个输出流进行多路复用,并确保多路复用后输出的抖动在可接受的界限内,然后将多路复用后的输出送入TRC模块。具体方法为,多路复用器选择一条FTT有效的VL进行发送。因本文采用基于时间槽的静态调度方案,所以每个调度周期最多仅有一条VL的FTT标识有效,多路复用器只需将该VL号告知TRC模块即可。TRC模块根据该VL的冗余状态,从数据发送缓存中取出数据发往MAC模块。

(3)TRC模块:该模块查询发送索引表得到该VL待发帧的地址,从数据发送缓存中取出该帧,并根据从寄存器模块读出的该VL的RM状态(冗余管理状态),将数据帧发往MAC模块。

图5 接收模块内部逻辑框图

3.2 接收模块设计与实现

接收模块除实现2.3节提到的完整性检查及接收冗余管理功能外,还需将经过冗余检查的有效帧按VL号存人数据接收缓存。接收模块内部逻辑如图5所示。

1)接收冗余管理模块:该模块用于验证接收帧的有效性,并消除从冗余通道接收的重复有效帧。从图5可以看出,该模块有两项主要工作:完整性检查和冗余检查。

(1)完整性检查模块

对于每个从MAC模块传来的接收帧,完整性检查模块必须校验接收到的帧是否具有该VL所期待的SN号。这个检查基于最后收到的帧,即便该帧被抛弃了。序列号检查允许链路上单帧的丢失(两个通道同时丢失时发生),而不考虑冗余管理配置。

以下两种情况,SN号虽然不符合上面提到的顺序,但依然是有效的:

①SN号为0的帧总是被接收的,因为它代表发送端系统复位;

②端系统复位后第一个收到的具有任何SN号的有效帧应该接收。

(2)冗余检查模块

冗余检查使能时,该模块为每条VL传送具有给定SN号的先有效的帧;有效帧从通道A、通道B或通过两者被接收。冗余检查模块不对帧的内容进行比较。冗余检查功能关闭时,该模块对任一通道收到的数据都向前传送。

在接收帧时,冗余检查模块还依赖于另一个参数,Skew-Max(最大偏斜)。SkewMax是两个接收到的有效帧之问的最大允许时间。若一条虚链路的SkewMax超出,冗余检查模块将把两个完整性检查模块都重启,以便它们接收下一个有效帧,而不考虑SN号,该机制允许端系统容忍暂时的数据丢失。

(3)SN表

存储端系统各接收虚链路最后收到的帧的SN号,用于完整性检查。

(4)逻辑物理VL号映射表

存储端系统各接收VL的逻辑VL号与物理VL号的对应关系。其他模块在查询该表后,得到物理VL号,便于操作。

2)包分拣模块:包分拣模块根据VL号判断到来的帧属于哪条虚链路,并将该帧存入该虚链路对应的数据接收缓存中。

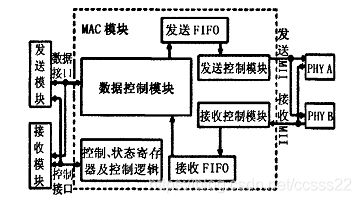

3.3 MAC模块设计与实现

MAC模块主要实现以下功能:为发送模块、接收模块提供数据、控制接口,实现数据的传送、控制及状态的传送;实现发送和接收MII接口(媒体无关接口),控制PHY A、PHY B进行发送和接收。MAC模块内部逻辑如图6所示。

图6 MAC模块内部逻辑框图

(1)数据控制模块:数据控制模块对外提供数据接口。将外部模块欲发送的数据存入模块内部的发送FIFO中,等待发送;并将接收FIFO中收到的数据发往外部模块。

(2)控制、状态寄存器及控制逻辑模块:该模块向外部模块提供控制接口。模块内部包含控制寄存器、状态寄存器及控制逻辑。

(3)发送FIFO、接收FIFO:这两个模块分别用于暂存待发送的数据和接收到的数据。

(4)发送及接收控制模块:实现发送及接收的MII接口,控制PHY芯片进行数据的发送与接收。

4 在项目中的应用

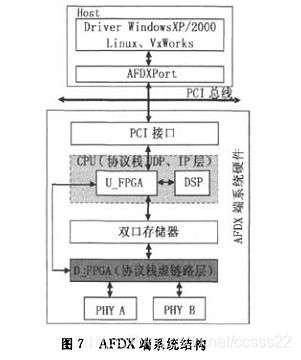

本文的设计在图7所示的AFDX端系统的研制中得到了成功应用,其中D_FPGA即为本文设计的AFDX端系统协议栈虚链路层的基于FPGA的实现。

在图7所示的端系统结构中:PCI接口模块实现PCI的接口;CPU模块实现AFDX端系统协议栈UDP、IP层的功能;双口存储器模块作为发送、接收虚链路帧的缓存。并存储端系统配置和运行需用到的其它数据;PHY模块实现以太网的物理层接口。

5 结论

本文着重对AFDX协议栈的虚链路层进行了研究,介绍了一种符合ARINC664 Part7规范要求的解决方案,描述了虚链路层各模块的设计思想,并在QuartuslI下对各功能模块的VHDL代码进行了功能和时序仿真。本方案基于FPGA的实现,已在西北工业大学测控与仿真技术研究所研制的AFDX端系统接口板中成功地进行了应用。端系统接口板初步的测试表明,本文的设计实现了AFDX虚链路层的基本功能,方案可行。