二、17【FPGA】无源蜂鸣器驱动实验

前言

学习说明此文档为本人的学习笔记,注重实践,关于理论部分会给出相应的学习链接。

学习视频:是根据野火FPGA视频教程——第二十讲

https://www.bilibili.com/video/BV1nQ4y1Z7zN?p=3

理论学习

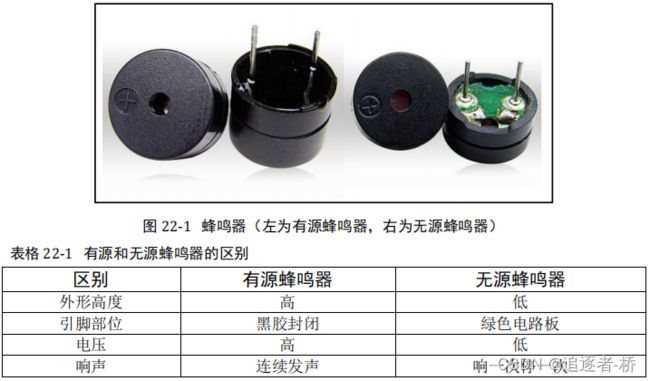

蜂鸣器按其结构可分为电磁式蜂鸣器和压电式蜂鸣器两种类型。压电式蜂鸣器是以压电陶瓷的压电效应,来带动金属片的振动而发声;而电磁式蜂鸣器则是用电磁的原理,通电时将金属振动膜吸下,不通电时以振动膜的弹力弹回。由于两种蜂鸣器发声原理不同,电压式结构简单耐用但音调单一、音色差,适用于报警器等设备;而电磁式由于音色好,所以多用于语音、音乐等设备。

蜂鸣器按其是否带有信号源又分为有源蜂鸣器和无源蜂鸣器。有源蜂鸣器的内部装有集成电路,不需要音频驱动电路,只需要接通直流电源就能直接发出声响。而无源蜂鸣器只有外加音频驱动信号才能发出声响。

无源蜂鸣器的驱动原理:

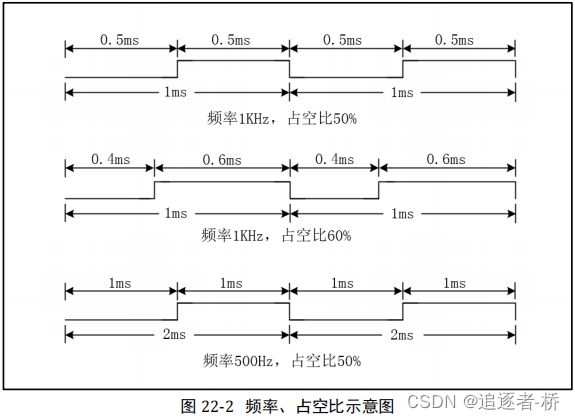

无源蜂鸣器与有缘蜂鸣器不同,因其内部不带震荡源,所以其无法向有缘蜂鸣器那样直接用直流信号驱动,这里需要使用 PWM 方波才能驱动其发声。

我们只要控制输入的 PWM 方波,输入不同的 PWM 方波发出的声音就不一样了。而不同频率和占空比的方波发出的声音是不同的,其中频率对音调有影响,占空比对音量大小有影响。所以我们只需产生不同频率和占空比的 PWM 方波去驱动无源蜂鸣器就能让无源蜂鸣器发出不同的音调了。

实战演练一

一、设计规划

1.1 实验目标

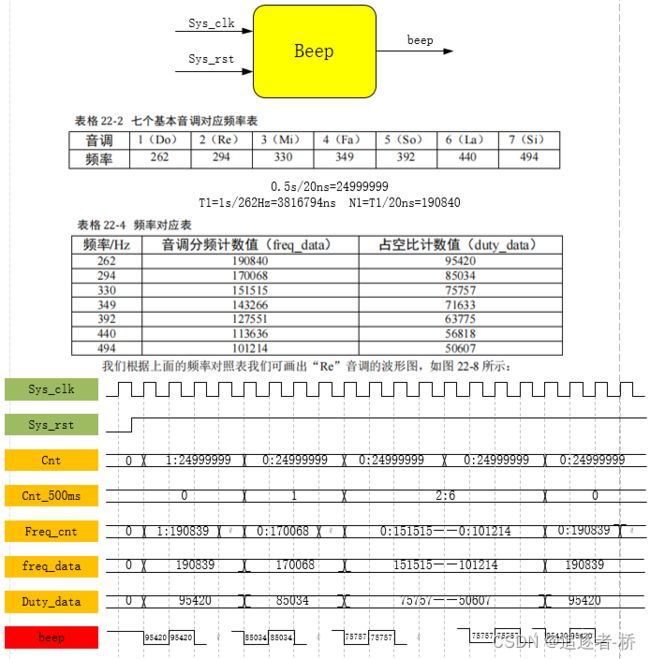

驱动无源蜂鸣器进行七个基本音调“哆来咪发梭拉西”的循环鸣叫,每个音节持续0.5s后,进入下一音阶。

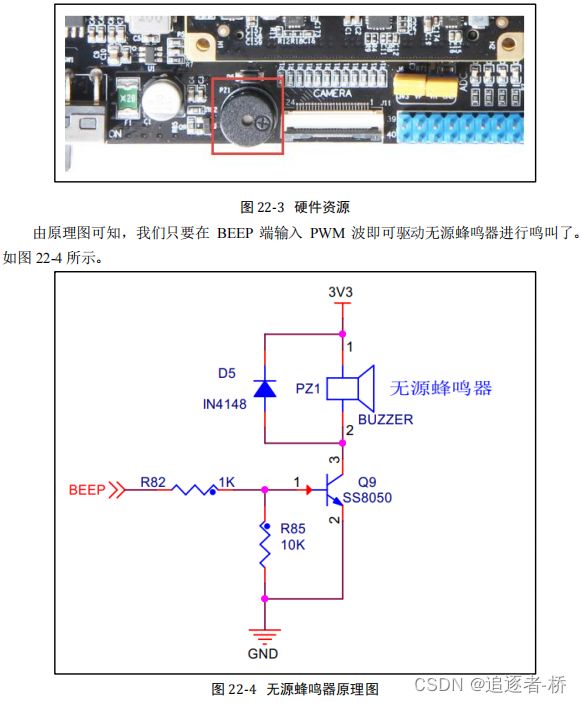

2.1 硬件资源

二、程序设计

2.1 波形图绘制

需要由于0.5s声音变化一次,且7个因为一个周期,所以需要两个中间变量来定义这两个值。

为使电路工作在特定的频率上才会产生相应的声音,时钟频率为50MHz,而声音的频率较低,因此需要对时钟频率进行分频处理。由于电平变化所以可以取周期的一般对电平进行翻转。

2.2 代码编写

module beep

#(

parameter TIME_500MS = 25'd24999999,

DO = 18'd190839 , //262

RE = 18'd170067 , //294

MI = 18'd151514 , //330

FA = 18'd143265 , //349

SO = 18'd127550 , //392

LA = 18'd113635 , //440

XI = 18'd101214 //494

)

(

input wire sys_clk,

input wire sys_rst_n,

output reg beep

);

reg [24:0] cnt;

reg [2:0] cnt_500ms;

reg [17:0] freq_cnt;

reg [17:0] freq_data;

wire [16:0] duty_data;

//系统时钟计数器

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

cnt <= 25'd0;

else if(cnt == TIME_500MS)

cnt <= 25'd0;

else

cnt <= cnt + 1'b1;

//0.5s计数器

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

cnt_500ms <= 3'd0;

else if((cnt_500ms == 6) && (cnt == TIME_500MS))

cnt_500ms <= 3'd0;

else if(cnt == TIME_500MS)

cnt_500ms <= cnt_500ms + 1'b1;

else

cnt_500ms <= cnt_500ms;

//声调频率计数器,声调的计数是变化的所以不能固定一个值

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

freq_cnt <= 18'd0;

else if((freq_cnt == freq_data) || (cnt == TIME_500MS))

freq_cnt <= 18'd0;

else

freq_cnt <= freq_cnt + 1'b1;

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

freq_data <= DO;

else case(cnt_500ms)

3'd0: freq_data <= DO;

3'd1: freq_data <= RE;

3'd2: freq_data <= MI;

3'd3: freq_data <= FA;

3'd4: freq_data <= SO;

3'd5: freq_data <= LA;

3'd6: freq_data <= XI;

default: freq_data <= DO;

endcase

//数据左移一位表示乘2,右移一位表示除以2

assign duty_data = freq_data >> 1'b1 ;

//频率输出

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

beep <= 1'b0;

else if(freq_cnt == duty_data)

beep <= ~beep;

else

beep <= beep;

endmodule

三、逻辑仿真

3.1 仿真代码

`timescale 1ns / 1ps

//

// Company: 追逐者——桥的小作坊

// Create Date: 2022/05/18 16:04:24

// Design Name: 无源蜂鸣器变频驱动

// Module Name: tb_beep

//

module tb_beep();

reg sys_clk;

reg sys_rst_n;

wire beep;

initial begin

sys_clk = 1'b1;

sys_rst_n <= 1'b0;

#20

sys_rst_n <= 1'b1;

end

always #10 sys_clk = ~sys_clk;

beep

#(

.TIME_500MS(25'd2499),

.DO (18'd262), //262

.RE (18'd294), //294

.MI (18'd330), //330

.FA (18'd349), //349

.SO (18'd392), //392

.LA (18'd440), //440

.XI (18'd494) //494

)

beep_isnt

(

.sys_clk (sys_clk ),

.sys_rst_n(sys_rst_n),

.beep (beep )

);

endmodule

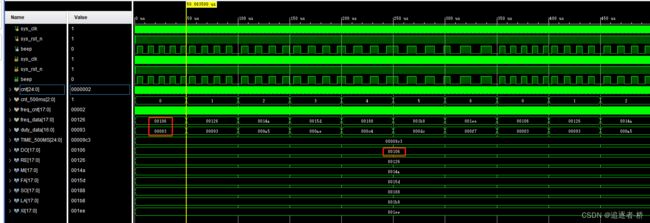

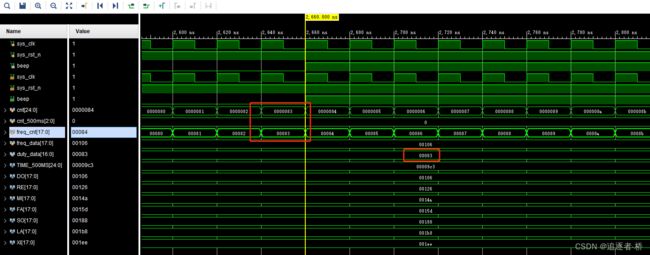

3.2 波形图对比

计数器的计数和跳变都没有问题

可以看出蜂鸣器的电平变化也没问题。

四、上板调试

四、上板调试

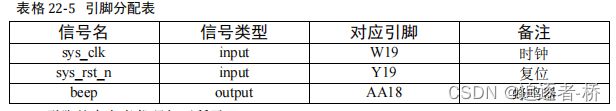

4.1 引脚约束

4.2 下载到板卡中

生成bit流文件下载文件,如图实验:

FPGA——无源蜂鸣器驱动实验

五、总结

频率的改变需要通过分频和倍频实现,且需要通过计数器来计算时间并作为其他事件的触发条件。