数电课程设计分享之流水灯

题目要求:

8个共阳极的LED灯,提供48MHZ的时钟信号;流水灯模式为:1、5亮,其余灭,右移三次后全灭;4、8亮,其余灭,左移三次后全灭;4、5亮,其余灭,向两边移动三次后全灭;1、8亮,其余灭,向中间移动三次后全灭。

设计思路:

1、Moore机

2、状态输出表:

| 状态名 |

状态赋值 |

输出 |

| 0 |

00000 |

01110111 |

| 1 |

00001 |

10111011 |

| 2 |

00010 |

11011101 |

| 3 |

00011 |

11101110 |

| 4 |

00100 |

11111111 |

| 5 |

00101 |

11101110 |

| 6 |

00110 |

11011101 |

| 7 |

00111 |

10111011 |

| 8 |

01000 |

01110111 |

| 9 |

01001 |

11111111 |

| 10 |

01010 |

11100111 |

| 11 |

01011 |

11011011 |

| 12 |

01100 |

10111101 |

| 13 |

01101 |

01111110 |

| 14 |

01110 |

11111111 |

| 15 |

01111 |

01111110 |

| 16 |

10000 |

10111101 |

| 17 |

10001 |

11011011 |

| 18 |

10010 |

11100111 |

| 19 |

10011 |

11111111 |

3、未用状态的次态为无关项,状态编码为自然二进制,用D触发器做状态存储器。

4、转移方程:

q0=q1·q2·q3·q4+q0·q4’+q0·q3’

q1=q1’·q2·q3·q4+q1·q2’+q1·q4’+q1·q3’

q2=q0’·q2’·q3·q4+q2·q4’+q2·q3’

q3=q3’·q4+q3·q4’

q4=q3’·q4’+q3·q4’

5、输出方程:

z0=(q0+q2+q3+q4)·(q1’+q2’+q4’)·(q1’+q2+q3+q4);

z1=(q0’+q3+q4)·(q1’+q2’+q3+q4)·(q0+q1+q2+q3+q4’)·(q1+q2’+q3’+q4’); z2=(q0’+q3+q4’)·(q1’+q2+q3’+q4’)·(q0+q1+q3’+q4);

z3=(q0’+q3’+q4)·(q0+q1+q2+q3’+q4’)·(q1+q2’+q3+q4’)·(q1’+q2+q3’+q4);

z[4:7]可以通过z[0:3]得到:

select=(q0|q1&(q2|q3|q4))

z[4:7]=({4{select}} &({z3,z2,z1,z0}))|({4{!select}}&({z0,z1,z2,z3}));

6、分频得到1HZ的时钟

自启动性:

| 未用状态 |

下一状态 |

| 10100 |

10101 |

| 10101 |

10110 |

| 10110 |

10111 |

| 10111 |

01000 |

| 11000 |

11001 |

| 11001 |

11010 |

| 11010 |

11011 |

| 11011 |

01000 |

| 11100 |

11101 |

| 11101 |

11110 |

| 11110 |

11111 |

| 11111 |

10000 |

最多经过三次时钟上升沿,回到正常状态中。

思考:

(1)采用格雷码为状态编码赋值可能更好。

(2)采用JK触发器可能会使转移方程变得简单。

(3)使用八个触发器,直接以流水灯的变化作为该状态的次态,可以省掉译码电路。

电路图(可能看不清楚):

代码

module led_control(

input clk,

output [7:0] led

);

//reg [7:0] ledout;

reg [31:0] divclock_num=0;

reg clock=0;

reg q0=0,q1=0,q2=0,q3=0,q4=0;

wire z0,z1,z2,z3;

parameter full_num=24000000;

always@(posedge clk)

begin

if (divclock_num==full_num)

begin

clock=~clock;

divclock_num=0;

end

else

begin

divclock_num=divclock_num+1'b1;

end

end

assign z0=(q0|q2|q3|q4)&(~q1|~q2|~q4)&(~q1|q2|q3|q4);

assign z1=(~q0|q3|q4)&(~q1|~q2|q3|q4)&(q0|q1|q2|q3|~q4)&(q1|~q2|~q3|~q4);

assign z2=(~q0|q3|~q4)&(~q1|q2|~q3|~q4)&(q0|q1|~q3|q4);

assign z3=(~q0|~q3|q4)&(q0|q1|q2|~q3|~q4)&(q1|~q2|q3|~q4)&(~q1|q2|~q3|q4);

assign led[7:4]={z0,z1,z2,z3};

assign led[3:0]=({4{(q0|q1&(q2|q3|q4))}}&({z3,z2,z1,z0}))|({4{!(q0|q1&(q2|q3|q4))}}&({z0,z1,z2,z3}));

always@(posedge clock)

begin

q0<=q1&q2&q3&q4|q0&~q4|q0&~q3;

q1<=~q1&q2&q3&q4|q1&~q2|q1&~q4|q1&~q3;

q2<=~q0&~q2&q3&q4|q2&~q4|q2&~q3;

q3<=~q3&q4|q3&~q4;

q4<=~q3&~q4|q3&~q4;

end

endmodule

仿真文件:

module sim_led();

reg clk;

wire [7:0] led;

led_control uut(clk,led );

initial

begin

clk=0;

end

always #2 clk=~clk;

endmodule

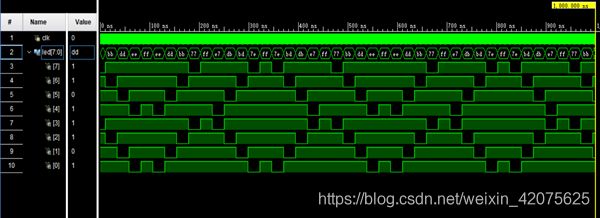

vavido仿真波形: