vivado tcl开发流程

本文以简单的led灯为例,阐述基于tcl的Vivado开发流程。

文件内容编写如下:

led.v

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2022/12/12 14:57:22

// Design Name:

// Module Name: alu

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module led(

input wire clk,

input wire rst,

output reg led

);

reg [31:0] cnt;

always@(posedge clk,posedge rst)

if(rst)

led<=0;

else if(cnt<500)

led<=1;

else

led<=0;

//

always@(posedge clk,posedge rst)

if(rst)

cnt<=0;

else if(cnt==1000-1)

cnt<=0;

else

cnt<=cnt+1;

endmodule

test.v

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2022/12/12 14:59:34

// Design Name:

// Module Name: test

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module test(

);

reg clk;

reg rst;

wire led;

initial

begin

clk=0;

forever

#5 clk=~clk;

end

initial

begin

rst=1;

#100

rst=0;

end

//inst

led U(

.clk(clk),

.rst(rst),

.led(led)

);

endmodule

约束文件led.xdc

set_property PACKAGE_PIN T22 [get_ports led]

set_property IOSTANDARD LVCMOS33 [get_ports led]

set_property PACKAGE_PIN Y9 [get_ports clk]

set_property IOSTANDARD LVCMOS33 [get_ports clk]

set_property PACKAGE_PIN P16 [get_ports rst]

set_property IOSTANDARD LVCMOS33 [get_ports rst]

开发流程

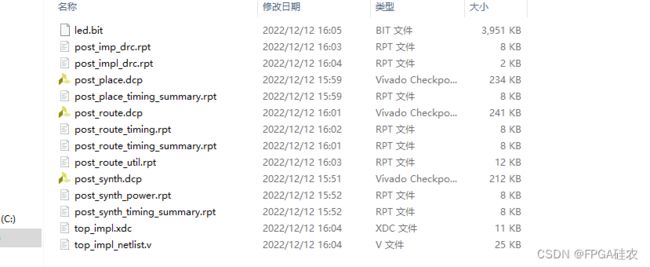

- 指定一个设计文件的输出路径,所有生成的报告、结果文件等都将存放在该路径文件夹下

set outputDir ./Out

file mkdir $outputDir

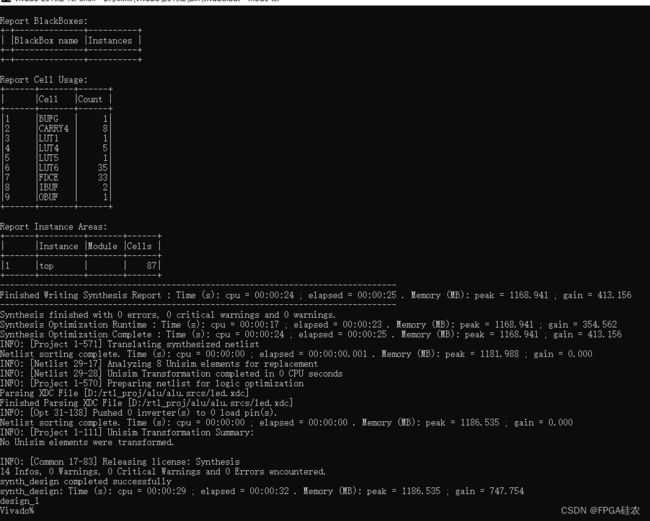

运行结果:

2. 读取设计的Verilog源文件和XDC约束文件

read_verilog led.v

read_xdc led.xdc

synth_design -top led -part xc7z020clg484-2

write_checkpoint -force $outputDir/post_synth

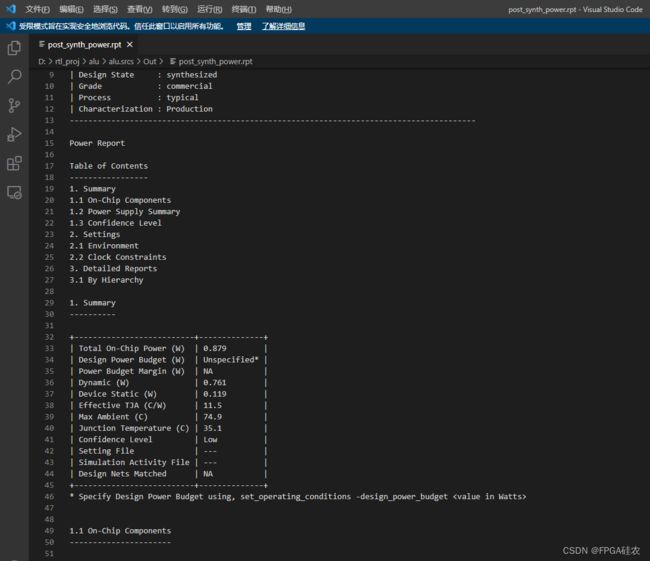

- 生成综合后的时序报告和功耗报告。

report_timing_summary -file $outputDir/post_synth_timing_summary.rpt

report_power -file $outputDir/post_synth_power.rpt

- 对设计、功耗进行优化,并对设计布局,对布局后的设计进行逻辑物理优化

opt_design #对设计进行优化

power_opt_design #对功耗进行优化

place_design #对设计进行布局

phys_opt_design #对布局后的设计进行逻辑物理优化

- 布局后写入一个设计检查点。

write_checkpoint -force $outputDir/post_place

- 生成布局后的时序总结报告

report_timing_summary -file $outputDir/post_place_timing_summary.rpt

- 对设计进行布线。

route_design

write_checkpoint -force $outputDir/post_route

- 生成布线后的时序总结报告。

report_timing_summary -file $outputDir/post_route_timing_summary.rpt

- 生成布线后的时序报告

report_timing -sort_by group -max_paths 100 -path_type summary -file $outputDir/post_route_timing.rpt

- 生成布线后的利用率报告。

report_clock_utilization -file $outputDir/post_route_util.rpt

- 生成布线后的功耗报告。

report_power -file $outputDir/post_imp_drc.rpt

- 生成布线后的drc报告。

report_drc -file $outputDir/post_impl_drc.rpt

- 写Verilog文件。

write_verilog -force $outputDir/top_impl_netlist.v

- 写xdc文件。

write_xdc -no_fixed_only -force $outputDir/top_impl.xdc

- 生成bit流文件。

write_bitstream -force $outputDir/test.bit