ZYNQ tcl语法编译生成vivado或IP核

一、tcl 全称是 Tool command Language。它是一个基于字符串的命令语言,是一个解释性语言,所谓解释性是指不象其他高级语言需要通过编译和联结,它象其他 shell 语言一样,直接对每条语句顺次解释执行。tcl 数据类型简单。对 tcl 来说,它要处理的数据只有一种——字符串。Tcl 将变量值以字符串的形式进行存储,不关心它的实际使用类型。vivado是Xilinx最新的FPGA设计工具,支持7系列以后的FPGA及Zynq 7000的开发。与之前的ISE设计套件相比,vivado可以说是全新设计的。看在vivado上,tcl已经成为唯一支持的脚本。tcl是一种很容易用户自己定义命令的脚本语言,Xilinx在此基础上增加了大量vivado的命令。对于vivado自定义的非标准的tcl命令,输入该命令后,继续输入空格+“-help”,可以查到该命令的详细解释。

二、tcl的基本语法

1. 变量和变量替换

set month 3

set day 2

set year 79

set date "$month:$day:$year"

puts $date若要在双引号括起来的单词中包含双引号,则需要用反斜线(\"parameter\")替换:

set name green.hand

set msg "I am a \"$name\""

打印 I am a "green.hand"大括号引用更加彻底,它取消所有特殊字符特殊意义:

set price {egg: $2.1/dozen

salt: $1.24/pound}

该例子中,$字符不会触发变量替换,换行符也不会被识别,因此\n也将失去换行功能。2.表达式

set value [expr 0==1]

puts $value

set value [expr 2>=1]

puts $value

set value [expr 2+3]

puts $value3.指令替换

puts "I am [expr 10*2] years old, and my IQ is [expr 100-25]"

set my_heigth 6.0

puts "If I was 2 inchs taller,I would be [expr $my_heigth + (2.0/12.0) ] feet tall"4.流程控制

set my_planet "earth"

if {$my_planet=="earth"}

{

puts "I feel rigth at home ."

}

else if{$my_planet == "venus"}

{

puts "This is ont my home."

}

else

{

puts "I am neither from earth,nor from Venus."

}

set temp 95

if{$temp < 80}

{

puts "It's a little chilly."

}

else

{

puts "Warm enough fo me."

}set num_legs 4

switch $num_legs

{

2{puts "It could be a human."}

4{puts "It could be a cow."}

6{puts "It could be an ant."}

8{puts "It could be a spider."}

default {puts "It could be anything."}

}

for {set i 0} {$i<5} {incr i 1}

{

puts "In the for loop,and i == $i"

}三,使用tcl编译生成vivado工程

1,tcl语言的执行顺序是:先分组,再替换,最后执行。

花括号中不准替换;双引号和花括号的作用都是分组,但是不同之处在于是否支持替换;

语句运行的时候首先分组(分组有三种方法:空格,双引号和花括号),然后替换($的作用是变量引导符,在字符串中如果要替换某个变量,可能还需要用{}来界定变量的起始和终点),最后运行。

2,使用tcl生成vivado:需要设置环境变量,在path环境变量中添加Vivado的路径,路径设置到bin文件夹,例如C:\Xilinx\Vivado\2017.4\bin

在Windows界面下,“开始”->“运行”,输入cmd,打开windows命令行终端。这个时候 有三个选择:

(1). 输入“vivado”,启动Vivado GUI界面,和点击桌面上的图标启动vivado没什么区别;直接点击桌面图标,就是调用windows batch命令启动vivado

(2). 输入“vivado -modebatch -source file.tcl”,从脚本批处理的形式启动vivado,运行后直接执行file.tcl文件

(3). 输入“vivado -modetcl”,启动tcl交互式命令行。

3,最常用的方式:

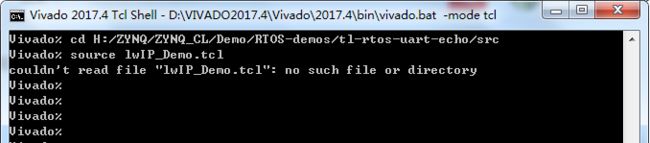

(1)从windows搜索处打开tcl console

(2)输入tcl命令行,cd +文件路径……打开工程

注意·:在文件浏览器路径复制的文件路径斜杠不对,需要换成右斜杠

(3)source xxx.tcl,这时候vivado工程就生成了

四,使用tcl语法编译生成IP核

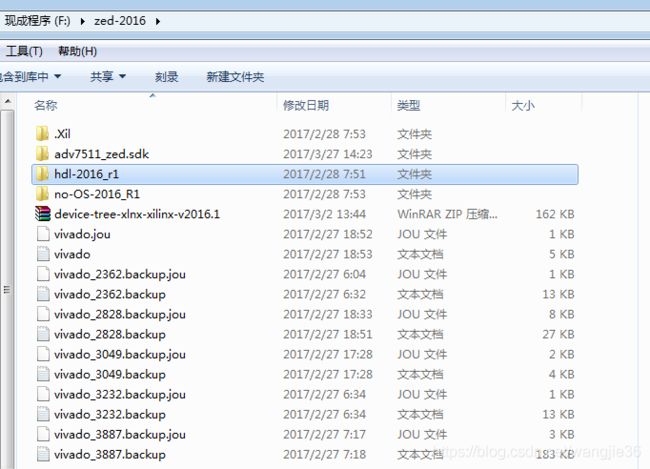

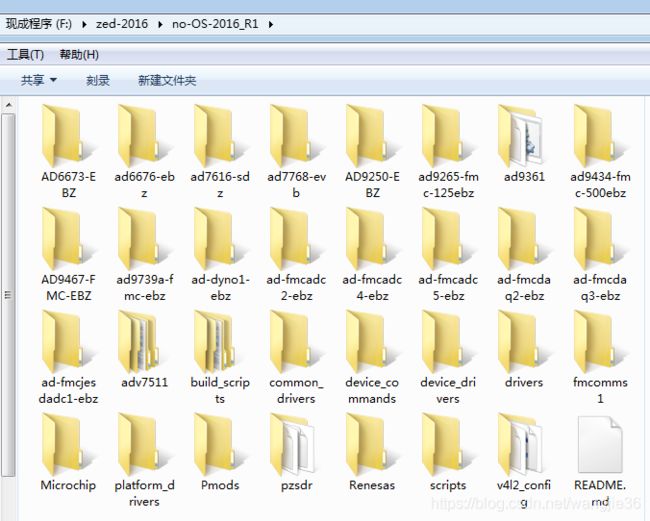

内核下载2016r1的,设备树,uboot都下载2016r1的

要进行HDMI的输出测试,还需要PS端的测试程序,可以在ADV7511

页面找到no-OS版的下载链接,最后两行,包括transmitter library和测试代码

编译HDL库,需要先编译如下库

- hdl-2016_r1/library/axi_clkgen source axi_clkgen_ip.tcl

- hdl-2016_r1/library/axi_hdmi_tx source axi_hdmi_tx_ip.tcl

- hdl-2016_r1/library/axi_i2s_adi source axi_i2s_adi_ip.tcl

- hdl-2016_r1/library/axi_spdif_tx source axi_spdif_tx_ip.tcl

- hdl-2016_r1/library/util_i2c_mixer source util_i2c_mixer_ip.tcl

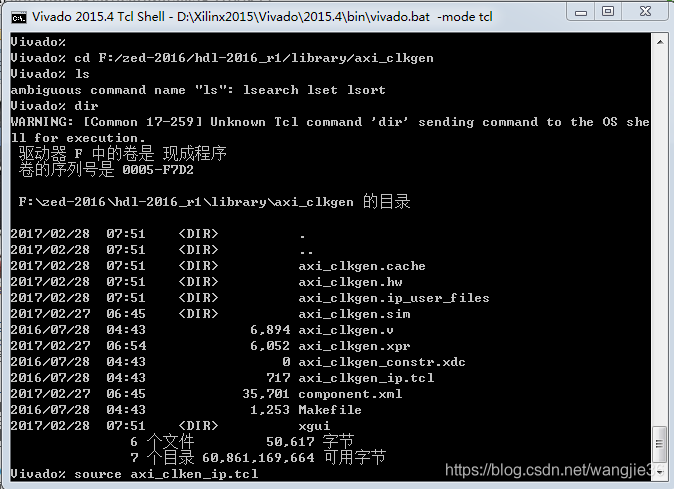

编译方法:比如编译axi_clkgen,打开vivado tcl shell,进入 cd F:/down_zed/4/hdl-2016_r1/library/axi_clkgen目录,执行source axi_clkgen_ip.tcl

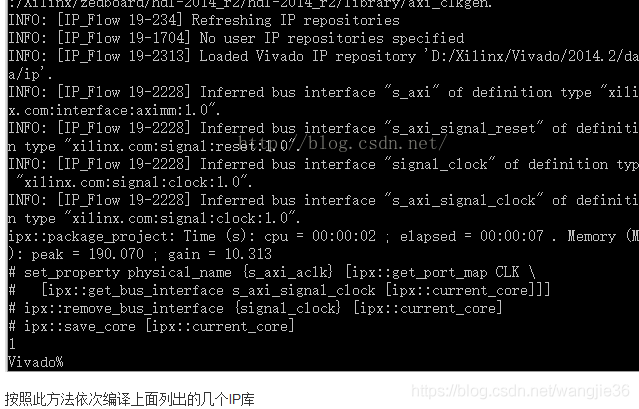

编译成功后输出如下信息

构建ADV7511项目,打开vivado gui,在tcl命令行里进入到hdl-2016_r1/projects/adv7511/zed目录,执行tcl脚本进行构建:source system_project.tcl

执行了此步骤以后,这时候就变成了vivado工程

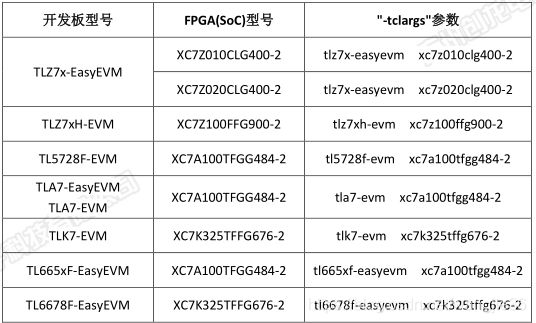

Vivado%:vivado -mode batch -source axi_gpio_project.tcl -tclargs tlz7-easyevm xc7z020clg400-2

vivado -mode batch:使用vivado的batch模式

-source axi_gpio_project.tcl:选中要执行的vivado脚本文件

-tclargs tlz7-easyevm xc7z020clg400-2:修改“-tclargs”参数,即可生成对应的FPGA芯片型号的工程,

中途如果报错,去xilinx官网下载一个能够编译HLS ip核的vivado版本,打补丁安装vivado2015.1,

2015.4.1 Vivado - Vivado 2015.4 更新 1 (2015.4.1) 版本说明

Xilinx Customer Community