FPGA驱动74HC595实现数码管动态显示

数码管原理

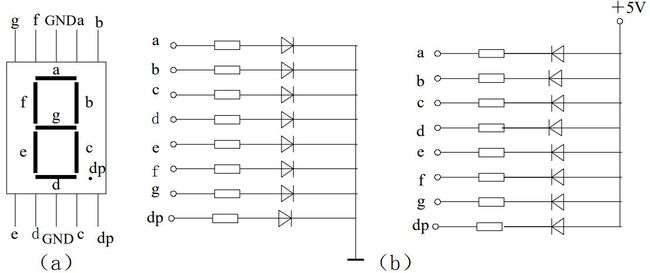

数码管分共阴极和共阳极两种,上图中间是共阴极数码管,点亮共阴极数码管需要给高电平,右边是共阳极数码管,点亮共阳极数码管需要给低电平。比如点亮abcdef就能显示0,点亮bc就能显示1,等等。

静态显示

每一个8段数码管需要8个引脚,那么6个数码管就要48个引脚,对于fpga来说占用引脚过多。但友晶的DE2开发板就是这种方式,虽然占用引脚很多,但这种方式使用起来最简单。

动态显示

将每个数码管的段选信号都连在一起,然后用6bit位选信号来选择某一个数码管进行显示,引脚占用就减少到14了。

动态显示下,任意时刻只有一个数码管是亮的。6个数码管会轮流点亮,由于数码管的余晖效应,只要刷新够快,就能让所有数码管同时显示。

74HC595

由于fpga引脚资源宝贵,为了节约IO口,数码管电路一般会用到移位寄存器74HC595,它能将串行数据转化为8位并行数据,74HC595内部结构非常简单,就是一个8位的移位寄存器和一个8位的存储寄存器:

2片74HC595级联就能实现16位串转并,舍弃掉最后两位,就能实现14位串转并功能。FPGA内部的14位的位选段选信号是并行的,我们需要先将其转化为串行数据输入74hc595,然后控制该芯片将串行数据转化为并行数据输出,只需控制DS、SHCP、STCP、OE四个引脚即可,这样FPGA的引脚占用就从14减小到4了。

此处我们需要自己写一个74hc595的驱动,由于是两片级联实现14位串转并,所以需要每14个shcp上升沿给出一个stcp上升沿,系统时钟50M,shcp时钟选择系统时钟二分频即25M,代码如下:

module dual_74hc595_ctrl(

input clk, // 50M

input rst_n,

// host side

input [5:0] sel,

input [7:0] seg,

// 74HC595 side

output ds,

output reg shcp,

output reg stcp,

output oe

);

// 低电平有效

assign oe = 1'b0;

// 合并位选段选信号

wire [13:0] ds_parallel = {seg, sel};

// 2分频,产生25M shcp

always @(posedge clk, negedge rst_n) begin

if(!rst_n)

shcp <= 0;

else

shcp <= ~shcp;

end

// bit计数器

reg [3:0] bit_cnt;

always @(posedge clk, negedge rst_n) begin

if(!rst_n)

bit_cnt <= 0;

else if(shcp) begin

if(bit_cnt == 4'd13)

bit_cnt <= 0;

else

bit_cnt <= bit_cnt + 4'h1;

end

end

// ds串行输出

assign ds = ds_parallel[bit_cnt];

// stcp

always @(posedge clk, negedge rst_n) begin

if(!rst_n)

stcp <= 0;

else if(shcp && bit_cnt == 4'd13)

stcp <= 1'b1;

else

stcp <= 1'b0;

end

endmodule

随便写个tb仿真一下,传入位选6’b000111,段选8’hff:

`timescale 1ps/1ps

module dual_74hc595_ctrl_tb;

reg clk = 1'b1;

always #10 clk = ~clk;

reg rst_n = 1'b0;

reg [5:0] sel = 0;

reg [7:0] seg = 0;

initial begin

#30 rst_n = 1'b1;

#10000;

sel = 6'b000111;

seg = 8'hff;

#10000;

$stop(2);// $finish;

end

dual_74hc595_ctrl inst_dual_74hc595_ctrl(

.clk (clk),

.rst_n (rst_n),

.sel (sel),

.seg (seg),

.ds (ds),

.shcp (shcp),

.stcp (stcp),

.oe (oe)

);

endmodule

波形如下:

可以看出,在两次stcp上升沿中间,有14次shcp上升沿,ds上的数据分别是1、1、1、0、0、0、1…1,由于是右移,所以最先发送的ds是最低位,则这14位数据就是{8’hff, 6’b000111}。

顶层驱动模块

有了这个模块,FPGA就可以使用14位的位选+段选信号来驱动数码管了。

但位选+段选的方法依然不方便,要是能用6个4位bcd码驱动6个数码管,那就方便了。

需要再写一个驱动,将24位bcd码信号转化为14位位选+段选信号,每1.3ms显示一个数码管,如此快速的扫描加上数码管的余晖效应,人眼看起来6个数码管是同时点亮的,驱动代码如下:

module seg_driver(

input clk, // 50M

input rst_n,

// 6个4位bcd码,对应6个数码管

input [23:0] bcd_code,

// 74HC595 side

output ds,

output shcp,

output stcp,

output oe

);

// 5-0对应从左到右6个数码管

reg [5:0] sel;

// 7-0对应数码管a-g-dp

reg [7:0] seg;

// 约1.3ms计数器,每1.3ms只点亮一个数码管,达到动态显示效果

reg [15:0] scan_cnt;

always @(posedge clk, negedge rst_n) begin

if(!rst_n)

scan_cnt <= 0;

else

scan_cnt <= scan_cnt + 16'd1;

end

// 位选计数器

reg [3:0] sel_cnt;

always @(posedge clk, negedge rst_n) begin

if(!rst_n)

sel_cnt <= 0;

else if(&scan_cnt) begin

if(sel_cnt == 3'd5)

sel_cnt <= 0;

else

sel_cnt <= sel_cnt + 3'd1;

end

end

// seg and sel

always @(*) begin

case(sel_cnt)

3'd0 :begin

sel = 6'b100000;

seg = bcd_to_seg(bcd_code[23-:4]);

end

3'd1 :begin

sel = 6'b010000;

seg = bcd_to_seg(bcd_code[19-:4]);

end

3'd2 :begin

sel = 6'b001000;

seg = bcd_to_seg(bcd_code[15-:4]);

end

3'd3 :begin

sel = 6'b000100;

seg = bcd_to_seg(bcd_code[11-:4]);

end

3'd4 :begin

sel = 6'b000010;

seg = bcd_to_seg(bcd_code[7-:4]);

end

3'd5 :begin

sel = 6'b000001;

seg = bcd_to_seg(bcd_code[3-:4]);

end

default :begin

sel = 6'b111111; // 默认全显示

seg = 8'h03; // 默认0

end

endcase

end

// 数码管译码函数

function [7:0] bcd_to_seg;

input [3:0] bcd_code;

begin

case(bcd_code)

4'h0 : bcd_to_seg = 8'h03;

4'h1 : bcd_to_seg = 8'h9f;

4'h2 : bcd_to_seg = 8'h25;

4'h3 : bcd_to_seg = 8'h0d;

4'h4 : bcd_to_seg = 8'h99;

4'h5 : bcd_to_seg = 8'h49;

4'h6 : bcd_to_seg = 8'h41;

4'h7 : bcd_to_seg = 8'h1f;

4'h8 : bcd_to_seg = 8'h01;

4'h9 : bcd_to_seg = 8'h09;

default: bcd_to_seg = 8'h03; // 默认0

endcase

end

endfunction

// 74hc595驱动

dual_74hc595_ctrl inst_dual_74hc595_ctrl(

.clk (clk),

.rst_n (rst_n),

.sel (sel),

.seg (seg),

.ds (ds),

.shcp (shcp),

.stcp (stcp),

.oe (oe)

);

endmodule

上板验证

用这个驱动显示一下012345,顶层代码如下:

module seg_dynamic(

input clk,

input rst_n,

// 74HC595 side

output ds,

output shcp,

output stcp,

output oe

);

wire [23:0] bcd = {4'h0, 4'h1, 4'h2, 4'h3, 4'h4, 4'h5};

seg_driver inst_seg_driver(

.clk (clk),

.rst_n (rst_n),

.bcd_code (bcd),

.ds (ds),

.shcp (shcp),

.stcp (stcp),

.oe (oe)

);

endmodule