基于Xlinx的时序分析与约束(4)----主时钟约束

主时钟约束语法

主时钟约束,就是我们对主时钟(Primary Clock)的时钟周期进行约束(告诉综合工具布局布线的标准),这个约束是我们用的最多的约束了,也是最重要的约束。

主时钟必须与一个网表对象相连,该对象代表了所有时钟边沿的开始点,并且在时钟树中向下传递;也可以说,主时钟的源点定义了0时刻,Vivado靠此来计算时钟延迟和不确定性 ;vivado会忽略所有时钟树上从主时钟上游的单元到主时钟之间的延时!

主时钟通常有两个来源:(1)板级时钟(主要是晶振)通过输入端口进入FPGA;(2)FPGA的GT收发器的输出管脚(如恢复时钟)。

主时钟只能通过create_clock命令来定义,且必须放在约束的开始,这是因为其它时序约束几乎都要参考主时钟。其基本语法如下:

create_clock -name

-period -waveform { } [get_ports ]

- -name: 由设计者指定的主时钟名称,用于标识定义的主时钟,若不指定,则会默认使用

作为主时钟名称 - -period:是定义的主时钟周期,单位ns,取值必须大于0

- -waveform :{

}分别代表时钟的上升沿和下降沿,用于指定占空比和时钟相位,单位为ns;若不指定,则时钟占空比默认为50%且第一个上升沿为0时刻 - get_ports表示定义的主时钟的物理节点是FPGA的物理引脚;而GT收发器的引脚则使用get_pins来定义

例1:引脚输入的主时钟约束

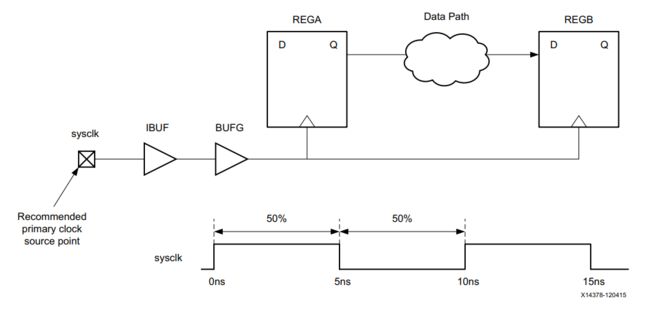

下图是一个从引脚sysclk进入FPGA的主时钟,其时钟周期为10ns,占空比50%且不存在相移。

根据主时钟约束的语法,其应该被约束为:

create_clock -period 10 [get_ports sysclk]

该语句定义了名为sysclk的物理节点产生的时钟sysclk,其时钟周期为10ns、占空比为50%(没有定义时的默认占空比)。需要注意的是,这个实例省去了主时钟的名称,以及省去了用 -waveform参数来描述其占空比与相位关系。

类似的,假设有一个外部时钟devclk通过ClkIn进入FPGA作为主时钟,其周期为10ns,占空比25%,相移90度。该时钟根据语法应该被约束为:

create_clock -name devclk -period 10 -waveform {2.5 5} [get_ports ClkIn]

该语句定义了名为ClkIn的物理节点产生的时钟devclk ,其时钟周期为10ns、占空比为50%,第一个上升沿在时刻2.5ns而第一个下降沿则在时刻5ns。

例2:高速收发器GT的恢复时钟

时钟源由高速收发器gt0提供,如下图所示:

进入FPGA,之后经过混合时钟管理单元MMCM生成其他时钟,以gt0发出的时钟为主时钟,其他生成时钟都有一个共同的时钟源,使用如下命令定义:

create_clock -name rxclk -period 3.33 [get_pins gt0/RXOUTCLK]

该语句定义了名为gt0/RXOUTCLK的物理节点产生的时钟rxclk,其时钟周期为3.33ns、占空比为50%(默认情况下的占空比)。

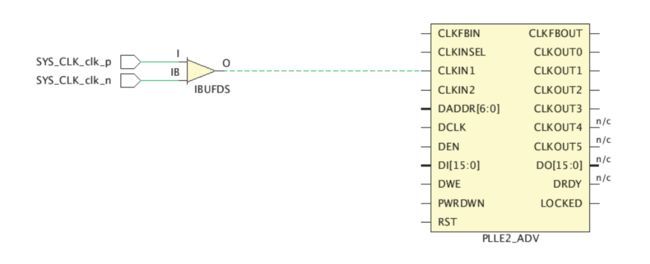

例3:差分时钟约束

差分时钟是指时钟是以差分形式(P端与N端)一起进入FGPA的时钟,比如差分晶振等,这种情况只需要约束差分时钟的P端即可,N端可以被vivado自动识别到。如果同时约束了正、负两端,反而会导致未知错误。

像上图这种差分时钟就可以这样约束(仅约束了P端):

create_clock -name sysclk -period 3.33 [get_ports SYS_CLK_clk_p]

主时钟约束实战

在了解了主时钟约束的语法后,我们接着来学习一下,如何具体地在vivado中使用它。

我们首先新建一个简单的工程,并实现以下代码(一个简单的两拍寄存器):

module test(

input sys_clk,

input in,

output out

);

assign out = out_rr;

reg out_r,out_rr;

always @(posedge sys_clk)begin

out_r <= in;

out_rr <= out_r;

end

endmodule由于vivado中的时序约束语句都是保存在XDC文件中,所以我们新建一个XDC文件用来保存我们的时序约束语句,步骤如下:

要实现主时钟约束的方法有好几种,但是不管是哪一种,最终的目的都是要把上面学到的主时钟约束语句给写入到XDC文件(timing.xdc)中去。

方法一:在Tcl窗口直接输入

直接在Tcl Console窗口输入主时钟约束语句:

create_clock -period 10.000 -name sysclk -waveform {0.000 5.000} [get_ports sys_clk]

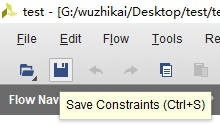

然后点击vivado左上角的保存约束按钮,将其保存到对应的XDC文件中:

此时,再打开timing.xdc文件,就已经出现了主时钟约束语句:

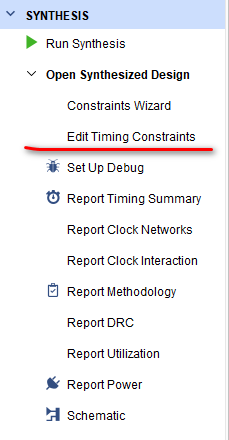

方法二:GUI界面输入

可能有时候不太记得主时钟约束语句的语法,没有关系,我们可以使用GUI界面来创建该语句。

GUI界面使用简单方便,是个非常好的人机交互。在创建了XDC文件后,把工程综合完成,点击 edit timing constraints,打开时序约束编辑界面:

左侧是约束分类区,展示了各种各样的时序约束;右侧是对应的约束编辑区 ;下方是已有的约束的展示区域。

先选择左侧的“create clock”后点击约束编辑区的+号,编辑一条新的主时钟约束语句(信息对应着填一下就可以了,没啥好说的):

此时vivado左侧的保存约束按钮又可以按下了,按下将这一条语句保存:

此时,再打开timing.xdc文件,就已经出现了主时钟约束语句:

- 博客主页:wuzhikai.blog.csdn.net

- 本文由 孤独的单刀 原创,首发于CSDN平台

- 您有任何问题,都可以在评论区和我交流!

- 创作不易,您的支持是我持续更新的最大动力!如果本文对您有帮助,还请多多点赞、评论和收藏⭐!