Xilinx时序分析学习和非同步时钟如何设置constraints

XDC的基本语法

《ug903 Vivado Design Suite User Guide Using Constraints》

XDC的基本语法可以分为时钟约束、I/O约束以及时序例外约束三大类。

时钟约束

时钟约束必须最早创建,对7系列FPGA来说,端口进来的主时钟以及GT的输出RXCLK/TXCLK都必须由用户使用create_clock自主创建。

FPGA PL时钟用户可在GUI界面创建。

而衍生时钟则分为以下两类:

create_generated_clock [-name arg] [-source args] [-master_clock arg]

时序例外约束

The priority rule for the objects is:

- Ports, pins, and cells

Pins of a cell are used instead of the cell itself. - Clocks

Clocks always have lower priority than ports, pins, and cells. A timing exception that

uses clock object(s) always has a lower priority than another timing exception defined

with ports, pins, and cells.

The precedence rule for the filters, from highest to lowest, is: - -from -through -to

- -from -to

- -from -through

- -from

- -through -to

- -to

- -through

时钟定义的先后顺序

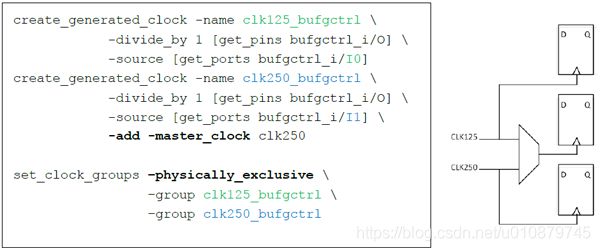

时钟的定义也遵从XDC/Tcl的一般优先级,即:在同一个点上,由用户定义的时钟会覆盖工具自动推导的时钟,且后定义的时钟会覆盖先定义的时钟。若要二者并存,必须使用 -add 选项。

异步时钟组

set_clock_group -name asyn_clocks -asynchronous -group clk1 -group -clk2

物理唯一时钟

还有一个 -logically_exclusive, -physically_exclusive, 二者作用相同。

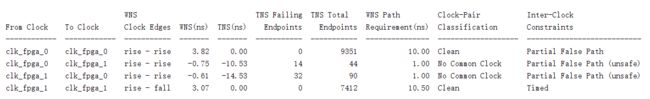

跨域时钟分析报告

report_clock_interaction

如果两个时钟连“Common Primary Clock”也不共享,则100%可以确认为异步时钟,应该加上相应的时钟关系约束。

显示为“Unexpanded”的时钟关系,表示Vivado在一定长度(缺省为1000)的周期内都没有为两个时钟的频率和相位找到固定的关系,则无法推导出相应的Path Req 约束值。此类CDC需要特别留意,也要加上异步时钟关系约束。

(123条消息) XDC约束技巧之时钟篇_坚持-CSDN博客 https://blog.csdn.net/wordwarwordwar/article/details/79183764

CDC的定义与分类

CDC是Clock Domain Crossing的简称,CDC时序路径指的是起点和终点由不同时钟驱动的路径。

安全的CDC路径

所谓安全的CDC路径是指那些源时钟和目标时钟拥有相同的来源,在FPGA内部共享部分时钟网络的时序路径。这里的安全指的是时钟之间的关系对Vivado来说是全透明可分析的。

set_max_delay $delay –from [get_cells cell1] –to [get_cells cell2] –datapath_only

set_max_delay -from [get_cells ……/rd_pntr_gc_reg[]] -to [get_cells ……/Q_reg_reg[]]

-datapath_only [get_property PERIOD $rd_clock]

set_max_delay -from [get_cells ……/wr_pntr_gc_reg[]] -to [get_cells ……/Q_reg_reg[]]

-datapath_only [get_property PERIOD $wr_clock]

EETOP 赛灵思(Xilinx) 社区 http://xilinx.eetop.cn/viewnews-2363

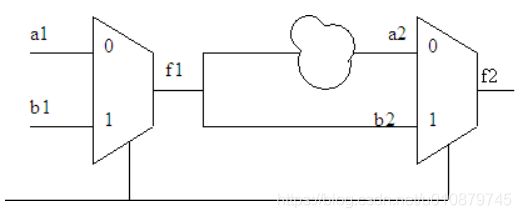

As we can see from the diagram, it is logically impossible from a1, through f1 and b2, to f2. It also logically impossible from b2, through f1 and a2, to f2. In such cases, we can use PrimeTime command set_false_path to disable the timing paths…

set_false_path -through a1 -through b2

set_false_path -through b1 -through a2

A false path can also be a path cross asynchronous clock domains. Let’s assuming clk1 is asynchronous to clk2, we can also disable the false paths like following.

set_false_path -from [get_clocks clk1] -to [get_clocks clk2]

set_false_path -from [get_clocks clk2] -to [get_clocks clk1]

《ug903 Vivado Design Suite User Guide Using Constraints》

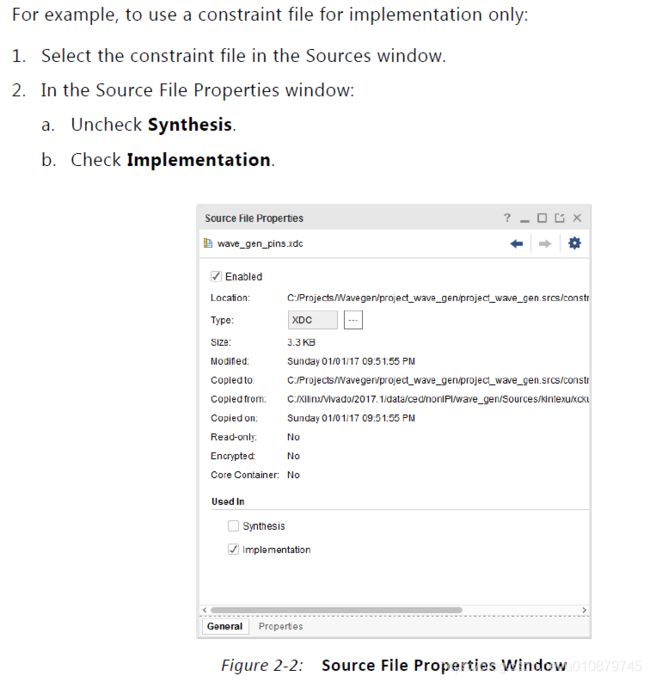

将constraits指定综合使用

add_file constraints_ooc.xdc

set_property USED_IN {synthesis out_of_context} [get_files constraints_ooc.xdc]

The equivalent Tcl commands are:

set_property USED_IN_SYNTHESIS false [get_files wave_gen_pins.xdc]

set_property USED_IN_IMPLEMENTATION true [get_files wave_gen_pins.xdc]

Recommended Constraints Sequence

RECOMMENDED: Whether you use one or several XDC files for your design, organize your constraints

in the following sequence.

## Timing Assertions Section

# Primary clocks

# Virtual clocks

# Generated clocks

# Clock Groups

# Bus Skew constraints

# Input and output delay constraints

## Timing Exceptions Section

# False Paths

# Max Delay / Min Delay

# Multicycle Paths

# Case Analysis

# Disable Timing

## Physical Constraints Section

# located anywhere in the file, preferably before or after the timing constraints

# or stored in a separate constraint file

set_property PROCESSING_ORDER EARLY [get_files wave_gen_pins.xdc]

同步器

all synchronizer flip-flops have their ASYNC_REG property set to true in order to preserve the synchronizer cells through any logic optimization during synthesis and implementation

impact on synthesis results:

• create_clock

• create_generated_clock

• set_input_delay

• set_output_delay

• set_clock_groups

• set_false_path

• set_max_delay

• set_multicycle_path

based on the utilization

of the Elaborated design to find the object names in your design that you want to constrain

for synthesis.

Before proceeding to implementation, you must verify that your design does not include any major timing violation.

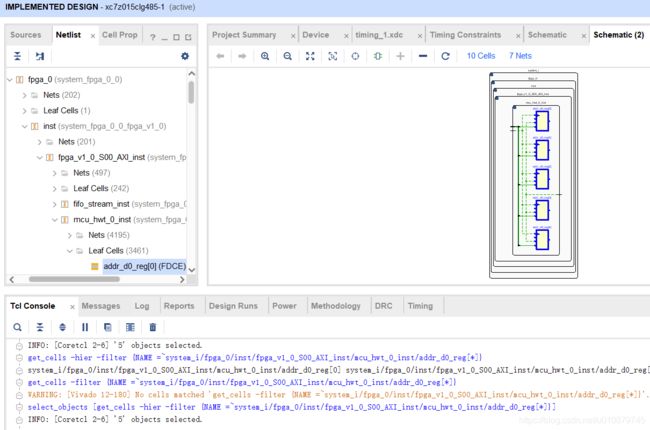

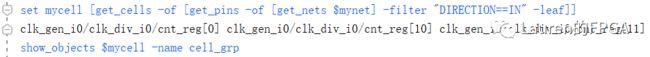

查找目标

如何快速查找目标cell - 云+社区 - 腾讯云 https://cloud.tencent.com/developer/article/1572984

This option works for both flat and hierarchical netlists:

% get_cells inst_A/inst_B/reg

% get_cells inst/inst_B/control_reg

• Another option is:

% get_cells -hier -filter {NAME =~ inst_A/inst_B/reg}

% get_cells -hier -filter {NAME =~ inst/inst_B/control_reg}

To apply some XDC constraints to all the instances of the original RTL module, the

property ORIG_REF_NAME should be used instead of the property REF_NAME. For example:

[get_cells -hierarchical -filter {ORIG_REF_NAME ==uart_tx_ctl}]

Xilinx recommends that you do the following:

• Use get_* commands without the -hierarchical option.

• Mark explicitly with the forward-slash (/) character all the levels of hierarchy as they show in the elaborated design view.

Examples Without Hierarchical Option:

• This option works for both flat and hierarchical netlists:

% get_cells inst_A/inst_B/reg

% get_cells inst/inst_B/control_reg

• Another option is:

% get_cells -hier -filter {NAME =~ inst_A/inst_B/reg}

% get_cells -hier -filter {NAME =~ inst/inst_B/control_reg}

get_nets laser_power_out_1[*]

get_cells -of laser_power_out_1[0]

Recommended Pin Queries

Original pin query:

get_pins –hier * -filter {NAME=~xx*/yy*}

Recommended efficient pin query:

get_pins –filter {REF_PIN_NAME=~yy*} –of [get_cells –hier xx*]

Alternate recommended pin query:

get_pins –filter {REF_PIN_NAME=~yy*} –of [get_cells –hier * -filter {NAME=~xx*}]

Example

For example, consider the following constraint:

set_max_delay 15 -from [get_pins -hier -filter {NAME=~/aclk_dpram_reg//CLK}] -to [get_cells -hier -filter {NAME=~/bclk_dout_reg*}] -datapath_only

The constraint above can be re-written as follows to significantly improve the query runtime, especially for larger designs:

set_max_delay 15 -from [get_pins -of [get_cells -hier –filter {NAME =~ aclk_dpram_reg/}] -filter {REF_PIN_NAME == CLK}]

-to [get_cells -hier bclk_dout_reg] -datapath_only

get_selected_objects

{system_i/fpga_0/inst/fpga_v1_0_S00_AXI_inst/mcu_hwt_1_inst/laser_power_out_reg[7]} …

select_objects [get_cells system_i/fpga_0/inst/fpga_v1_0_S00_AXI_inst/mcu_hwt_1_inst]

select_objects [get_cells system_i/fpga_0/inst/fpga_v1_0_S00_AXI_inst/mcu_hwt_0_inst/addr_d0_reg[]]

select_objects [get_cells -hier -filter {NAME =~system_i/fpga_0/inst/fpga_v1_0_S00_AXI_inst/mcu_hwt_0_inst/addr_d0_reg[]}]

设变量

set myobj [get_selected_objects]

show_objects $myobj -name test

report_compile_order -constraints

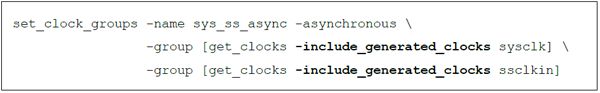

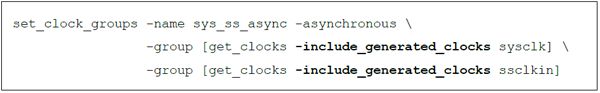

两个主时钟ssclkin和sysclk由不同的端口进入FPGA,再经由不同的时钟网络传递,要将它们设成异步时钟,可以使用如下约束:

异步时钟组:

set_clock_groups -asynchronous -group clkA -group clkB

set_clock_group -name asyn_clocks -asynchronous -group clk1 -group -clk2

set_clock_groups -asynchronous -group FCLK_CLK0 -group FCLK_CLK1

![]()

set_false_path

逐条进行时序例外约束

set_false_path -through a1 -through b2

set_false_path -through b1 -through a2

set_false_path -from [get_cells a/b/c/_meta] -to [get_cells a/b/c/_sync]

A false path can also be a path cross asynchronous clock domains. Let’s assuming clk1 is asynchronous to clk2, we can also disable the false paths like following.

set_false_path -from [get_clocks clk1] -to [get_clocks clk2]

set_false_path -from [get_clocks clk2] -to [get_clocks clk1]

set_max_delay

set_max_delay 10 -datapath_only -from clkA -to clkB

set_max_delay 12 -from [get_clocks clk1] -to [get_clocks clk2]

set_max_delay 15 -from [get_clocks clk1]

set_max_delay -from [get_cells ……/rd_pntr_gc_reg[]] -to [get_cells ……/Q_reg_reg[]]

-datapath_only [get_property PERIOD $rd_clock]

set_max_delay -from [get_cells ……/wr_pntr_gc_reg[]] -to [get_cells ……/Q_reg_reg[]]

-datapath_only [get_property PERIOD $wr_clock]

set_multicycle_path

set_multicycle_path -from [get_cells rega] -to [get_cells regb] -setup -end 2

set_multicycle_path -from [get_cells rega] -to [get_cells regb] -hold -end 1

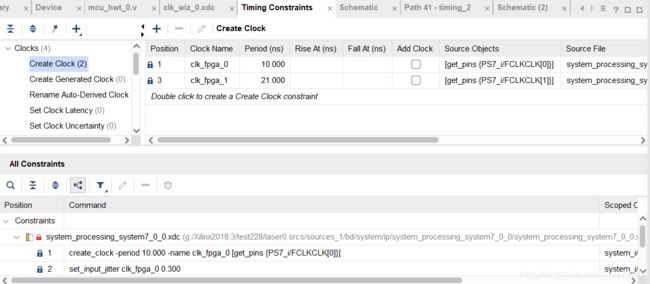

发现Timing Constraints文件

double click Edit Timing Constraints

g:/Xilinx2018.3/test228/laser0.srcs/sources_1/bd/system/ip/system_processing_system7_0_0/system_processing_system7_0_0.xdc

create_clock -name clk_fpga_0 -period “10” [get_pins “PS7_i/FCLKCLK[0]”]

set_input_jitter clk_fpga_0 0.3

#The clocks are asynchronous, user should constrain them appropriately.#

create_clock -name clk_fpga_1 -period “21” [get_pins “PS7_i/FCLKCLK[1]”]

set_input_jitter clk_fpga_1 0.63

修改

右下角右键鼠标

选第二项或第三项,设异步时钟组或最大时延

set_clock_groups -asynchronous -group [get_clocks clk_fpga_1] -group [get_clocks clk_fpga_0]

set_max_delay -datapath_only -from [get_clocks clk_fpga_1] -to [get_clocks clk_fpga_0] 10.0

get_property PERIOD [get_clocks clk_fpga_0]

10.000

get_property PERIOD [get_clocks clk_fpga_1]

21.000

set clk_fpga_0 [get_clocks clk_fpga_0]

clk_fpga_0

get_property PERIOD $clk_fpga_0

10.000

重置时间constraints

reset_timing

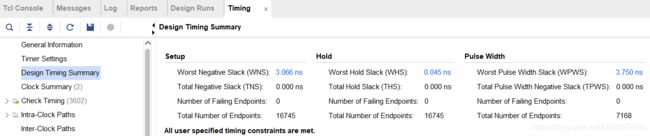

After systhesis

After implementation

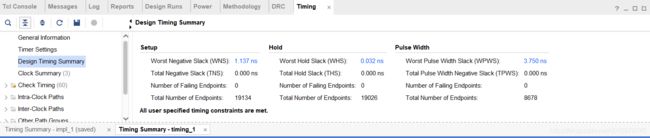

如果只放松时序单向,则仍有一个方向时序超标

set_max_delay -datapath_only -from [get_clocks clk_fpga_0] -to [get_clocks clk_fpga_1] 10.0

从fpga_0到fpga_1已指标放松,现在出问题是fpga_1出,fpga_0入

constraints file

#set_clock_groups -asynchronous -group [get_clocks clk_fpga_1] -group [get_clocks clk_fpga_0]

#set_max_delay -datapath_only -from [get_clocks clk_fpga_1] -to [get_clocks clk_fpga_0]

set_max_delay -datapath_only -from [get_clocks clk_fpga_0] -to [get_clocks clk_fpga_1] [get_property PERIOD [get_clocks clk_fpga_0]]

set_max_delay -datapath_only -from [get_clocks clk_fpga_1] -to [get_clocks clk_fpga_0] [get_property PERIOD [get_clocks clk_fpga_0]]