IBM有望在2026年之前实现量子优势

(图片来源:网络)

目前,噪声是量子计算面临的最大挑战,限制了量子计算技术的快速发展。在未来几年内,IBM正努力通过各种类型的量子误差管理来减少噪声,直到实现真正的量子纠错 (QEC)。

这也是降低噪音的重要性。量子比特(qubit)是量子计算机的基本信息单位,一个量子比特能保持其量子态的时间越长,它能执行的计算操作就越多。但是量子比特对环境噪声非常敏感,这些噪声可能来自量子计算机的控制电子设备、布线、低温、其他量子比特、热量,甚至是宇宙辐射等外部因素。噪声会导致量子比特的量子态崩溃(一种称为退相干的情况),从而产生错误。一个未纠正的错误可能会级联成大量错误并破坏整个计算。这种噪声源于原子层面,虽然无法完全消除,但可以控制。

量子优势和噪音

毫无疑问,量子计算机具有无可争辩的优势。大多数专家认为,与传统超级计算机相比,量子计算展示其优越性只是时间问题。届时,量子计算将实现“量子优势”。

IBM将量子优势定义为:在实际案例中,相对于最佳经典算法,量子算法运行时间实现了显著改进。这也证明量子优势所需的算法必须具有量子电路,经典算法无法有效模拟这些电路。

问题在于:要使量子计算机获得量子优势,除了提高量子比特相干性、门保真度和电路执行速度外,还必须显著增加计算量子比特数。但是增加量子比特的数量也会增加噪声和量子比特错误。因此,管理噪声和量子比特错误对于量子计算的长期发展至关重要。

尽管纠错在经典计算机和某些类型的内存硬件中很常见,但我们不能在量子计算机中使用相同的技术,因为按照量子力学定律,克隆未知的量子态是不可能。

量子纠错 (QEC) 是一个复杂的工程和物理问题。迄今为止,科学家们已经投入了大量时间寻找解决方案,但量子纠错仍然难以捉摸,似乎还需要很多年的时间。在完全纠错之前,IBM正在研究其他误差管理解决方案。

量子误差管理

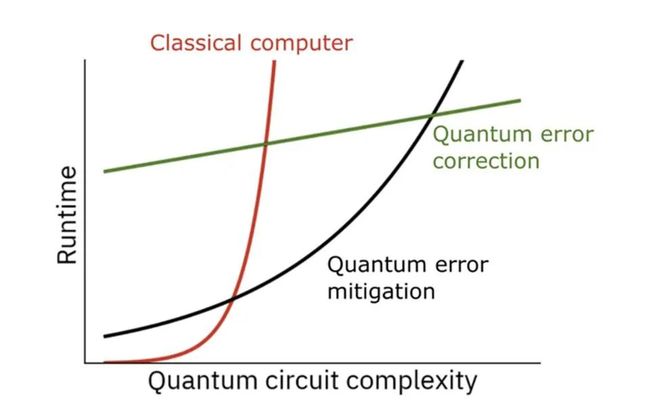

在量子纠错发挥实用性之前,量子误差校正将填补空白(图片来源:网络)

上面的IBM图表将减少误差的量子电路的指数缩放与经典计算机的指数缩放进行了比较。交叉点是校正量子误差与经典解决方案相比更具优势的转折点。

IBM在纠错研究方面有着悠久的历史,从1996年David DiVincenzo的调查开始。2015年,它开发了第一个检测量子比特翻转和相位翻转误差的系统。如今,由于量子纠错的重要性,几乎每个企业和学术量子计算项目都在进行某种形式的纠错研究。

目前,IBM通过三种方法来研究量子误差管理:误差抑制、误差缓解和误差校正。暂且不谈误差纠正,先说说误差抑制和误差缓解。

误差抑制是最早也是最基本的错误处理方法之一。它通常会修改电路,使用能量脉冲使量子比特保持更长时间的量子态,或将脉冲引导到空闲量子比特,以消除由相邻量子比特引起的任何不良影响。这种误差抑制称为动态解耦。

IBM认为,误差缓解将弥合当今容易出错的硬件与未来的容错量子计算机之间的差距。误差缓解的短期目标是使量子优势早日实现。

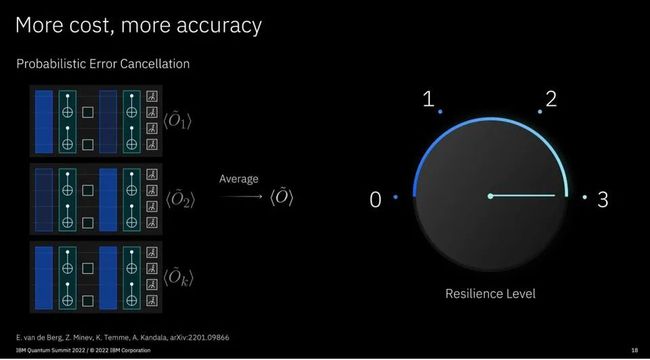

IBM所做的持续误差缓解研究比其他任何机构都多。通过这项工作,IBM开发了多种误差缓解方法,包括概率错误消除(PEC)和零噪声外推(ZNE)。

PEC的功能很像降噪耳机,提取和分析噪声,然后在与原始噪声信号混合之前反转以消除它。但显著区别之一是,它不像音频降噪算法那样使用单个样本,而是使用从一组电路计算的平均值。

ZNE通过在不同噪声水平下,运行量子程序来降低量子电路中的噪声,然后外推计算以确定零噪声水平下的估计值。

有效的量子纠错将消除几乎所有与噪声相关的误差。值得注意的是,随着代码数量的增加,QEC以指数方式抑制误差。在任何有限的代码下,错误将始终存在。为了获得最佳结果,重要的是选择一个代码来抑制误差,使其刚好适合目标应用程序。

在QEC可用之前,量子误差缓解提供了实现量子优势的最快途径。

(图片来源:网络)

最近,IBM宣布将误差抑制和误差缓解集成到 Qiskit Runtime primitives Sampler 和 Estimator 中。作为测试版功能,可以使用户以速度换取更少的错误。在IBM的路线图中,预计这些功能的最终版本将在2025年发布。

存在与编译、执行和误差缓解技术的经典后处理相关的开销。开销的多少取决于所使用的误差缓解类型。IBM引入了一个新的简化选项,称为“弹性级别”,用户在其工作所需的成本和准确性之间调整权衡。采样器和估算器将自动对优化级别1到3的电路应用动态解耦误差抑制。Resilience 0不提供任何误差缓解,Resilience 1是测量误差缓解,Resilience 2提供有偏误差缓解(通过 ZNE),Resilience 3启用无偏估计器(通过 PEC)。

所有可通过云访问的IBM系统都将提供误差缓解功能。随着弹性数字的增加,成本也会增加。Resilience 3产生的错误最少,但可能需要100,000倍以上的计算时间。

IBM Quantum平台负责人Blake Johnson博士解释了IBM实施此误差缓解服务选项的基本原理:“我们有一些非常高级的用户,他们想自己做所有事情,他们不希望我们接触他们的电路。但我们也看到越来越多的用户像看待烤面包机一样看待量子计算机。他们不明白它是如何运作的。他们只想按下一个按钮,就可以达到想要的结果。因此,我们决定将某些内容设为默认值,前提是它没有采样开销,并且没有额外的运行成本。”

量子纠错

得益于整个量子计算社区开展的纠错研究,过去十年间,QEC取得了重大进展。即便如此,可能还需要多年的研究,才能找到可行的解决方案。

量子纠错的早期挑战之一:是在不破坏量子比特的量子态的情况下,通过测量它来识别错误。1995年,Peter Shor开发了一个突破性的解决方案来规避这个问题。Shor的系统不是将量子状态存储在单个量子比特中,而是将量子信息编码为分布在9个物理量子比特上的逻辑量子比特。该方案能够通过监测系统的奇偶校验来检测错误,而不是通过直接测量来破坏量子态。

目前,IBM正在研究多种量子纠错方法,包括一些类似于Shor代码的方法。这类纠错码称为量子低密度奇偶校验(qLDPC)。LDPC并不新鲜。它用于许多经典的纠错应用,例如Wi-Fi和5G。

据IBM称,qLDPC具有以下优势:

(1)每个逻辑量子比特只需要几个物理量子比特,而不是二维表面代码所需的数百个。

(2)如果发生错误操作,只会暴露有限数量的量子比特。

量子纠错的研究机会和各种方法太多了,无法一一介绍,有很多选择是好事,如果要实现容错量子计算机,就必须找到纠错的解决方案,我们拥有的选择越多,机会就越大。

IBM的量子路线图反映了问题的复杂性。它显示:纠错解决方案将在2026年之后的某个时间可用。实际上,这可能还需要几年时间。

总结

(1)随着量子硬件的不断改进,IBM实施的量子误差缓解将会促进实现早期量子优势。目前,误差缓解的运行时间呈指数级增长,受所需量子比特数量和电路深度的影响。但是,速度、量子比特保真度和误差缓解方法的改进有望大大减少这种开销。

(2)IBM的误差缓解目标是为误差校正提供持续的开发路径。一旦实现QEC,就能构建容错量子计算机,在以量子为中心的超级计算环境中运行数百万个量子比特。这些机器将能模拟大型多体系统,优化复杂的供应链物流,创造新的药物和材料,对复杂的金融市场行为进行建模和反应等等。

(3)容错量子计算机标志着以量子为中心的科学研究新时代已经到来。这种新能力可以改变世界。

分析师笔记

(1)Quantinuum 最近发布了两个重要的QEC概念验证。它的研究人员开发了一种逻辑纠缠电路,其保真度高于其物理对应电路。研究人员还以完全容错的方式纠缠了两个逻辑量子比特门。

(2)IBM宣布,动态电路也将可用于其系统以及误差缓解。动态电路有望在量子低密度奇偶校验 (qLDPC) 纠错码中发挥重要作用。

(3)为了实现量子优势,IBM 开始使用最近发布的433量子比特处理器Osprey来扩展。Osprey的量子比特比当前的127量子比特Eagle 处理器多3倍。

(4)除了IBM的误差抑制和误差缓解计划外,以下是IBM量子路线图中的主要亮点,它们提供了实现量子优势的途径:

2023年,随着Condor处理器的发布和进一步扩展到1121个量子比特。提高全系统速度和质量的目标也在继续。

2024年,IBM将开始集成和测试支持未来扩展的关键技术,例如经典并行化、耦合器、多芯片量子处理器和量子并行化。

2025年,模块化量子硬件、新控制电子设备和低温基础设施,这些是近期实现量子优势所需的最终硬件。

2026年,将未来系统扩展到10K–100K量子比特。到那时,它还可以显著提高系统速度和质量。量子误差缓解的成熟落地将实现量子优势,同时,量子纠错也将取得重大进展。

编译:卉可

编辑:慕一