傻白探索Chiplet,关于EPYC Zen2 的一些理解记录(五)

目录

一、知识铺垫

(1)Chiplet

(2)Zen架构

(3)EPYC和Ryzen

(4)EPYC Zen2

二、关于EPYC Zen2里的部件

(1)内存控制器

(2)PCIe控制器

(3)Infinity Fabric总线

(4)关于CCX和CCD

(5)关于64核心128线程

三、关于EPYC Zen2的架构

(1)升级核心微架构,IPC大幅提升

(2)革命性的分离式设计

(3)更加可靠的安全性

(4)大幅提升内存频率和带宽

(5)率先支持PCIe 4.0

四、关于EPYC Zen2的性能

中国工程院院士许居衍在题为《复归于道:封装改道芯片业》的报告中指出,经典的2D缩放已经“耗尽”了现有的技术资源,现在通过节点实现性能翻番的方法已经失灵。单片集成电路过去一向强调PPA,即更高的性能(erformance)、更低的功耗(Power)、更小的面积(Area),现在转向关注PPC+(性能、功耗、成本、etc.)。这个逻辑方向到了需要修正的时候了!因此3D异质集成、MCP(Multi-Chip Package多芯片封装)、SiP(System-in-Package)、PoP(Packaging on Packaging)等封装技术成为走出2D同质集成的契机。3D异质集成的基础就是IP复用。许居衍院士在报告中非常看好3D异质集成技术的潜力。

一、知识铺垫

(1)Chiplet

简而言之,Chiplet其实就是一颗商品化的、具有功能(如USB、存储器)特征的裸芯片(die)。从系统端出发,首先将复杂功能进行分解,然后开发出多种具有单一特定功能,可相互进行模块化组装的裸芯片,如实现数据存储、计算、信号处理、数据流管理等功能,并最终以此为基础,建立一个Chiplet的芯片网络(未来的电脑系统可能只包含一个CPU芯片和几个GPU,这些GPU都连接到Chiplet上,形成芯片网络)。

理论上,Chiplet模式是一种开发周期短且成本较低的方法,提供了先进工艺和主流成熟工艺选择的灵活性,可以将不同节点工艺(10nm、14/16nm及22nm)、不同材质(硅、砷化镓、碳化硅、氮化镓)、不同功能(CPU、GPU、FPGA、RF、I/O、存储器)、不同半导体公司的芯片封装在一起。

(2)Zen架构

Zen是AMD公司的微处理器架构,是AMD在2016年推出的新一代处理器架构。Zen架构的目标是提供高性能和高效率,其采用了新的架构设计方法,包括“模块化”设计方法和高密度缓存体系结构,这使得Zen架构的处理器在单核心和多核心方面都具有良好的表现。Zen架构的处理器主要用于桌面和服务器市场,包括AMD的Ryzen和EPYC产品线。Zen架构的后续版本包括Zen+和Zen 2。

(3)EPYC和Ryzen

EPYC和Ryzen是AMD公司生产的两种处理器产品线,分别采用Zen架构设计并生产。

- EPYC(Enterprise Processor for You Compute)是AMD面向企业市场的高性能处理器产品线,主要用于服务器和工作站系统。它的名字“霄龙”来源于希腊神话中的天神霄龙,意味着高性能和强大。

- Ryzen(pronounced "RYE-zen")是AMD面向桌面市场的处理器产品线,主要用于桌面电脑系统。它的名字“锐龙”来源于希腊神话中的海神锐龙,意味着高性能和灵活。

总的来说,EPYC和Ryzen的主要区别在于它们面向的市场不同,EPYC主要面向企业市场,而Ryzen主要面向桌面市场。另外,EPYC的性能和可扩展性通常会比Ryzen更高。

话说到这儿,可能还有些入门憨憨不知道服务器和工作站有啥区别,服务器和工作站是两种不同类型的计算机:

- 服务器是专门用于提供网络服务的计算机,其主要功能是存储数据、运行服务程序和为其他计算机提供资源。服务器通常具有高性能、高容量的硬件设备,并且有能力承受大量并发连接。

- 工作站是个人用户使用的计算机,主要用于办公、设计、开发等工作。工作站通常没有服务器那么高的性能和容量,但是一般具有更好的图形处理能力和用户界面,方便用户使用。

因此,服务器主要用于提供服务,而工作站则用于工作。

(4)EPYC Zen2

EPYC Zen 2是AMD公司生产的一款微处理器,是公司的第二代EPYC处理器。EPYC Zen 2处理器采用7nm工艺制造,支持多达64核心128线程的多核处理器,具有更高的性能和更低的功耗。这款处理器被广泛应用于服务器和工作站计算机中,并且也可以用于高端个人电脑。EPYC Zen 2处理器拥有更高的性能,可以支持更复杂的计算任务,并且具有更低的功耗,可以提高系统的效率。

二、关于EPYC Zen2里的部件

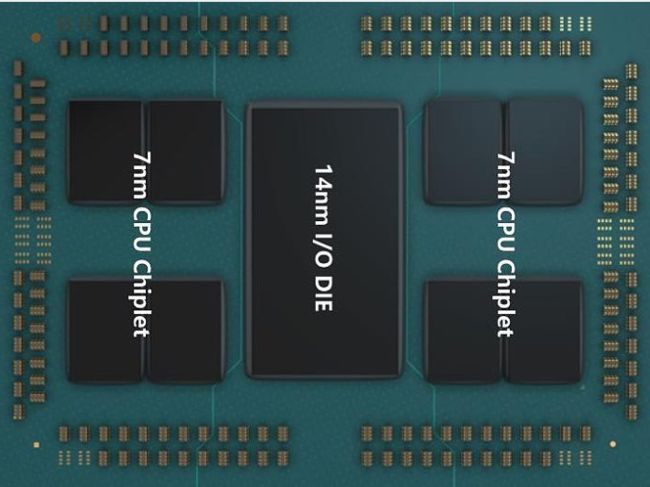

AMD推出使用Chiplet技术生产的代号为“罗马Rome”的第二代霄龙EYPC Zen2架构CPU芯片,内部最多八个7nm CPU裸芯片和一个14nm I/O裸芯片,其中前者只有CPU核心、各级缓存和Infinity Fabric总线端口,得益于新工艺可以获得更小面积、更强性能、更低功耗。后者专门独立出来,集成输入输出、内存控制器、PCIe控制器和Infinity Fabric总线端口,可以更方便、更高效地处理各个CPU核心、不同处理器的互连,而工艺之所以采用14nm,是因为它对新工艺不敏感,老工艺则更加成熟,成本也更低,符合不同IP采用最合适工艺的Chiplet设计原则。

二代霄龙也采用了chiplet小芯片设计,基础单元还是CCX(Core Complex),每个CCX包含4个核心(8个线程),然后两个CCX组成一个CCD(Core Complex Die),也就是一个CPU Die,包含8个核心(16个线程),然后每颗处理器包含多个CPU Die,最多8个组成64个核心(128个线程)。

(1)内存控制器

内存控制器是用来管理计算机内存的硬件设备。它的主要功能是负责将计算机的存储器(如内存、硬盘、SSD等)与处理器连接起来,并负责管理数据在存储器和处理器之间的传输。

内存控制器通常包括以下功能:

- 内存地址管理:负责维护内存地址映射表,将计算机的逻辑地址转换为物理地址。

- 内存读写:负责将数据从内存中读出或写入内存。

- 内存缓存:负责在内存和处理器之间建立一个缓存层,以加快数据传输的速度。

- 内存页管理:负责维护内存分页表,并负责处理内存页的交换和换入换出。

总的来说,内存控制器是计算机内存管理的重要组成部分,负责管理数据在内存和处理器之间的传输,以及维护内存地址映射和内存分页表,从而保证计算机系统的正常运行。

(2)PCIe控制器

PCIe(Peripheral Component Interconnect Express)控制器是一种用于连接计算机的外围设备的控制器。它是PCI(Peripheral Component Interconnect)总线的扩展版本,具有更快的数据传输速度和更高的带宽。

PCIe控制器的主要功能是负责将计算机的外围设备连接到计算机的主板上。它可以通过PCIe总线与外围设备进行数据传输,并负责管理数据在计算机和外围设备之间的传输。常见的外围设备包括显卡、网卡、声卡、硬盘、SSD、打印机等。使用PCIe控制器可以将这些外围设备与计算机连接起来,使得计算机能够使用这些设备的功能。

(3)Infinity Fabric总线

Infinity Fabric 是AMD公司开发的一种总线架构,用于在AMD处理器中连接不同的组件。

Infinity Fabric总线是AMD处理器的内部总线,用于连接处理器内部的不同组件,如CPU核心、显卡、内存控制器等。它具有高带宽、低延迟和良好的可扩展性,可以支持多种处理器架构。

Infinity Fabric总线的主要优点在于它可以提供高带宽和低延迟的数据传输,从而提高处理器的性能。此外,它还具有良好的可扩展性,可以支持不同的处理器架构,使得AMD处理器能够适应不同的应用场景。

(4)关于CCX和CCD

我当时思考了一下“为啥有了CCX还要CCD呢?”

- CCX(Core Complex)是AMD公司在芯片设计中使用的一种基础单元,包含多个CPU核心,负责处理计算机的基本运算操作。

- CCD(Core Complex Die)是AMD公司在芯片设计中使用的一种单元,由两个CCX组成,包含多个CPU核心,负责处理计算机的基本运算操作。

为什么需要CCD呢?原因是CCX作为一种基础单元,包含的CPU核心数量相对较少,无法满足对多核心处理器的需求。而CCD则是由两个CCX组成,包含更多的CPU核心,可以满足对多核心处理器的需求。

“ 那为啥不直接一个CCX装8个核心呢?”

首先,在计算机系统中,核心群越大,互连实现越复杂,延迟也会增加。具体来说,核心群越大,在核心之间进行数据交换和指令同步的时间就会增加,从而导致系统的总体性能下降。因此,在芯片设计中,设计人员通常会考虑如何在保证足够的性能的同时尽量减小核心群的大小,以提高处理器的效率

(5)关于64核心128线程

通常情况下,计算机处理器的核心数和线程数是相同的,因为每个核心都可以执行一个线程。但是,有些处理器具有超线程技术,可以在单个核心内同时执行两个线程。这样,32核心的处理器就可以支持64个线程。

超线程技术的工作原理是,当一个核心的一个线程需要等待某些资源(例如数据或者I/O操作)时,处理器会将该线程挂起,并让另一个线程使用该核心。这样,单个核心就可以同时执行两个线程,从而提高系统的性能。但是,超线程技术并不能真正提高单个核心的计算能力,而是通过调度多个线程来提高系统的整体性能。

三、关于EPYC Zen2的架构

除了制造工艺(7nm)上的优势之外,第二代AMD EPYC(霄龙)系列处理器最重要的革新其实是其核心基于Zen 2架构。相较于上一代产品所采用的Zen架构,Zen 2架构在各方面都进行了增强。其中最核心的有两个部分:一是核心微架构升级,二是计算单元和I/O单元的分离。

(1)升级核心微架构,IPC大幅提升

3.1.1 Tage分支预测器的改进

TAGE分支预测器是一种特定类型的预测器,它使用了一种叫做TAGE的技术来预测控制流分支(例如if语句)的执行情况,用于在处理计算机程序的流水线中预测下一个指令将被执行,用于提高计算机程序的执行效率。 它通常用于处理器中,帮助预测哪些指令将被执行,从而减少流水线中的停顿。

TAGE分支预测器通过跟踪程序的历史来预测分支的执行情况。 它使用一个哈希表来存储历史信息,并使用这些信息来预测下一个分支的执行情况。 当预测不准确时,TAGE分支预测器会调整其内部的参数,以便在下一次预测时更准确。

Zen 2采用了更优良的TAGE分支预测器和更大的运行缓存,大幅改进了分支预测功能,全新的TAGE分支预测器相比上一代的Perceptron,在各级指令缓存,微操作缓存以及L1 cache的关联宽度等方面几乎都是翻倍的,预测失败的几率降低了三分之一。无论利用效率、指令融合效率和有效吞吐量都更好。

3.1.2 AGU单元数量提升

AGU单元(Address Generation Unit)是一种处理器的硬件单元,用于生成和管理内存地址。它主要用于执行加载和存储指令,例如在处理器的寄存器中读取数据并将其存储到内存中,或者从内存中读取数据并将其存储到寄存器中。AGU单元可以帮助处理器快速访问内存中的数据,提高处理器的性能。

在整数运算单元上,Zen 2架构的ALU数量没有变,但是管理数据载入和存储指令的AGU单元从2个提升到了3个,并提升了各种缓存大小,增强了ALU、AGU的调度能力,使其更加合理。

3.1.3 浮点运算单元的数据路径宽度翻倍

浮点运算单元的数据路径宽度为256bit(在一次操作中处理的数据的宽度为256位,越宽性能越高),比上一代翻倍了,不仅具有更大的吞吐量,同时也更好地实现了对AVX-256指令(一种高级向量扩展指令集,可以提高浮点运算的速度)的支持。此外,浮点运算单元的数据载入和存储带宽也获得了提升,将使得数据的传输更具效率,并减少了与整数单元出现冲突的概率

3.1.4 模块化设计带来更高灵活度

除了核心架构的进步,Zen2在处理器的设计布局上也进行了变革,以便实现更高灵活度的模块化设计。Chiplet模块化设计是基于AMD Infinity Fabric互联的增强版本,其核心思路是在单个处理器封装内链接多片独立的硅晶片。和上一代Zen架构中每个处理器核心分别自带相关I/O模块截然不同的是,Zen2架构彻底将处理器核心和I/O模块分离,计算核心本身不再提供I/O接口而专注于运算,I/O模块成为连接各个计算核心和外部链接的中枢。

Zen 2的计算核心采用先进的7nm制程工艺生产,有助于缩小晶片面积、提高频率、降低功耗。而I/O部分由于模拟电路更多,即使采用7nm工艺也不会带来面积、功耗等方面的明显改善,所以采用成熟的14nm工艺制造。这种创新的模块化设计的优势明显——在同等功耗下拥有更多的CPU核心,可以获得更高的性能;而与传统的单片设计相比,生产成本又更低。将这种全新的设计方法与台积电最前沿的7nm生产工艺优势相结合,Zen 2架构带来了性能、能耗和计算密度的提升,有助于大幅降低数据中心的运营成本和散热需求。

除了性能和成本上的优势,采用模块化设计的优势还在于可以根据计算需要,灵活地将不同数量的计算核心与I/O模块搭配,以实现不同的规格。Zen 2单个计算模块的规格是8核心、16线程,单颗第二代AMD EPYC(霄龙)处理器的SoC封装最多可以搭配8个计算模块,这样就能够实现最多64核心、128线程的规格。此前单路CPU最多的物理核心记录也只有32个,所以第二代AMD EPYC(霄龙)处理器在物理核心数量上实现了翻倍,而且还支持SMT技术。

(2)革命性的分离式设计

3.2.1 升级的NUMA模式

不仅如此,Zen 2架构还升级了NUMA(Non-Uniform Memory Access)非统一内存访问模式。所谓NUMA,简单来说就是在NUMA模式下CPU 核心和内存控制器将优先处理物理结构上离处理器最近的内存中数据,除非内容过大会溢出到下一个内存模块,这可以有效降低这些数据的访问延迟并提高整体效能。

在Zen架构中,由于Zen架构中每个Die都拥有独立的内存控制器,所以当这两颗分别拥有4个Die的CPU(一共8个Die)进行数据传输时,就一共会存在8个NUMA域,并且最多会存在3个NUMA间距。因此在基于Zen架构的双路系统中,两颗CPU之间进行数据传输时,延迟会达到一个较高的水平,这也会影响到整体效能。

不过在Zen 2架构中,每颗CPU的所有内存控制器都集成在I/O Die中,所以当基于Zen 2架构的两颗CPU组建双路系统时,它们在NUMA模式下只会存在两个NUMA域,并且这两颗CPU之间也仅有两个NUMA间距。因此,更少的NUMA域和间距将会降低双路系统中两颗CPU之间的数据传输延迟,同时也能有效提升其整体效能。

其实Zen 2架构中NUMA模式的改进还不止如此,为了满足不同使用场景的性能需求,Zen 2架构还拥有多种NUMA模式,这些模式名为“NPSx”(英文全称为NUMA Nodes Per Socket)。从AMD给出的资料来看,Zen 2架构中最多可实现NPS4、NPS2、NPS1、NPS0这4中NUMA模式。

其中,每颗基于Zen 2架构,拥有8个Die的第二代AMD EPYC(霄龙)处理器在NPS4下,其8个Die将被分为4组(每两个Die一组),每组中的两个Die将会与通过物理结构最近的内存控制器读取对应这两个通道中内存的数据(即不能读取其他内存通道中的内存数据,所以这两个Die可用的内存容量有限)。由于使用了物理层结构最近的内存控制器,所以在NPS4下,每个Die的内存读写延迟更低,并且内存带宽更高。不过由于这种模式下每组中的两个Die可用内存容量有限,某些对内存容量要求较高的应用并不适合使用NPS4模式。

此外,NPS2就是把第二代AMD EPYC(霄龙)处理器的8个或者4个Die平均分为两组,每组中的Die也是通过物理结构最近的内存控制器读取4个通道中内存的数据。因此相比NPS4,NPS2模式下每组可使用的内存容量更大,但内存延迟也稍高一些。同理,NPS1模式可同时适用于所有单路和双路系统,每颗CPU使用各自的内存控制器去访问相应的8通道内存。而NPS0仅适用于双路系统,两颗CPU共同使用16个内存通道。

(3)更加可靠的安全性

3.3.1 集成AMD安全协处理器和加密引擎

除了全新升级的架构和革命性的分离式设计之外,基于Zen 2架构的第二代AMD EPYC(霄龙)处理器还从硬件层面提供了非常可靠的安全性。第二代AMD EPYC(霄龙)处理器中集成了AMD安全协处理器(ARM Cortex-A5架构的32位控制器),运行于安全的系统/内核,可以确保固件数据等片外非易失性存储的安全,提供安全加密功能,并可实现硬件验证启动,和x86系统的隔离性更好。此外,其内存控制器中还集成了AES-128加密引擎,当提供相应的密钥时,该加密引擎可以自动加密和解密主存储器中的数据。

3.3.2 AMD内存加密技术

不仅如此,第二代AMD EPYC(霄龙)处理器还支持AMD的内存加密技术,它可以让服务器获得全程软、硬加密保护。该技术借助硬件SHA安全算法,支持安全内存加密(英文简称:SEV)和安全加密虚拟化(简称:SME)这两种加密模式。其中,SEV安全加密虚拟化可以保护虚拟机免受无谓伤害,让虚拟机/容器技术被分别保护,连管理员和不安全的虚拟机管理程序也无法越权篡改。此外,每个虚拟机和管理器都有独立的密钥,彼此加密隔离,并与AMD现有的AMD-V虚拟化技术整合。

- 在SEV模式下,监视器和运行在同一机器上的客户端资源、不同客户负载完全隔离,代码和数据将分别标记、独立加密,访问的时候如果加密标记错误,就只能看到加密状态。

- SME安全内存加密是基于硬件支持,可以保护物理内存免受攻击,单个安全密钥,操作系统/虚拟器管理器可以自己选择需要加密的页面,而网络、存储、显卡等硬件设备可以无缝访问加密页面。同时SME内存加密功能对性能的影响很小,仅对被加密页面产生延迟。

(4)大幅提升内存频率和带宽

相比代号为“Naples”的第一代EPYC(霄龙)处理器,第二代AMD EPYC(霄龙)处理器将支持更高频率内存,并且内存带宽也大幅提升。首先在内存频率方面,第二代AMD EPYC(霄龙)处理器最高可支持DDR4 3200频率内存(DDR4 类型的内存,频率为 3200 MHz),而Naples则最高只支持DDR4 2666频率内存。此外在理论最高内存带宽方面,双路第二代AMD EPYC(霄龙)处理器的理论最高内存带宽可达410GB/s,领先双路Naples约21%,同时相比竞争对手的双路第二代至强可扩展处理器,第二代AMD EPYC(霄龙)处理器的理论最高内存带宽更是领先约45%之多。

双路指的是处理器有两个内存通道,可以同时连接两条内存插槽。处理器有两条内存通道可以提高内存带宽,从而提升计算机的性能。

(5)率先支持PCIe 4.0

不仅如此,第二代AMD EPYC(霄龙)处理器还是行业首例支持PCIe 4.0的x86服务器处理器。相比第一代EPYC(霄龙)处理器,其每PCIe通道带宽翻倍,并且显著提升了数据中心加速器的性能。因此,第二代AMD EPYC(霄龙)处理器完全可以满足未来设备的数据传输需求。从AMD给出的资料来看,第二代AMD EPYC(霄龙)处理器配备128条PCIe 4.0通道,并且其理论传输带宽可达512GB/s。

PCIe(Peripheral Component Interconnect Express)是一种常用的计算机总线技术,用于连接计算机的各种外设。PCIe 4.0 是最新的一代 PCIe 总线技术,相比之前的 PCIe 3.0 技术,它的带宽大大提高,能够提供更快的数据传输速度。

四、关于EPYC Zen2的性能

总的来看,率先采用7nm生产工艺、基于Zen 2架构的第二代AMD EPYC(霄龙)处理器的确是AMD推出的一款重磅产品。其先进的7nm生产工艺有助于缩小晶片面积、提高频率、降低功耗;Zen 2架构则大幅度提升了IPC;革命性的模块化设计带来了更高的灵活性。此外,第二代EPYC(霄龙)处理器最高达64核128线程的核心规格也让它拥有远超上一代产品的性能。不仅如此,第二代EPYC(霄龙)处理器的理论最大内存带宽相比上一代产品提升约21%,并且相比竞品有45%的优势,同时内存频率最高可支持DDR4 3200.

参考资料:

7nm为羽、Zen 2为翼,AMD第二代EPYC(霄龙)处理器技术详解 (baidu.com)

Chiplet时代来临 日前,中国工程院院士许居衍在题为《复归于道:封装改道芯片业》的报告中指出,经典的2D缩放已经“耗尽”了现有的技术资源,现... - 雪球 (xueqiu.com)