quartus II使用

1、解决警告信息

FPGA在写Verilog时编译警告,具体警告信息如下:

Warning (18236): Number of processors has not been specified which may cause overloading on shared machines. Set the global assignment NUM_PARALLEL_PROCESSORS in your QSF to an appropriate value for best performance.

(警告(18236):未指定处理器数量,这可能导致共享计算机过载。 将QSF中的全局分配NUM_PARALLEL_PROCESSORS设置为适当的值以获得最佳性能。)

解决方法:

看上边错误警告,未指定处理器数量,这可能导致共享计算机过载。 将QSF中的全局分配NUM_PARALLEL_PROCESSORS设置为适当的值以获得最佳性能。

打开Assignment->Settings->Compilation Process Settings

选择Use all available processors 或者根据自己处理器数量选择最大允许处理器数。保存再编译就OK了。

2、关联Modelsim

(1)指定Modelsim路径

Tools–Options–EDA Tool Options下:

modelsim:D:\modeltech64_10.5\win64

modelsim-altera:D:\intelFPGA\19.1\modelsim_ase\win32aloem

(2)选择EDA工具

Assignment->Settings->EDA tool settings->simulation->Tool name中选择modelsim

(3)生成tb模板

Processing->start->Start Test Bench Template Writer

(4)编写tb文件

File->Open上一步生成的tb模板文件(默认生成的文件名与模块名不相同,后面添加名字时指的是模块名,建议修改为相同,否则写成文件名仿真时会找不到对应的模块)

(5)关联tb文件

Assignment->Settings->EDA tool settings->Simulation->Comile test Bench->Test Benches->new->选择tb文件add(Test bench name是模块名而不是文件名)

(6)开始仿真

Tools->Run simulation tools->RTL

3、查看综合器生成的原理图

(1)输入代码,选择Processing > start > Analysis & Elaboration

(2)Tools > Netlist viewer > RTL viewer

4、修改工程名和顶层模块

(1)修改工程名称流程:

1.删除文件及文件夹,只剩下.VHD、.Verilog等设计文件和.qpf、.qsf两个文件。

2.将.qpf和.qsf两个文件的文件名修改为目标工程名。

3.将.qpf和.qsf两个文件用记事本或其它文本编辑器打开,找到文件中原工程名的字符串,将原工程名字符串改为新的目标工程名字符串。.qpf和.qsf两个文件中各有一处要修改。

4.双击.qpf打开工程,重新编译就好了。

(2)修改顶层实体名称:

1.修改源文件(设计文件)名称:将Top-level entity(顶层实体)名称修改为目标名称。

2.软件中修改工程的顶层实体名称:Assignments -> Settings -> General -> Top-level entity:修改为新的实体名称即可。

3.重新编译。

5、原理图端口名称、模块名称都显示不全的解决方法:

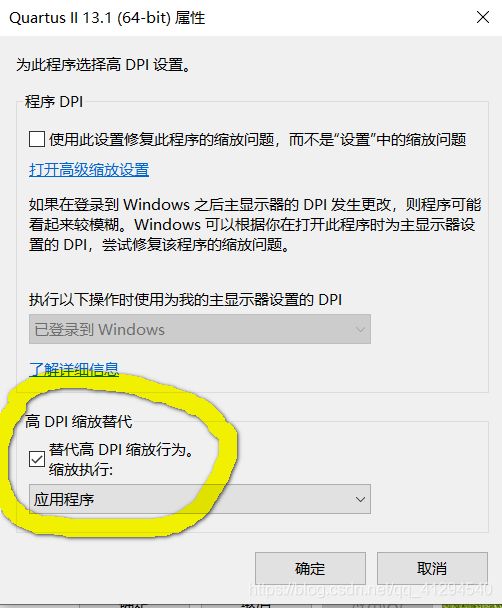

解决方案:右键桌面Quartus图标——>属性——兼容性——高级DPI设置——高级DPI缩放勾选(win10)

6、新建IP核和修改IP核

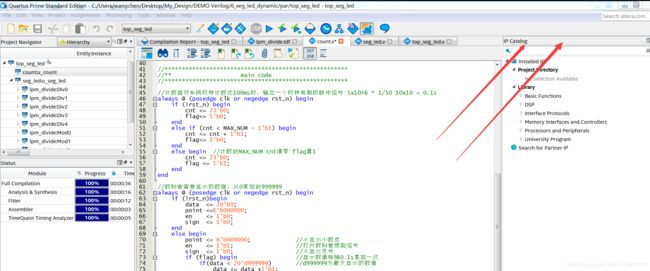

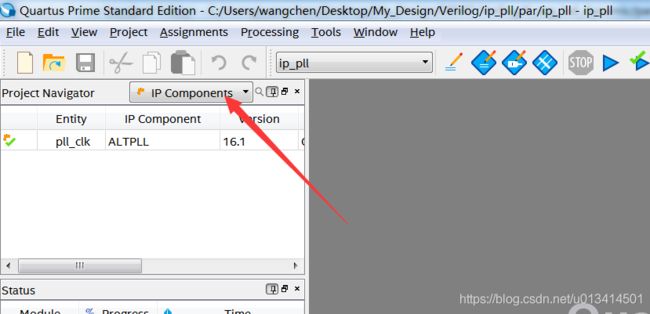

自Quartus16取消了【MegaWizard Plug-In Manager】,后续版本使用IP核的时候,tools->ip catalog然后在软件的右侧就可以新建IP核了。

若要修改IP核,首先在项目导航中选择IP组件

若要修改IP核,首先在项目导航中选择IP组件  然后右键Edit即可

然后右键Edit即可  7、开启代码自动补全功能 Quartus16以后默认没有开启代码自动补全功能的,而Quartus13是有开启的 开启方法:tools-options

7、开启代码自动补全功能 Quartus16以后默认没有开启代码自动补全功能的,而Quartus13是有开启的 开启方法:tools-options  8、固定一个模块的布局布线到另外一个工程中使用 [QuartusII中Design partion功能的使用](https://blog.csdn.net/weixin_30556959/article/details/99366676) Exported Partion File(.qxp)

8、固定一个模块的布局布线到另外一个工程中使用 [QuartusII中Design partion功能的使用](https://blog.csdn.net/weixin_30556959/article/details/99366676) Exported Partion File(.qxp)

从安全角度考虑,我们常希望保证我们设计的私有性。一个有效的方法就是利用QuartusII Exported Partition file(.qxp)创建用于综合或布局布线网表文件(不包括源代码。这种增量编译的特点需要一个完整QuartusII 许可的支持(比如免费的web版本的许可不支持的)。

A、产生qxp文件

1、进行第一次工程的综合;

2、将需要锁定的模块设置: set as design partition、netlist type(source file),然后进行第二次综合;

3、修改netlist type为post-fit,然后进行第三次综合;

B、导出qxp文件

1、Export design partition:导出锁定模块的qxp文件;

C、导入qxp文件

1、用qxp文件代替rtl代码;

2、inport design partition:导入qxp文件

3、综合就可以了

8、时钟管理

**全局时钟的设置:**在Quartus软件中,有全局的设置选项“auto global clock”,可以使得工具在实现的时候自动把一此高扇出的时钟信号走到全局网络上。同样,“auto global register control signals”选项同样可以把一些高扇出的触发器控制信号(如复位和时钟使能信号)走到全局网络上去。setting->analysis&synthesis setting->more setting->existing options setting

如果不希望某个节点(管脚或内部信号)被选择使用全局网络,可以在assignment Editor中单独对该信号设置开关(assignment anme-auto global clock)

**局部走线:**到不同目的节点的延时可能相关较大,即偏斜skew较大,可能会带来时序麻烦。布局布线中有对设计中的保持时间进行优化的选项,可以选择是仅优化IO管脚还是优化所有路径的保持时间。setting->analysis & synthesis settings->more settings->existing options settings->ignor LCELL Buffers,LCELL延时原语,用以认为地增加一些延时电路以满足保持时间的要求。

二、各种错误解决

1、分析综合时出现Warning (12241): 1 hierarchies have connectivity warnings - see the Connectivity Checks report folder

出现“hierarchies”这个词基本上是模块例化的问题。一般例化时,要是哪个连线没引出,没接上,或者是位宽不匹配就会出这个警告。可以通过定位到例化文件,或者是观察RTL视图去寻找,但是工程一大可不是那么好找的啊!

Declared by entity but not connected by instance. If a default value exists, it will be used. Otherwise, the port will be connected to GND.

Declared by entity but not connected by instance. Logic that only feeds a dangling port will be removed.

解释:实例化的时候,有一些端口没用,让没用的端口的位置空着,可以忽略。

2、Warning (15714): Some pins have incomplete I/O assignments. Refer to the I/O Assignment Warnings report for details

Critical Warning (169085): No exact pin location assignment(s) for 44 pins of 44 total pins. For the list of pins please refer to the I/O Assignment Warnings table in the fitter report.

还没有分配管脚的原因,

3、Critical Warning (332148): Timing requirements not met

解决方法:http://www.bubuko.com/infodetail-3306096.html

4、Warning (21074): Design contains 5 input pin(s) that do not drive logic

Warning (15610): No output dependent on input pin “block_num[0]”

Warning (15610): No output dependent on input pin “block_num[1]”

Warning (15610): No output dependent on input pin “block_num[2]”

Warning (15610): No output dependent on input pin “block_num[3]”

Warning (15610): No output dependent on input pin “block_num[4]”

原因:这是在例化时没有例化block_num这个参数

5、Error (10267): XXXX,cannot connect instance ports both by order and by name

原因:模块例化时有接口前没有加点“.”。

6、Warning (276027): Inferred dual-clock RAM node “phy78Q2133:phy78Q2133_u0|fifo:fifo_tx|mem_rtl_0” from synchronous design logic. The read-during-write behavior of a dual-clock RAM is undefined and may not match the behavior of the original design.

usb-blaster驱动重新安装问题