Verilog状态机常见三种写法

1.1理论

Verilog状态机又称同步状态机(FSM,Finite State Machine),一般又叫状态机,在Verilog描述电路中大部分是同步执行(并行)的,但是很多时候需要处理明显具有时间先后的事件,就要用到状态机。每一个状态代表一个小事件,一个完整的任务分为多个事件,完成这个任务需要从该事件跳转到下一时间另一个时间,依次进行下去,整个系统就可以正常运行

1.2状态机分类

1.Moore(摩尔)型:摩尔状态机的输出只与当前状态有关,即当前状态决定输出值,输入值只决定状态的跳变,不影响电路的输出。(此输出为电路的输出值,而非状态机的状态输出)

次态=f(输入,现态),输出=f(现态)。

2.Mealy(米勒)型:米勒型状态机的输出与当前状态和当前输入有关。次态=f(输入,现态),输出=f(现态,输入)。

1.3举例分析

这里从网上找到一个售货机例子,售货机里有价值4元饮料,支持一元与两元,设计一个状态机,当投入金额大于或等于饮料价格时收获机找零并弹出一瓶饮料。硬币与商品一进一出。

状态图:

一段式状态机

module fsm_sale(

input clk ,

input rst_n ,

input [1:0] in ,

output reg [1:0] out ,

output reg out_vld

);

//---------------定义信号----------------------//

reg [3:0] state ;

//---------------定义信号状态变量--------------------//

parameter S0 = 4'b0001 ;

parameter S1 = 4'b0010 ;

parameter S2 = 4'b0100 ;

parameter S3 = 4'b1000 ;

//---------------一段式状态机--------------------//

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

state <= S0;

out <= 0;

out_vld <= 0;

end

else begin

case(state)

S0:begin

if(in==1)begin

state <= S1;out <= 0;out_vld <= 0;

end

else if(in==2)begin

state <= S2;out <= 0;out_vld <= 0;

end

else begin

state <= state;out <= 0;out_vld <= 0;

end

end

S1:begin

if(in==1)begin

state <= S2;out <= 0;out_vld <= 0;

end

else if(in==2)begin

state <= S3;out <= 0;out_vld <= 0;

end

else begin

state <= state;out <= 0;out_vld <= 0;

end

end

S2:begin

if(in==1)begin

state <= S3;out <= 0;out_vld <= 0;

end

else if(in==2)begin

state <= S0;out <= 0;out_vld <=1;

end

else begin

state <= state;out <= 0;out_vld <= 0;

end

end

S3:begin

if(in==1)begin

state <= S0;out <= 0;out_vld <=1;

end

else if(in==2)begin

state <= S0;out <= 1;out_vld <=1;

end

else begin

state <= state;out <= 0;out_vld <= 0;

end

end

default:state <= S0;

endcase

end

end

endmodule

二段式状态机

module fsm_sale

//---------------------<端口声明>---------------------------------------

(

input clk ,

input rst_n ,

input [1:0] in ,

output reg [1:0] out ,

output reg out_vld

);

//---------------------<信号定义>---------------------------------------

reg [3:0] state ;

reg [3:0] n_state ;

//---------------------<状态机参数>-------------------------------------

localparam S0 = 4'b0001 ;

localparam S1 = 4'b0010 ;

localparam S2 = 4'b0100 ;

localparam S3 = 4'b1000 ;

//----------------------------------------------------------------------

//-- 状态机第1段

//----------------------------------------------------------------------

always@(posedge clk or negedge rst_n)begin

if(!rst_n)

state <= S0;

else

state <= n_state;

end

//----------------------------------------------------------------------

//-- 状态机第2段

//----------------------------------------------------------------------

always@(*)begin

case(state)

S0: begin

if(in==1)begin

n_state = S1;

end

else if(in==2)begin

n_state = S2;

end

else begin

n_state = state;

out = 0 ;

out_vld = 0 ;

end

end

S1: begin

if(in==1)begin

n_state = S2;

end

else if(in==2)begin

n_state = S3;

end

else begin

n_state = state;

end

end

S2: begin

if(in==1)begin

n_state = S3;

end

else if(in==2)begin

n_state = S0;

out_vld = 1 ;

end

else begin

n_state = state;

out_vld = 0;

end

end

S3: begin

if(in==1)begin

n_state = S0;

out_vld = 1 ;

end

else if(in==2)begin

n_state = S0;

out = 1 ;

out_vld = 1 ;

end

else begin

n_state = state;

out = 0;

out_vld = 0;

end

end

default:n_state = S0;

endcase

end

endmodule

三段式状态机

module fsm_sale

(

input clk ,

input rst_n ,

input [1:0] in ,

output reg [1:0] out ,

output reg out_vld

);

reg [3:0] state ;

reg [3:0] n_state ;

localparam S0 = 4'b0001 ;

localparam S1 = 4'b0010 ;

localparam S2 = 4'b0100 ;

localparam S3 = 4'b1000 ;

always @(posedge clk or negedge rst_n)begin

if(!rst_n)

state <= S0;

else

state <= n_state;

end

always @(*)begin

case(state)

S0: begin

if(in==1)

n_state = S1;

else if(in==2)

n_state = S2;

else

n_state = state;

end

S1: begin

if(in==1)

n_state = S2;

else if(in==2)

n_state = S3;

else

n_state = state;

end

S2: begin

if(in==1)

n_state = S3;

else if(in==2)

n_state = S0;

else

n_state = state;

end

S3: begin

if(in==1 || in==2) // in != 0也行

n_state = S0;

else

n_state = state;

end

default:n_state = S0;

endcase

end

always @(posedge clk or negedge rst_n)begin

if(!rst_n)

out <= 0;

else if(state ==S3 && in==2)

out <= 1;

else

out <= 0;

end

always @(posedge clk or negedge rst_n)begin

if(rst_n==1'b0)

out_vld <= 0;

else if((state ==S2 && in==2) || (state ==S3 && in!=0))

out_vld <= 1;

else

out_vld <= 0;

end

endmodule

下面分别是三段状态机的仿真图

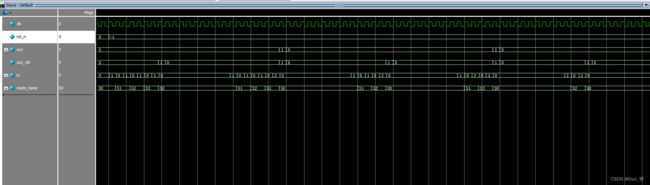

一段式:

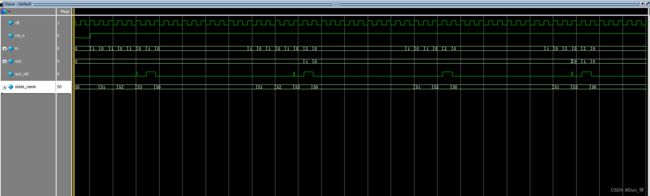

二段式:

三段式:

一段式状态机,只涉及时序电路,没有竞争与冒险现象,上述代码总消耗逻辑(total logic element)为8,比较少,但是状态一旦多了,一段式显得比较臃肿,不利于工程后期维护。

二段式状态机,一段为状态转移,第二段为状态机输出、电路输出。输出波形产生了毛刺现象,而在本文中产生这种现象的原因是,n_state因为组合逻辑原因不断出现临时状态,而这些状态是无效的,输出也因此产生了这些临时状态,即毛刺。

三段式状态机,各大教材中比较推崇的,一段是同步时序逻辑的状态转移(state→n_state);二段是组合逻辑的状态转移的条件,描述状态转移的规律;三段是状态的输出;由于维护方便, 组合逻辑与时序逻辑完全独立。避免了组合逻辑的竞争与冒险,所以我也推荐此种写法。