LoRa PHY帧格式详细介绍

目录

1. LoRa PHY帧格式

2. Preamble部分

2.1 可变Preamble部分

2.2 Sync Word部分

2.3 SFD部分

3. Header部分

3.1 Payload数据包长度

3.2 CR因子选择

3.3 PHY中CRC存在控制

3.4 Header数据校验

4. LoRa空口数据包传输时间

参考文献:

1. LoRa PHY帧格式

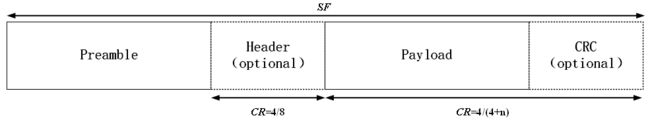

LoRa物理层的数据包格式,如图 1所示,主要包括前导(Preamble),数据包头(Header),有效载荷(Payload)和循环冗余校验(CRC)四部分组成。

图 1 LoRa PHY 帧格式

整个物理层的数据包,根据LoRa调制设定的扩频因子(SF)完成CSS调制。Preamble部分不需要编码而直接采用CSS的调制,而往后的数据都会经过Hamming编码,以提高纠错能力,其中Header部分固定采用CR=4/8的编码格式,Payload和CRC的编码格式由Header中的CR参数确定。

从图 1中可以看出,数据包的Header和CRC是用虚线表示,这两部分的数据,可以通过寄存器设置进行删除,以节约PHY数据包长度,进而节约无线信号传输时间和所需要的能量。

PHY帧格式中的Payload部分,有上层协议进行细化,例如LoRaWAN协议会对此部分内容进行详细说明,本报告不进一步说明。而PHY帧格式中的CRC部分为可选内容,通过Header中的CRC存在标志位进行使能,使能后占16bit,否则没有该数据。

因此LoRa PHY帧格式主要对其Preamble和可选的Header部分内容进行详细说明。

2. Preamble部分

2.1 可变Preamble部分

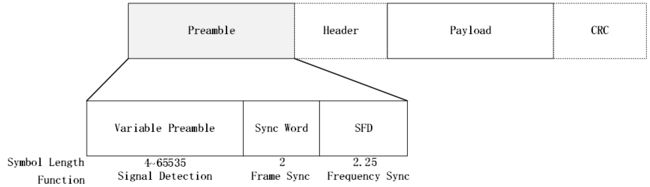

LoRa PHY数据包的前导主要包括三部分组成:可变前导(variable preamble),帧同步字(Sync Word)和帧起始分隔符(SFD:Start Frame Delimiter)三部分组成,如图 2所示。

图 2 LoRa PHY Preamble详细格式

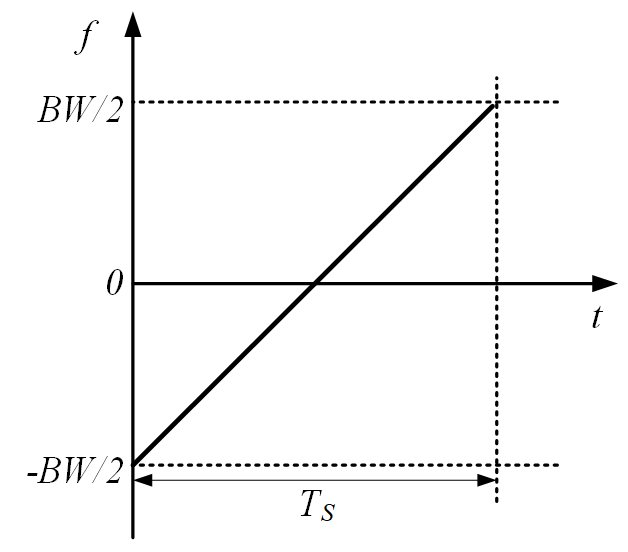

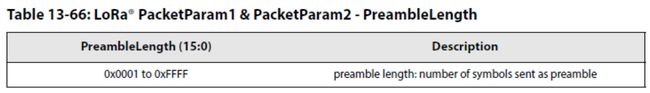

可变前导部分由4至65535个长度的up-chirp符号组成,每个标准的up-chirp符号的频率,如图 4所示,主要提供信号检测、接收机增益设置、频率和采样时间同步等功能,如图 3前三个符号所示。可变前导的数据长度由芯片的寄存器设置。例如芯片SX1278可以通过地址为0x20和0x21的RegPreamble寄存器进行具体长度设置,如图 5所示;SX1268则在LoRa调制器下通过Opcode = 0x8C的SetPacketParams中的PacketParam1 & PacketParam2进行设置,如图 6所示。

图 3 LoRa PHY前导Chirp波形

图 4 基带中标准up-chirp信号

图 5 SX1278系里手册中前导长度设置

图 6 SX1268系里手册中前导长度设置

2.2 Sync Word部分

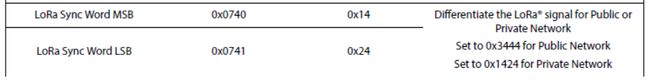

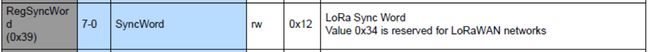

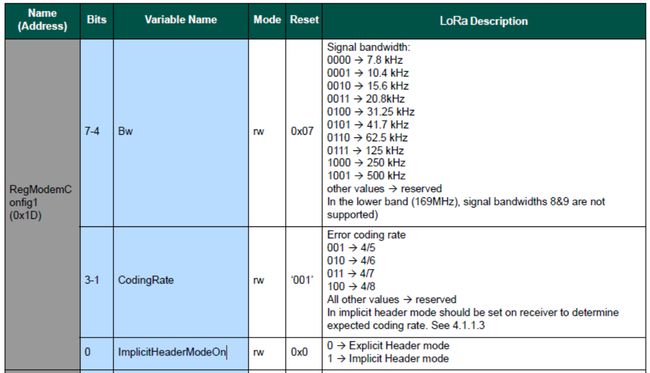

可变长度前导后,是两个符号宽度的帧同步字(Sync word),可以用来快速识别不同的Lora网络。LoRa芯片会直接丢弃帧同步字内容与预设值不一致的数据包。SX1268芯片中通过地址为0x0740 和0x0741的寄存器设置Sync Word,如图 7所示,其中该芯片设定Sync Word=0x3444为公共网络(Public Network)数据包,而Sync Word=0x1424为私有网络(Private Network)数据包。

图 7 SX1268系里芯片中Sync Word设置

而LoRaWAN中规范Sync word=0x34,该数值由SX1278等芯片中地址为0x39的RegSyncWord中的保留设置值,如图 8所示。用户也可以通过修改该寄存器中的内容,修改数据包中的Sync Word。

图 8 SX1278系里芯片中Sync Word设置

对比LoRa两代核心芯片后可以发现,新一代以SX1268代表的芯片,可以通过寄存器直接设置物理层包格式中占两个符号宽度的Sync word值。但是前一代以SX1278为代表的芯片,通过寄存器只能设置一个符号值,因此如何由该一个符号设置值,扩展成两个符号宽度的PHY波形中的Sync Word值,是一个待确定的问题。

由于LoRa底层标准未公开,目前对此部分数据映射,目前没有明确的结论。如果假设SX1278等中Sync Word设置为x:

- [2]中提到对应PHY中的两个符号,分别为

和

和

- [3]中提到对应PHY中的两个符号,分别为

和

和

- [4]中提到将

的高四bit和低四bit分别映射到两个符号,映射关系如图 9所示。

的高四bit和低四bit分别映射到两个符号,映射关系如图 9所示。

图 9 [4]中Figure 2.8提到的Sync Word映射关系

上述针对SX1278系列芯片中的Sync Word映射关系,还有待后续实验验证。

2.3 SFD部分

LoRa规范中PHY数据包中的SFD部分规范比较明确,为占2.25个符号宽度的标准down-chirp信号,如图 3所示,而其中的标准down-chirp信号,如图 10所示。

图 10 基带中标准down-chirp信号

3. Header部分

LoRa PHY数据包分别有两种Header模式:Explicit Header mode和Implicit Header mode,区别在于Explicit模式会在PHY的数据包中包含Header的内容,而Implicit模式的PHY数据包不包含Header的内容。显然Implicit模式将进一步减少无线信号传递的内容,以进一步达到节约传输时间、减少数据包冲突、降低模块运行功耗等目的。此时,通信双方需要预先将Payload数据长度、CR因子,是否存在Payload CRC字段提前进行设置,才能完成通信。

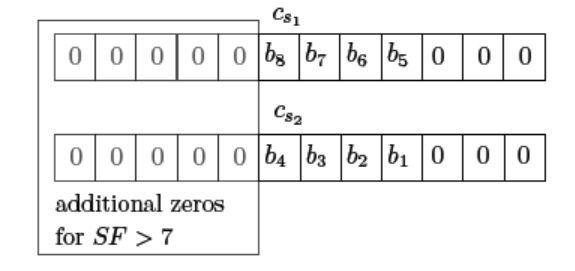

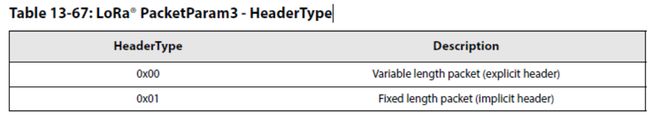

SX1278系列芯片中Header的两种模式由地址为0x1D的RegModemConfig1寄存器bit0进行配置,如图 11所示;SX1268系列芯片中Header的两种模式通过Opcode = 0x8C的SetPacketParams中的PacketParam3进行设置,如图 12所示。

图 11 SX1278系列芯片中Header模式选择

图 12 SX1268系列芯片中Header模式选择

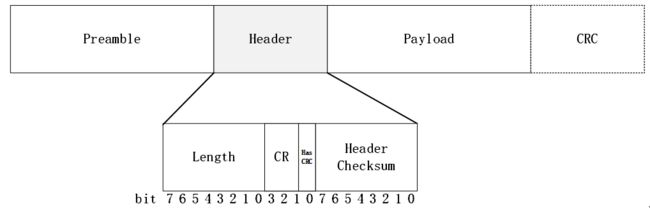

由于LoRa标准并未公开此部分数据结构,因此根据已有的逆向分析显示[5],[6],如图 13所示。Header包括的内容有:payload数据包长度,CR编码方式,payload后是否包含CRC数据,以及header的内容的CRC,共占2.5Byte长度,也就是20个Bit。需要注意的是,Header部分固定采用CR=4/8的编码方式。

图 13 LoRa物理层数据包中Header详细格式

3.1 Payload数据包长度

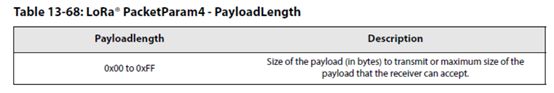

Header中的第一个Byte用于表示整个数据包中,后续Payload内容的长度,占了8个bit,因此一包LoRa数据中,后续payload内容最大为255Byte。

SX1278系列芯片中payload数据包长度由地址为0x22的RegPayloadLength寄存器设置,如图 14所示。SX1268系列芯片中的payload数据包长度由Opcode = 0x8C的SetPacketParams中的PacketParam4进行设置,如图 15所示。

图14 SX1278系列芯片中Payload数据包长度设置

图 15 SX1268系列芯片中Payload数据包长度设置

3.2 CR因子选择

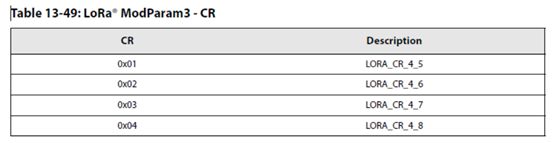

LoRa标准中定义了四种编码方式,分别将4个bit原始数据,经过编码后变化至5,6,7,8四种长度数据。这四种编码方式的选择,相应的定义在了LoRa Header中数据包长度接下来半个Byte(4个bit)中的三个bit,如图 13所示。

SX1278系列芯片中CR因子由地址为0x1D的RegModemConfig1寄存器bit3-bit1进行配置,如图 11所示。SX1268系列芯片中的CR因子由Opcode = 0x8B的SetModulationParams中的ModParam3进行设置,如图 16所示。

图 16 SX1268系列芯片中CR因子设置

3.3 PHY中CRC存在控制

LoRa 物理层数据包的CRC是可以选择传输或者不传输的,如图 1所示。该机制的控制,定义在了LoRa Header中数据包长度接下来半个Byte(4个bit)中的其中一个bit,如图 13中Has CRC部分。如果数据包中存在CRC,那么还需要额外再传输2个Byte内容,即16bit原始数据。

SX1278系列芯片中CRC存在设置由地址为0x1C的RegHopChannel寄存器bit6进行配置,如图 17所示。SX1268系列芯片中的CRC存在设置由Opcode = 0x8C的SetPacketParams中的ModParam5进行设置,如图 18所示。

图 17 SX1278系列芯片中CRC存在设置

图 18 SX1268系列芯片中CRC存在设置

3.4 Header数据校验

LoRa Header数据中的最后一个Byte内容为Header数据字段的CRC校验,即前面所述的数据包长度,CR因子和payload后CRC内容是否存在这12bit内容的CRC校验,占最后一个Byte宽度,如图 13中Header Checksum部分所示。

4. LoRa空口数据包传输时间

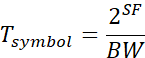

LoRa按照Symbol为单位进行无线传输,而每个symbol的传输时间,有LoRa调制的BW和SF因子有关,详细可以参考:

LoRa PHY CSS调制分析及Matlab实现_weixin_43270276的博客-CSDN博客_css调制

因此需要计算确定Payload内容长度后,对应的symbol符号数量,就可以得到具体的空口数据包传输时间。

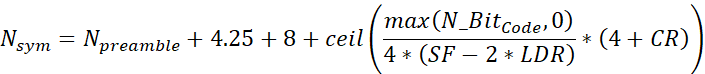

LoRa PHY数据帧中,前导部分的长度比较容易确定,主要是因为该部分数据在定义和描述的时候,直接是以symbol作为单位的。此部分数据占的符号数可以表示为:

![]()

其中![]() 对应2.1 可变preamble部分,由相应寄存器直接设定长度,中间的2个symbol长度为sync word部分内容符号数,最后的2.25个symbol为SFD部分内容符号数。

对应2.1 可变preamble部分,由相应寄存器直接设定长度,中间的2个symbol长度为sync word部分内容符号数,最后的2.25个symbol为SFD部分内容符号数。

LoRa PHY传输时,除了前导部分对应的符号![]() 之外,后续至少还要传送8个symbol,同时该规范了后续必须传输的8个Symbol必须采用CR=4,即实现4/8编码,且该8个符号采用SF-2进行CSS符号映射,即Low Data Rate Optimization的方式进行CSS调制。因此,我们可以得到,该8个符号最多能够传输的原始bit数为:

之外,后续至少还要传送8个symbol,同时该规范了后续必须传输的8个Symbol必须采用CR=4,即实现4/8编码,且该8个符号采用SF-2进行CSS符号映射,即Low Data Rate Optimization的方式进行CSS调制。因此,我们可以得到,该8个符号最多能够传输的原始bit数为:

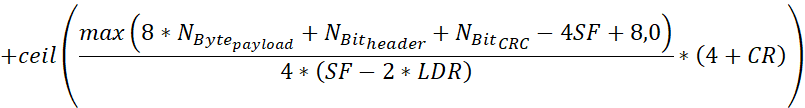

除了前导是以symbol为单位,LoRa PHY帧结构中其他内容,都是以Byte为单位。经过Header部分的分析,我们可以知道该部分实际占用的数据长度取决于是否使用Header部分,在显性模式(explicit)下,该数据长度为2.5Byte,即20个bit,而在隐性模式(implicit)下,该数据长度为0。因此可以表示为:

如果LoRa PHY帧结构是否包含CRC,取决于Header中的Has CRC标志位,如果存在,那么此部分占用2个Byte,即16个bit,否则为0。因此可以表示为:

而数据包中Payload部分数据长度,由Header中的Length决定。此部分数据占用bit数可以表示为:

![]()

其中:![]() 由芯片寄存器设置,体现于Header的Length部分。

由芯片寄存器设置,体现于Header的Length部分。

因此,整个芯片传输实际承载的bit数可以表示为:

![]()

上述数据,部分是需要通过前导后的8个强制的symbol传输,因此实际需要再次编码,CSS调制的bit数为:

![]()

![]()

显然,在某些极端情况下,![]() 直接计算会小于0,例如

直接计算会小于0,例如![]() ,

, ![]() ,

, ![]() ,

, ![]() ,此时直接计算,

,此时直接计算,![]() 。此种情况代表8个强制的Symbol,编码传输完8个bit的payload数据后,还有剩余的bit,此时LoRa芯片会将多余Symbol补充冗余数据后直接传输。因此,实际需要后续编码传输的原始bit数据为:

。此种情况代表8个强制的Symbol,编码传输完8个bit的payload数据后,还有剩余的bit,此时LoRa芯片会将多余Symbol补充冗余数据后直接传输。因此,实际需要后续编码传输的原始bit数据为:

![]()

也就是当![]() 长度超过0时,才需要用到8个强制symbol以外的符号进行传输。

长度超过0时,才需要用到8个强制symbol以外的符号进行传输。

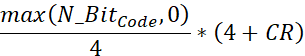

此部分数据的编码情况,由系统的CR因子决定,也就是将剩余需要额外编码的bit数,每4个bit编码至4+CR个bit。因此,经过编码之后的bit数变为:

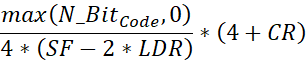

经过编码后的bit,再经过处理后,最终需要根据设定的SF因子,组成symbol。如果没有打开Low Data Rate Optimization功能,那么每SF个bit组成一个Symbol进行CSS调制;如果打开Low Data Rate Optimization功能,那么每SF-2个bit组成一个Symbol进行CSS调制。

因此,额外需要占用的symbol为:

其中:

显然,上式不能被![]() 完全整除,代表额外需要编码的bit数不可能正好是

完全整除,代表额外需要编码的bit数不可能正好是![]() 的整数倍。此时,LoRa芯片将补充为整数个symbol,即对刚刚的结果进行向上取整,因此,最终额外需要占用的符号数可以表示为:

的整数倍。此时,LoRa芯片将补充为整数个symbol,即对刚刚的结果进行向上取整,因此,最终额外需要占用的符号数可以表示为:

最终,LoRa数据包空口所占用的符号数为:

![]()

其中的固定数8代表前导后固定需要发送的8个symbol。将其他参数代入后可以得到:

![]()

上述结果与手册中介绍的一致。最终,空口传输所需要的时间可以表示为:

![]()

其中

参考文献:

[1]LoRaWAN 1.0.3, [Online] “https://lora-alliance.org/wp-content/uploads/2020/11/lorawan_regional_parameters_v1.0.3reva_0.pdf”

[2] O. Seller and N. Sornin, “Low power long range transmitter,”, Eur. Patent 2 763 321, Feb. 5, 2013

[3] C. Bernier, F. Dehmas and N. Deparis, "Low Complexity LoRa Frame Synchronization for Ultra-Low Power Software-Defined Radios," in IEEE Transactions on Communications, vol. 68, no. 5, pp. 3140-3152, May 2020

[4] Eigner, H., Interference analysis of LoRaWAN systems, 2021. [Online]. Available: https://repositum.tuwien.at/handle/20.500.12708/16683

[5] P. Robyns, P. Quax, W. Lamotte, and W. Thenaers, “A multi-channel software decoder for the LoRa modulation scheme,” in Int. Conf. on Internet of Things, Big Data and Security (IoTBDS), Mar. 2018.

[6] J. Tapparel, “Complete reverse engineering of LoRa PHY,”https://tcl.epfl.ch/resources-and-sw/lora-phy/, Tech. Rep., 2019.