UC3842电源管理芯片详细解读

UC3842是AC-DC反激式变压器中常用的电源管理芯片,其具有较低的启动电流(<1mA),并且可以在高达500KHz频率下工作,在输出端输出可脉宽调制的PWM波来驱动NMOSFET,并且在MOS管关断时具有较低的功耗。

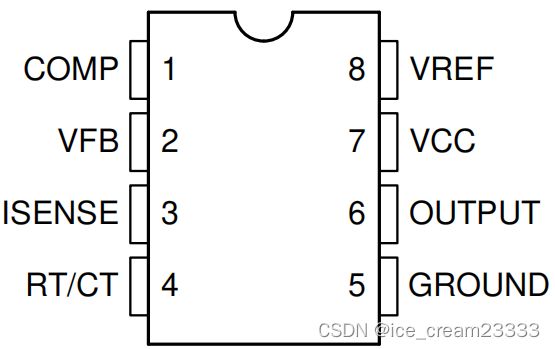

一、管脚描述(以8脚封装为例)

图1. UC3842管脚分布图

1.COMP(Compensation):误差放大器补偿引脚。内接误差放大器E/A的输出端,可通过连接外部补偿组件(如阻容网络)来调整误差放大器的输出。误差放大器内部限流,可以通过将COMP引脚接GND来设置零占空比。

2.VFB:电压反馈引脚。误差放大器的反相输入端,通常接开关电源电路的反馈电路。

3.ISENSE:初级绕组电流感应引脚。PWM比较器的同相输入端,与误差放大器的输出信号经过二极管和电阻分压后的信号做对比,控制PWM锁存输出低电平使MOS管关闭。通过在此引脚串联一个电流感应电阻到地,可以将电流转换为电压,使芯片工作在电压模式控制状态下。

4.RT/CT:振荡器固定频率设置引脚。从此引脚连接定时电容CCT到GND引脚,从此引脚连接定时电阻RRT到VREF引脚,设置电容CCT的充放电时间,二者决定了振荡器产生的时钟信号频率。

5.GROUND/PWRGND(14脚封装有此脚):模拟地/电源地。

6.OUTPUT:MOSFET栅极驱动端。

7.VCC/VC(14脚封装有此脚):电源引脚。OUTPUT栅极驱动电路的偏置电压输入端,同时作为整个芯片的供电输入端。

8.VREF:5V参考电压引脚。VREF用于通过定时电阻RRT向振荡器定时电容器CCT提供充电电流。

二、功能框图及具体工作原理

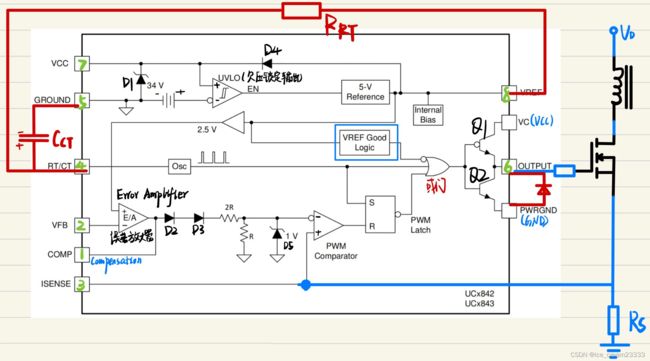

图2.UC3842功能框图

注:在8引脚封装中,VCC和VC引脚接在一起引出VCC,GND和PWRGND接在一起引出GND。

1.电源部分

(1)前级保护

如图2所示,VCC引脚串联一个34V钳位稳压二极管D1接地,起到保护作用。UC3842正常工作时VCC允许最大电压为30V,当供电电源超过34V时,D1导通,将VCC钳位在34V(疑问:VCC允许最大电压为30V,这里为什么不直接用30V稳压二极管钳位呢?)在电流比较小时,D1还可以承受,但当电流较大时,D1可能会因为电流较大而短路导致VCC接地,因此在电路设计中必须通过一个限流电阻限制流经VCC的电流,建议设计中IVCC<25mA。

并且设计过程中IVCC和IOUTPUT要满足以下要求:

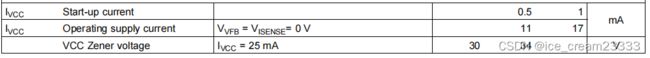

静态工作电流为0.5mA,总的供应电流supply current=IVCC=静态工作电流+平均输出电流IOUTPUT

![]()

Qg为MOS管栅电压电荷,fsw为开关管工作频率。即在设计过程中,启动电流最小为0.5mA,最大为1mA,当电路达到稳定状态后,正常工作电流平均为11mA,最大为17mA,极限值为25mA,且IOUTPUT极限值为200mA。

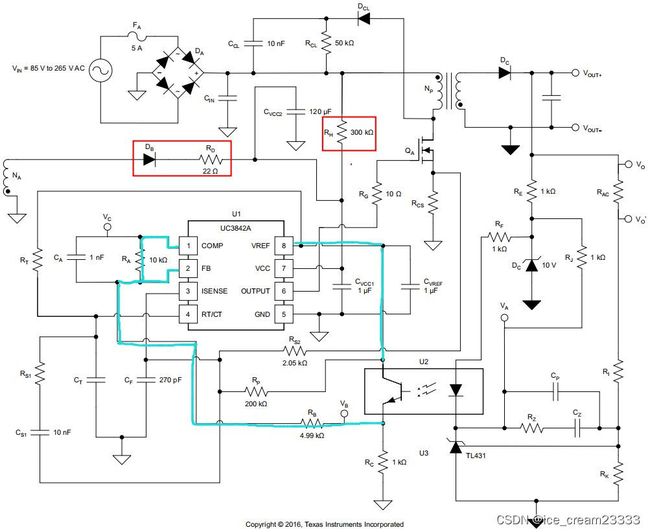

注:在实际中,如图3所示,在VCC引脚接300KΩ的启动电阻RH,最大启动电流约为1.25mA(这里超过1mA会不会有问题?刚开始有些大,随着VCC增大,这个电流会减小),同时在VCC引脚和变压器辅助绕组之间串联二极管DB和电阻RD进行限流分压,防止在MOS管关断瞬间过大的尖峰电流加在VCC引脚导致UC3842损坏。

启动电阻RH的计算方法如下:

VIN(min)是用于供电VCC的最小电压(图中为85√2=120V),VVCC(max)是最大VCC钳位电压34V,IVCC为不考虑栅驱动电流的IC供应电流,Qg为MOSFET栅电荷,fSW为开关频率。

图3.UC3842A反激式开关电源电路

(2)UVLO(欠压锁定输出)

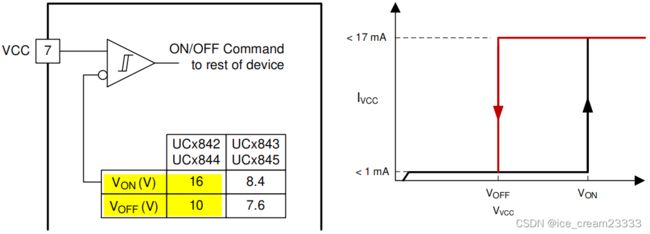

电源初始供电后,芯片在1mA以下启动电流下工作在欠压锁定输出UVLO状态下。如图2所示,UVLO部分比较器反相输入端接电源(应该不是固定电压),同相输入端接VCC,通过比较VCC供电电压与内部开启/关断电压来控制供电电流,具体工作方式图4。

图4.UVLO工作方式

(a).当芯片供电电流增大到使供电电压VCC高于芯片开启电压VON(=16V)时,供电电流增大到17mA(最大值),典型值为11mA,此时芯片达到正常工作电流,UVLO运算器输出为高,产生5V参考信号,引出VREF引脚;

(b).当芯片供电电流减小到使芯片供电电压VCC低于关断电压VOFF(=10V)时,芯片总供电电流减小到1mA(<1mA),此时芯片工作在欠压锁定输出状态下(同样,在开启过程中,若供电电压VCC

注:在如图3所示的AC-DC反激式开关电源电路中,整流滤波后的直流电压经过300KΩ启动电阻后达到UC3842启动电流给VCC引脚旁路电容CVCC1充电,当充电电压达到芯片开启电压VON时,芯片供电电流增大到17mA,芯片开始正常工作,OUTPUT脚输出PWM波控制MOS管导通与关断。MOS管导通期间,由充电电容CVCC1为芯片供电,电容CVCC1处于放电状态;MOS管关断期间,由变压器辅助绕组为芯片供电,CVCC1处于充电状态。在工作过程中,如启动电流不足或电压无法达到VON,则芯片无法正常工作。

疑问1:启动电流会随着VCC电压的增大/减小而发生变化,但整个电路工作过程,启动电流是一直保持达到要求启动电流值,这样才能保证芯片可以在电压VCC达到开启阈值VCC时启动,是这样吗?

疑问2:当MOS管关断时,变压器初级绕组上产生反向感应电动势,辅助绕组上电压为上负下正,二极管导通,给VCC供电,有没有可能在还没来得及产生反向感应电动势的时候,芯片供电电压VCC降到了VOFF10V以下,则芯片停止工作,等辅助绕组上电压逐渐升高到VON后芯片重新开始工作,如此往复,芯片就出现了“打嗝”现象,会这样吗?

2.参考电压部分

当芯片工作电压达到开启电压后,VCC UVLO输出一个精度较高、较稳定的5V参考电压。

(1)作为高速开关逻辑的逻辑电源VREF Good Logic,此处其实也是一个和VCC UVLO类似的迟滞电路VREF UVLO,反相端接3.6V电压源,同相端接5V参考电压,当参考电压低于3.6V时,VREF UVLO输出低,图2中的或门输出高,UC3842 OUTPUT引脚输出低,MOS管关断。当参考电压达到5V左右,VREF UVLO输出高,说明芯片处于正常工作状态,或门输出状态由振荡器和PWM Latch决定。

注:参考电压端什么时候会被拉低呢?在图3所示电路中若充电电容CT短路接地,则VREF会被拉低,当可能拉低到<3.6V时,VREF UVLO输出低,图2中的或门输出高,UC3842 OUTPUT引脚输出低,MOS管关断,就起到了一定的保护作用。

(2)VREF分压后输出稳定的2.5V参考电压作为误差放大器E/A的同相输入端,VFB作为误差放大器的反向输入端,同时补偿引脚COMP接在误差放大器的输出端,可以通过设置一定的RC网络来进行输出电压的反馈监测,从而调整PWM波的占空比。

(3)为内部其他电路偏置提供参考。

(4)对VREF和RT/CT之间的充电电阻和充电电容提供充电电流。

3.误差放大器

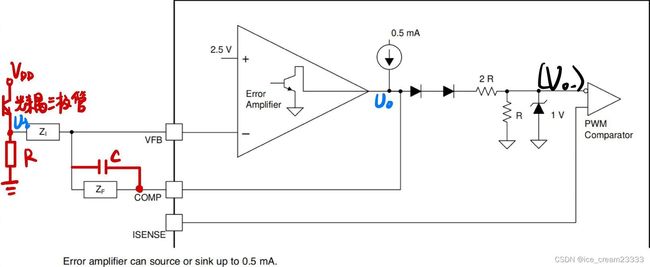

图5.误差放大器(图中红色部分为第二种反馈方式,也是图3电路中的反馈方式)

如图5所示,误差放大器的输出端是一个与0.5mA电流源并联的开集三极管(即集电极开路输出,但此图中不确定开集三极管前面电路是什么,只能从输出分析原理)。若不接电流源,当三极管输入为高,三极管导通,输出端集电极接地;当三极管输入为低,三极管截止,输出端相当于悬空,为高阻态。而接入电流源可以让三极管集电极可以输出一个高电平(而不是高阻态)。

误差放大器的工作方式如下:当VFB电压大于2.5V,三极管基极输入为高,集电极输出为低,此时COMP端与误差放大器输出叠加向后级传输,但产生的效果应该是让占空比减小(提前关断MOS管),因此COMP端的输入应该设计适配的阻抗网络让二者达到此结果;同样当VFB电压小于2.5V,三极管基极输入为低,集电极输出为高,COMP端输入与误差放大器输出叠加向后级传输,但产生的效果应该是让占空比增大(延迟关断MOS管)。

根据VFB和COMP两引脚,电压反馈方式有两种:

(1)如图6所示为第一种反馈方式,VFB直接接地,则误差放大器输出为高,COMP接光耦三极管集电极,发射极接地。当输出电压增大,则TL431和光耦构成的反馈电路中光耦一次侧二极管上电流增大,二次侧三极管集电极电流IC增大,则电阻R上分压增大(VD=VR+Vcomp),COMP被拉低;反之当输出电压减小,则TL431和光耦构成的反馈电路中光耦一次侧二极管上电流减小,二次侧三极管集电极电流IC减小,则电阻R上分压减小,COMP被拉高,COMP的状态影响PWM信号的占空比,以此来调控开关管的开关时间。

图6.第一种反馈方式

(2)如图5及图3中蓝色部分均为第二种反馈方式。假设误差放大器为普通放大器,那么根据“虚短”、“虚断”有如下:

(a)虚短:VFB=VREF=2.5V;

(b)虚断:I(+)=I(-)=0,即

其中Ui由光耦三极管电流及电阻R决定,因此可以通过配置阻抗网络、设置光耦工作电流区域来设置COMP端电压,从而调控PWM波占空比(具体COMP端需要怎么设置呢?)、

4.电流感应部分

误差放大器输出端接两个二极管降压之后分压并通过稳压二极管钳位在1V,接在PWM比较器的反相输入端,PWM比较器的同相输入端接电流感应引脚ISENSE的同相输入端,当电流感应引脚ISENSE电压>1V时,PWM比较器输出为高,反之,输出为低。

如图2所示,通常在电流感应引脚INSENSE串联一个电阻RS到地,电阻另一端接MOS管源极。当MOS管关断时,INSENSE引脚无电流,为高阻态,则PWM比较器输出为低,PWM波占空比由振荡器决定,当MOS管导通时,INSENSE引脚电流逐渐增大,通过RS电阻INSENSE引脚电压逐渐拉高,当Vsense>1V时,PWM比较器输出为高,则RS触发器Reset引脚触发复位,RS触发器输出为高,则或门输出为高,UC3842输出端OUTPUT为低,MOS管关断,RS上电阻电流瞬间减小,INSENSE电压也快速地减小(<1V),PWM比较器输出为低,PWM波占空比由振荡器决定,如此往复。

电阻RS的大小由MOS管导通电流决定,RS=1/IDS。

5.振荡器部分

如图2所示,振荡器接引脚RT/CT,定时电阻串联在VREF和RT/CT之间,定时电容通过RT/CT接地。定时电阻RRT、定时电容CCT提供具有一定放电时间和充电时间的锯齿波,通过RRT和CCT可以设置振荡器产生固定频率的时钟信号,计算公式如下:

(1)振荡器可以工作在高达500KHz频率下,其波形峰值为1.7V。要求芯片UC3842死区时间不超过振荡器时钟周期的15%,而死区时间由电容CCT的放电电流决定(详见datasheet),并且死区时间与CCT容值成正比,因此要选择具有较小容值的电容。

在死区时间/放电时间内,输出端OUTPUT一直为低电平,MOS管为关断状态。最大占空比由下式限制:

可理解为在死区时间内开关管是关断的,其他时间内开关管是导通的,振荡频率足够大,死区时间可以忽略不计,则时钟信号最大占空比可以达到100%。

(2)开关管关断时,会产生噪声尖峰信号耦合到振荡器RT/CT端。在较大占空比下,足够大的尖峰信号会影响振荡器的正常工作,则需选择具有较大容值的CCT,建议不小于1000pF。需综合考虑。CCT和RRT的大小对振荡器的波形影响如图7:

图7.RT/CT选型波形图

左图为大电阻小电容,充电慢放电快,则PWM Latch "Set"端占空比小,芯片OUTPUT输出PWM波占空比可调范围大,右图为小电阻大电容,充电快放电慢,则PWM Latch "Set"端占空比大,芯片OUTPUT输出PWM波占空比可调范围小。

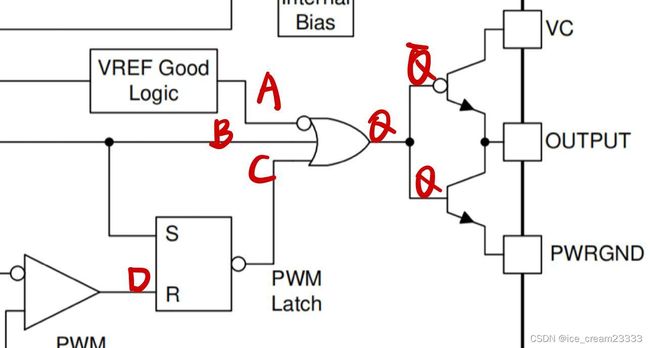

6.输出端OUTPUT信号

输出端通过两个三极管连接进行推挽输出设置,当Q为“1”时,上方三极管基极电压为低,下方三极管基极电压为高,则上方三极管截止,下方三极管导通,OUTPUT接地,输出低,MOS管关断;当Q为“0”时,上方三极管基极电压为高,下方三极管基极电压为低,则上方三极管导通,下方三极管截止,OUTPUT接VCC,输出高,MOS管导通。

根据RS触发器,VREF Good Logic、或门各信号来分析OUTPUT输出,如图所示:

说明:当INSENSE引脚>PWM波比较器反相端电压时(最大为1V),PWM比较器输出信号D为“1”,反之为“0”;

振荡器输出信号B为固定频率的时钟信号,占空比由CCT、RCT大小决定;

信号C为RS触发器输出信号;

信号A为参考电压逻辑输出信号,当参考电压正常输出为5V时,A为“1”,低于3.6V时A为“0”。

结合图7 RT/CT选型波形图,真值表如下图所示:

因此在一个时钟周期内,只有从Set信号下降沿变为低电平开始,到Reset信号上升沿刚开始变为高电平结束,即图7中的t1on/t2on阶段。

整体解释OUTPUT引脚输出:电容放电时间决定了振荡器的频率,即Latch的"Set"引脚的信号状态。初始上电时,启动电阻给电容CT充电,达到芯片阈值电压16V时,电容放电,芯片开始稳定工作。刚开始的一段时间,MOS管关断,UC3842 Sense引脚上电流感应电压为0,低于PWM比较器反相输入端的电压,则PWM Latch的"Reset"引脚为低电平,当电容CT放电结束瞬间,PWM Latch "Set"引脚下降沿变为低电平,则MOS管导通,在此期间,Sense引脚上电流感应电阻感应电压逐渐上升,上升到等于PWM比较器反相输入端电压时,PWM比较器输出为高电平,即PWM Latch的"Reset"引脚为高电平,则MOS管突然关断,Sense引脚上电流感应电阻感应电压瞬间降低为0,小于PWM比较器反相输入端的电压,PWM比较器输出为低电平,则"Reset"引脚立马变为低电平。此阶段"Set"引脚和"Reset"引脚均为低电平,保持上一阶段的输出,则MOS管一直处于关断状态,直到下一次电容CT放电结束,"Set"引脚下降沿出现MOS管再次开启,如此循环往复,控制MOS管开启、关断时间。

从上述过程中可知,可以通过控制输出补偿端的电压大小来调整MOS管占空比大小。拉高COMP引脚电压,占空比增大;拉低COMP引脚电压,占空比减小。COMP引脚电压不得超过6V (Datasheet上有个高水平输出,有个低水平输出,不太理解什么意思)。

思考:在RS触发器这里,B、D可以同时为“0”或同时为“1”吗?

总结

从各个引脚以及芯片结构框图并结合实际原理图详细解释了UC3842各个引脚的功能及内部工作原理,从而对UC3842有了更深刻的理解,便于设计开关电源电路。

期望各位的指导与建议!!