LPDDR4硬件详解

-

目录

2 LPDDR4颗粒介绍

2.1.LPDDR4架构

3.LPDDR4电气特性

3.1 上电时序

3.2 上电初始化时序

3.3 复位时序

3.4 下电时序

3.5 经典的核心时序

3.6 DMI

3.7 ODT

3.8 ZQ校准

3.8 Vref

4.测量指标

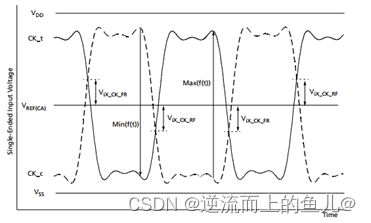

4.1 CLK

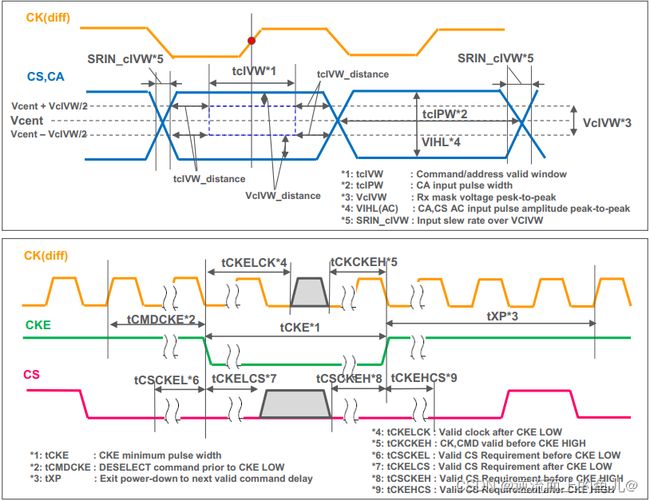

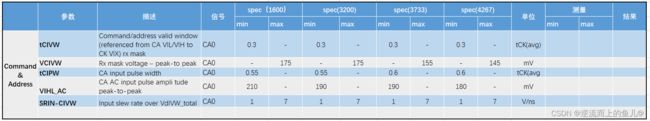

4.2 Cammand & address

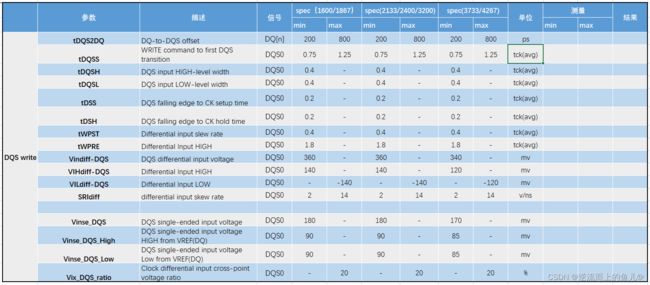

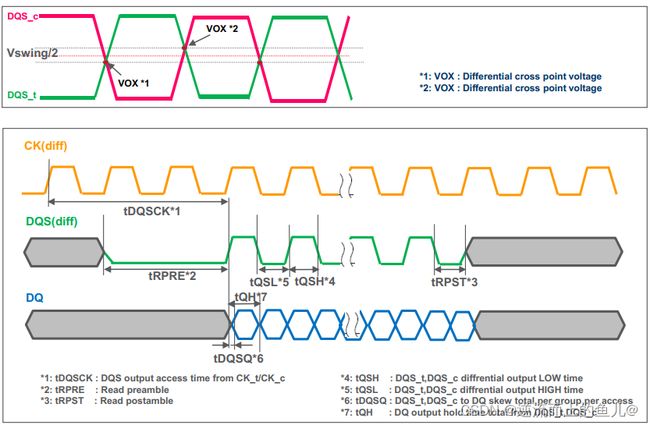

4.3 DQS write

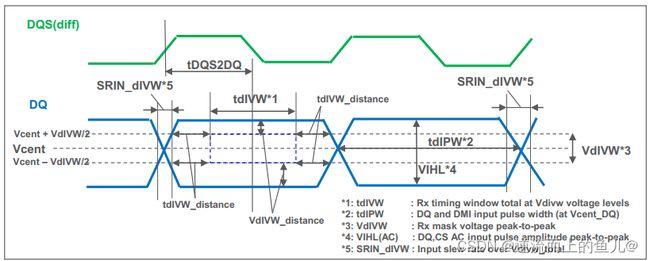

4.4 DQ write

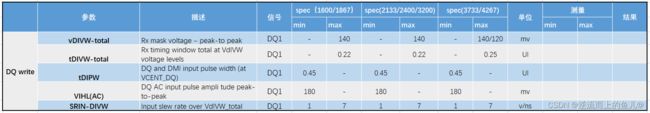

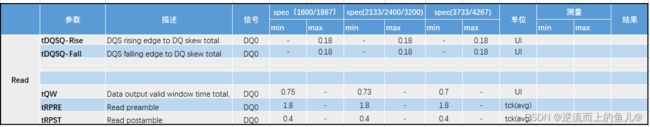

4.5 DQ read

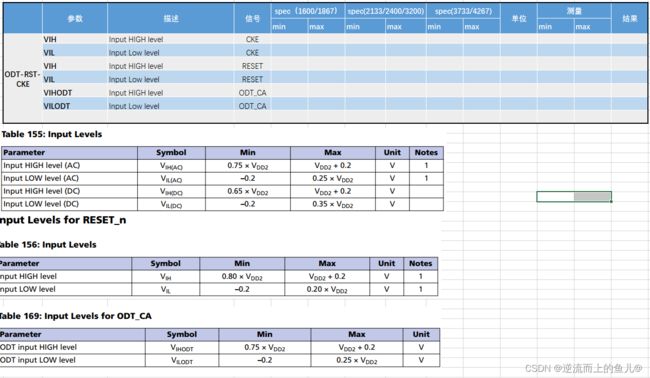

4.6 ODT-RESET-CKE

2.1测试前准备

2.1.1示波器的选择及设置

2.1.2测试注意事项

2.2信号测试

2.2.1读写分离方法

2.2.2信号测试的内容

DDR基础知识

1.1什么是DDR?

DDR SDRAM全称为Double Data Rate SDRAM,中文名为“双倍数据率SDRAM”。

DDR是在原有的SDRAM的基础上改进而来,严格的说DDR应该叫DDR SDRAM,人们习惯称为DDR。

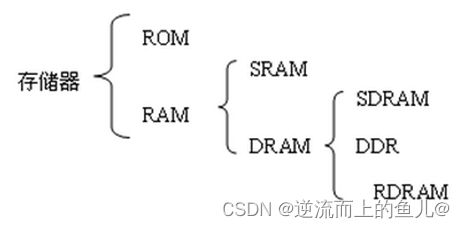

ROM和RAM都是半导体存储器

ROM-Read-Only Memory,是一种只能读出事先所存数据的固态半导体存储器,其特性是一旦储存资料就无法再将之改变或删除

RAM-Random Access Memory,随机是指数据不是线性依次存储,而是自由指定地址进行数据读写,通俗来说就是可以以任何顺序访问,而不管前一次访问的是哪一个位置。

RAM又分两大类,一种称为静态RAM(Static RAM/SRAM),是一种具有静止存取功能的内存,不需要刷新电路即能保存它内部存储的数据,也就是说加电情况下,不需要刷新,数据不会丢失。SRAM速度非常快,是早期读写最快的存储设备了,但是SRAM也有它的缺点,即它的集成度较低,相同容量的内存需要很大的体积,且功耗较大;同时它也非常昂贵,所以只在要求很苛刻的地方使用,譬如CPU的一级缓存,二级缓存。

另一种称为动态RAM(Dynamic RAM/DRAM),DRAM 只能将数据保持很短的时间,为了保持数据,DRAM使用电容存储,所以必须隔一段时间刷新(refresh)一次,如果存储单元没有被刷新,存储的信息就会丢失(关机就会丢失数据);它的速度也比SRAM慢,不过它还是比任何的ROM都要快,但从价格上来说DRAM相比SRAM要便宜很多,计算机内存就是DRAM的。

SDRAM又是在DRAM的基础上发展而来,同时也是属于DRAM中的一种。SDRAM即Synchronous DRAM,同步动态随机存储器,同步是指 Memory工作需要同步时钟,内部命令的发送与数据的传输都以它为基准;

DDR SDRAM又是在SDRAM的基础上发展而来,这种改进型的DRAM和SDRAM是基本一样的,不同之处在于它可以在一个时钟读写两次数据,这样就使得数据传输速度加倍了。

-

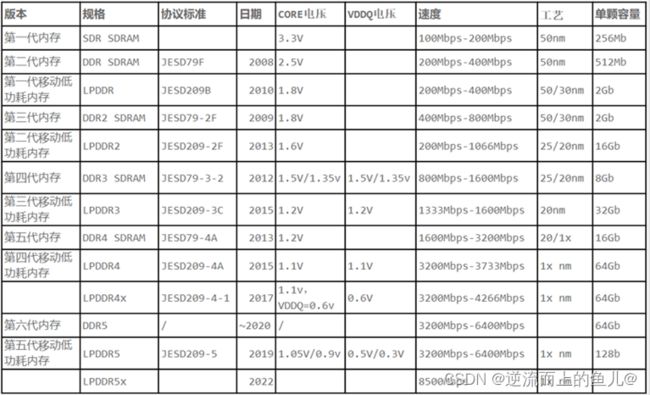

- DDR演进路线

1.3历代DDR提升速率的方法

从SDR SDRAM到DDR3

1.核心频率基本不变,133MHz

2.采用时钟双边沿采样,得到双倍速率

3.通过提升预取位数,提升时钟频率(从1n到8n)

DDR4和DDR3一样,只有8n的prefetch,但为了提升前端Front End的总线速度,不得不在核心频率上动起了手脚,核心频率从200-400MHz,总线速度提升。

比如,我们产品上使用的LPDDR4,在JDDEC上可以看到,使用16为prefetch,对应有533MHz~4266MHz。我们使用的4266Mbps,其存储阵列核心频率就是4266/16=255.625MHz,DDR接口时钟频率为2133MHz

2 LPDDR4颗粒介绍

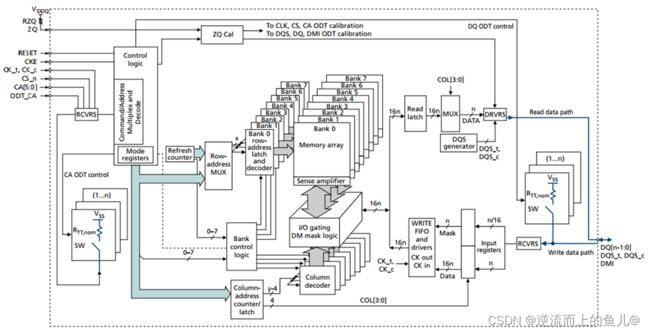

2.1.LPDDR4架构

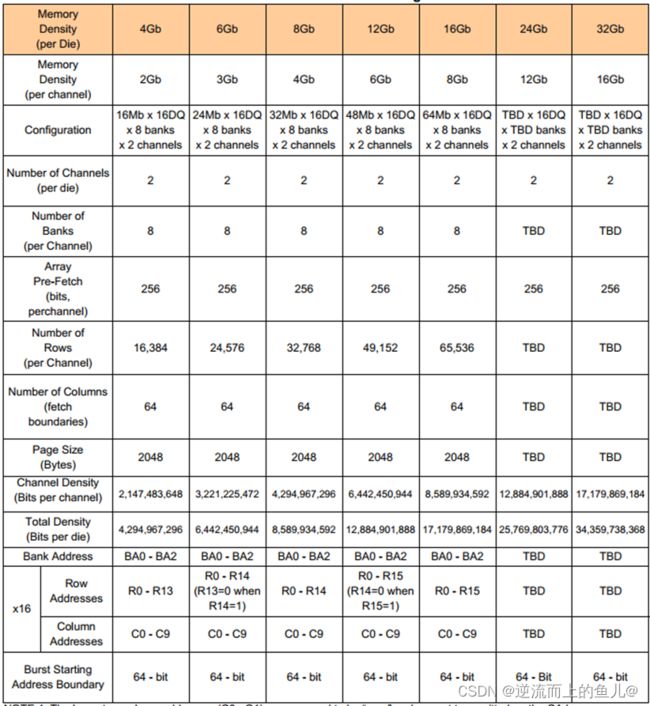

LPDDR4采用了全新的双通道设计,每个裸片包含两个Channnel,每个Channel包含8个Bank,16Bit位宽,16n预读取(DDR4的2倍),每个Die的最高存储容量可以达到32Gb。

对于标准的容量的LPDDR4器件,每个Channel的列是固定的(Page页是固定的),容量越大,行越多。如下图所示:

具体的结构图如下:

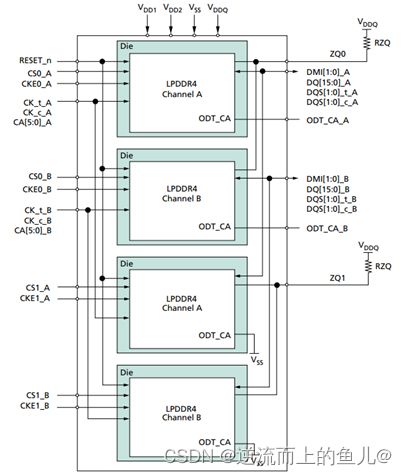

那么,如何组成所谓的single-channel/single-rank, dual-channel/single-rank, dual-channel/dual-rank等形形色色的类型颗粒呢?

Rank和channel的概念相信大家都比较清楚,在这里简单的解释一下。所谓channel,可以理解为一个独立的DDR控制器通道,可以独立的控制接在上面的ddr颗粒工作。Rangk,可以理解为通过片选信号,让多组DDR颗粒通过CS片选来分时复用同一个channel。

所以,扩展channle可以扩展DDR的总带宽,阔展Rank可以在相同的channle下扩展内存容量。假设,一颗有两channel,32位宽的cpu,想要获得高带宽,就需要使用dual-channel的颗粒,或者2个16位宽颗粒组成dual-channel,或者4颗8位宽颗粒组成dual-channel;想要在channel满配的情况下,继续宽展容量,就需要去堆rank了。

那么,如何连接扩展呢?

如下图的例子,是4个16位宽die组成dual-rank、dual-channel的架构。工作时,上面两个die或者下面两个die,组成一个rank同时进入读写操作,把16位宽的die扩展成32位宽的一个rank。上下两个rank通过cs片选分时复用,组成一个双rank的组合。

2.2 LPDDR4颗粒封装

在JEDEC上定义了6中封装:

1.272 ball的4通道FBGA封装

2.200 ball的兼容单双通道FBGA封装

3.203 ball的双通道FBGA封装

4.432 ball的HDI封装

5.324 ball的非HDI封装

6.275 ball的MCP封装

2.3 DDR4颗粒的管脚定义

这个比较简单,附一张jedec的介绍图片

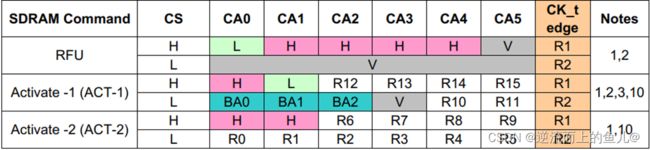

需要说明的是,在上面2.1架构上面介绍行列地址的时候,大家可能就会有疑问,为什么只有ca0~ca5六根地址线,却可以识别出多达16个行地址和10个列地址?

答案是位宽不够、周期来凑。首先,LPDDR4同样在DQ和DM使用DDR采样,命令线SDR采样。为了减少命令线的数量,ddr采用了多个时钟周期来传输一个命令,在jedec上定义了1、2、4个时钟周期的命令行。通过多个时钟周期来传递一条指令,从而达到减小ca信号线数量的目的。

3.LPDDR4电气特性

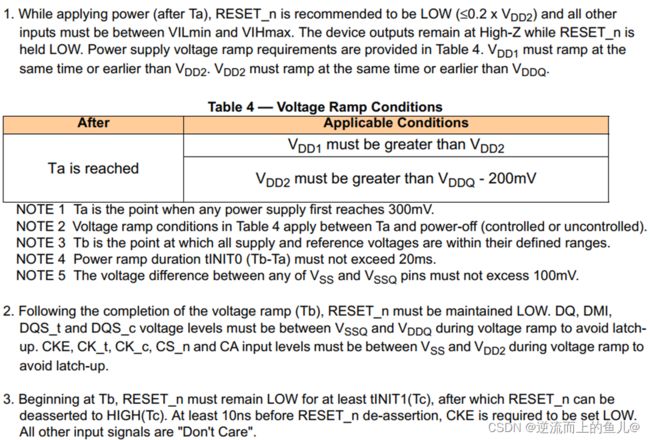

3.1 上电时序

1.上电前,reset保持低;

2.上电时序是VDD1 >= VDD2 >= (VDDQ-200mv)

3. 所有电源在20ms内上电

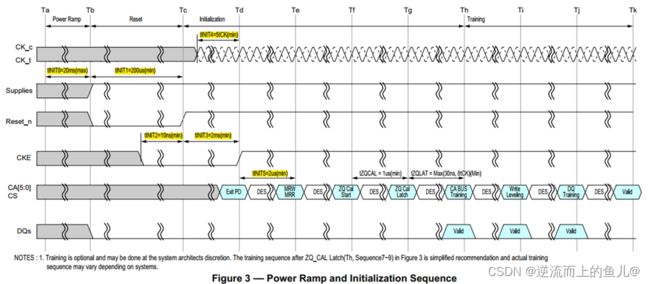

3.2 上电初始化时序

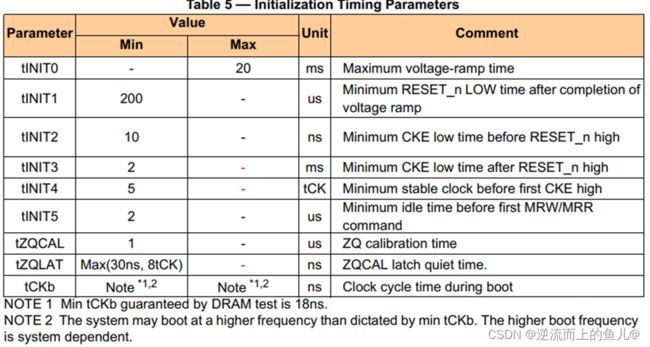

LPDDR4初始化有比较经典的几个时序需要测量,具体参考图和测试指标,在jedec上面有非常直观的给出,设计电源和控制器必须满足这个要求:

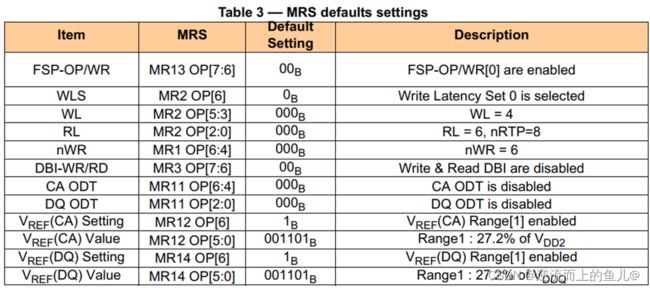

另外,在初始化过程中,为了防止DDR的功能异常。此时,一些重要的延时参数和ODT、vref采用默认值,默认值如下:

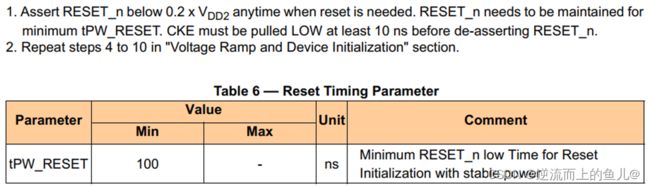

3.3 复位时序

- reset低电平信号质量满足<0.2*VDD

- 复位信号宽度大于100ns

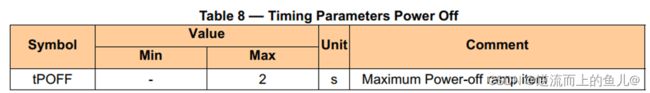

3.4 下电时序

同上电时序是VDD1 >= VDD2 >= (VDDQ-200mv)

最长下电时间<2s(到300mv)

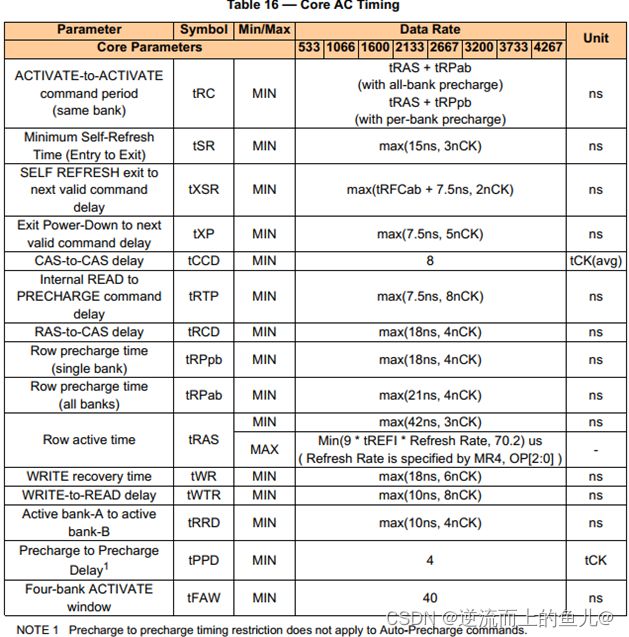

3.5 经典的核心时序

DDR核心时序的作用非常重要,通过合理的调整时序能够在相同频率总线下发挥超出设计的带宽,曾经红级一时的主板超频,就是通过调整DDR的核心时序来实现的。发烧友把时序区分成大时序和小时序,逐一调整,是主板发挥出更强的性能。LPDDR4的核心时序如下图,比较通俗。每个命令可以从2.3节的表格中查到。

3.6 DMI

LPDDR4的DBI管脚集成了DM(data mask)和DBI(Data bus inversion)两个功能。

DBI可以在读、写、Mask write、MRR、MRW操作中生效。读操作DMI可以通过MR3寄存器的OP6使能,写操作DMI可以通过MR13寄存器的OP5使能。

DBI功能在写操作中的作用:当给定的字节lane的DBI_n采集到低电平时,DRAM会反转DQ作为输入pin接收到的写操作数据。当给定的字节lane的DBI_n采集到高电平时,DRAM不会反转DQ作为输入pin接收到的写操作数据。

DBI功能在读操作中的作用:当写给给定字节lane的数据中‘0’的比特数大于4时,DRAM将会反转其输出到DQ作为输出pin上的读操作数据,并且驱动DBI_n pin为低电平。否则,DRAM将不会反转读操作数据,并且驱动DBI_n PIN为高电平

DM只支持写操作。DM功能在写操作中的作用:当给定的字节lane的DM_n采集到低电平时,DRAM会掩掉DQ作为输入pin接收到的写操作数据。当给定字节lane的DM_n采集到高电平时,DRAM不会掩掉DQ作为输入pin接收到的写操作数据,而会写到其core中。

DMI工作有如下多个状态:

![]()

3.7 ODT

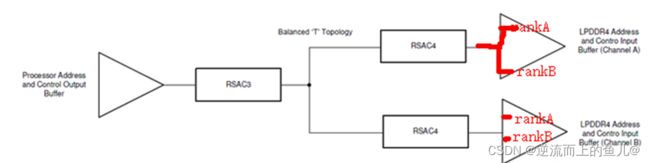

在LPDDR4中ODT支持DQ-ODT和CA-ODT,由于4die的DQ连接在各自的channel上,2 rank分时复用,所以所有DQ-ODT在write操作时全部打开。

但是,4 die CA连接在各自的rank上,并且呈树形连接在同一个sdram controller上。所以,需要通过ODT-CA来控制端接。

如上图,CA的ODT必须同时选择不工作的那一rank的两个颗粒做端接。比如,rankA工作,那么,就需要端接RankB的channelA和channelB。

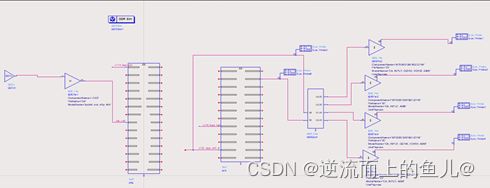

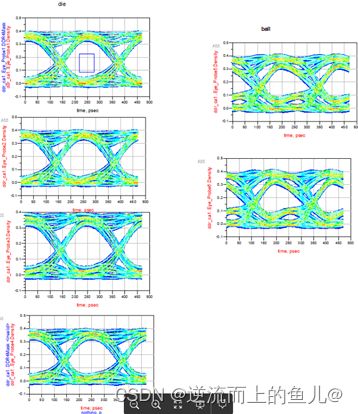

如下图,就算端接正确的情况和端接错误的情况:

仿真拓扑

正确的端接 错误的端接

3.8 ZQ校准

DQ是数据传输的双向PAD。在读操作时,DRAM需要提供合适的输出驱动电压Voh,在LPDDR4中规定为VDDQ/2.5或VDDQ/3,也即440mV和367mV, 它是靠DQ Pad内的上拉电阻网络来实现的。

在写操作时,作为接受方,DRAM的DQ会连接一个下拉的ODT 终止电阻(RTT),来改善信号完整性。

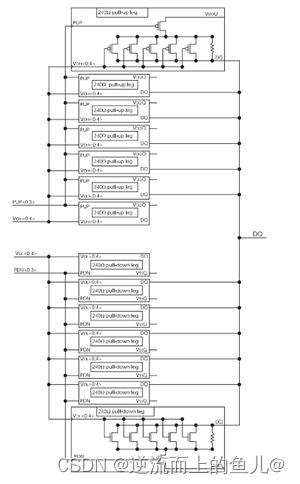

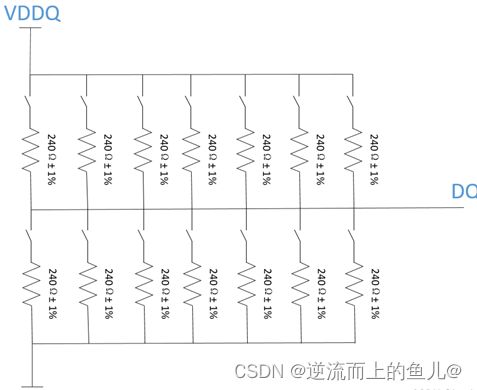

在早期的DDR中,DQ的上拉电阻和下拉电阻是分离结构,从DDR3开始采用上拉和下拉合并的电阻网络来实现,下图以DDR3中的上拉和下拉合并的电阻网络为例。

DQ Pad内部的电阻网络包含7个并联的上拉电阻,以及7个并联的下拉电阻。上拉连接VDDQ,下拉接地。每个电阻有多个CMOS生成(图中每个 240Ω pull up/down leg),且通过控制上部MOS管来和DQ导通或断开,每个在正常工作的时候应为240Ω。

在DQ作为输出时,断掉所有下拉电阻,只有上拉电阻和DQ连接,并且控制上拉电阻的导通个数,来控制输出Voh电压。

在DQ作为输入时,断掉所有上拉电阻,只有下拉电阻和DQ连接,从而构成ODT需要的下拉电阻。并且通过控制下拉电阻的导通个数,生成需要的不同电阻值的电阻

校准过程:

有对DQ Pad内部的上下拉电阻网络中的每个电阻进行校准,才能满足高频下信号完整性需求,这就用到了连接在ZQ Pad 外部的240Ω±1%参考电阻。

校准的前提是,我们认为该外部参考电阻不会随着环境变化,在任何条件下都是标准的240Ω。

DRAM内部对每个240Ω电阻进行校准时都会共用该外部参考电阻,因此每个电阻是分开进行校准,在时间上不能重叠。

对每个上拉电阻进行校准时,其校准电路如下:

其中左侧方框为校准控制模块,内部包含ADC, 比较器,择多滤波器(majority filter)。图中VDDQ/2作为参考电压,有DRAM内部产生。图中最右侧为一个近似电阻(approximation register,是polyresistor), 比240Ω稍大。和该240Ω+电阻并联的有5个P Channel device(如原文所述),通过控制其导通个数,来使其最终等效电阻最终等于240Ω

具体校准步骤如下:

- 收到ZQ校准命令后,PUP会被驱动为低电平,使和VDDQ连接的PMOS开关打开

- 校准控制模块通过调整VOH[0:4], 来使不同的P Channel device导通

- 比较VPULL-UP和VDDQ/2的电压,当二者相等时,DQ上下两侧的电阻相等,均为240Ω,校准完成

- 记录下该电阻的VOH[0:4]的值

- 对每个上拉电阻进行校准,记录下每个电阻对应的VOH[0:4]值

- 下拉电阻校准过程类似,不多赘述。不同的是和240Ω+电阻并联的是N Channel device。

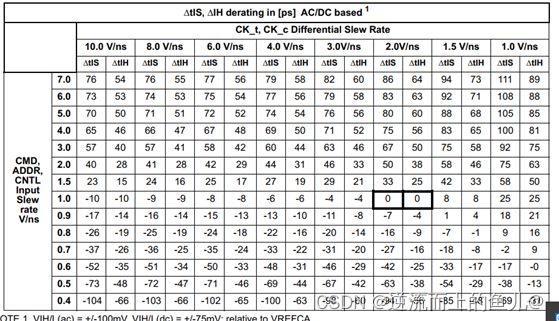

3.8 Vref

Vref偏移对DDR会造成什么影响,其中有比较重要的一个点就是会影响setuptime和holdtime。大家仔细观察在DDR的jedec上面对应的时序都有derating定义(由于我司的jedec标准都是未完善的A版本,可能看不到,截一个我之前的jesd79-4B),有兴趣可以去研究一下,derating预减是从0.5UI短,AC或DC门限到vref门限的值。所以说,这个门限会直接影响setuptime和holdtime。

LPDDR4的vref由内部网络提供复杂的training,具体training过程可以参考三星的手册,比较接近jesd209-4B的定义。

4.测量指标

测量指标在jedec上都有明确规定,比较简洁,这一节把主要测试指标归纳一下

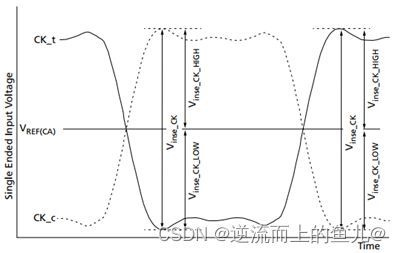

4.1 CLK

4.2 Cammand & address

4.3 DQS write

4.4 DQ write

4.5 DQ read

4.6 ODT-RESET-CKE

- 测试指导

2.1测试前准备

2.1.1示波器的选择及设置

示波器采用16G高速4通道

- 探头采用16GHz差分探头*4、

- 差分焊接组件

2.1.2测试注意事项

- 测试包括信号质量和时序测试,信号质量测试需要使用有源探头测试,并使用短地针,测试时候地的选择需要尽量靠近测试点。测试时序可以使用无源探头以及长地线。

- 测试点需要选择最靠近信号末端的测试点,如果有必要需要刮开过孔。

- 测试前需要保证板卡示波器接地。

- 测试需要佩戴静电手环。

- 测试时需要注意,测试信号上升下降时间时候需要把边沿展开观察单调性,数据不要求单调。

2.2信号测试

2.2.1读写分离方法

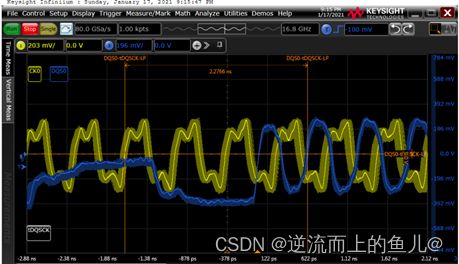

DDR测试界一个经久不衰的话题就是读写分离。的确,没有一定的经验,看到密密麻麻的波形去做读写分离还是比较困难的,本节介绍常见的几种读写分离方法。

1.利用preamble差异来区分读写

该方法对于DDR3来说非常直观,read preamble是负脉冲,weite preamble是正脉冲,只需要捕获DQS的Burst初始脉冲即可。可以使用window、欠幅、视频等方式触发。

但是,对于LPDDR4就不能使用这个方式了,LPDDR4的读写preamble跳变相同。但是,仔细阅读LPDDR4的标准就会发现,read的preamble可选为翻转或者不翻转,默认是不翻转。而且,大部分产品都不会去刻意配置,所以,可以根据preamble的翻转状态去区分读写。

Write Read

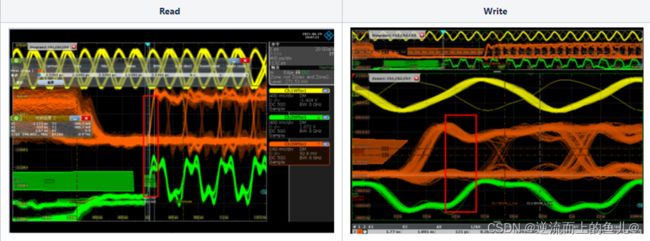

1.利用相位差分离读/写信号

读信号与写信号之间有一个重要差异:写数据是DQS和DQ Centre-Align(中间对齐), 读数据DQS和DQ是Edge-Align(边沿对齐),Memory Controller在接收到内存的读数据时,在controller内部把DQS和DQ的相位错开90度,实现中间对齐来采样

2.利用更大的信号幅度触发方法分离读/写信号

通常,读/写信号的信号幅度是不同的,因此我们可以通过在更大的信号幅度上触发示波器来实现两者的分离。一般在DRAM端进行测试时,写数据从Memory Controller出来,到达DRAM颗粒的时候,信号已经被衰减了,而读数据刚刚从DRAM出来,还没有经过任何的衰减,因此读数据的幅度要大于写数据

3.利用斜率差分离读/写信号

读数据的斜率大于写数据。在DRAM端进行测试时,写数据从Memory Controller出来,到达DRAM颗粒的时候,信号已经被衰减了,所以,斜率也小一些;而读数据刚刚从DRAM出来,还没有经过任何的衰减,因此读数据的斜率要大于写数据

4.利用脉冲宽度分离读/写信号

DQS是双向信号,读数据从DRAM出来,经过PCB走线到达Memory Controller;而写数据从Memory Controller出来,经过PCB走线到达DRAM。当在DRAM端进行测试时,读信号由于反射在信号边沿可能会存在回勾,信号宽度相对于写数据就有差异,这时就可以根据脉宽宽度对读/写信号进行分离。

2.2.2信号测试的内容

| 序号 |

测试项 |

描述 |

指标 |

备注 |

| 1 |

初始化测试 |

测试上下电、复位的信号质量和时序 |

见3.1~3.4 |

|

| 2 |

时钟测试 |

时钟的频率、信号质量、抖动 |

见4.1 |

|

| 3 |

命令线测试 |

命令线的时序、信号质量 |

见4.2 |

|

| 4 |

DQS、DQ写操作测试 |

DQ、DQS的写时序、信号质量 |

见4.3、4.4 |

|

| 5 |

读操作测试 |

DQ、DQS的读时序、信号质量 |

见4.5 |

|

| 6 |

状态信号测试 |

CA-OTD、RESET、CKE信号质量 |

见4.6 |