GD32F407之架构介绍

最近使用了国产的arm芯片GD32F407效果还是非常不错的,感觉和STM32F407类似度达99%,目前还没有感觉出来有很大的差别之处,可能库函数接口会不一样,但都是大同小异。

到官网下载Datasheet文档发现居然还是中文版的,有那么点点小惊喜,突然感觉中国真的强大了。话不多说,直接玩起来,相信大家玩M3或M4的板子大多应该是参考正点原子或者野火来的吧,所以就有那么点习惯按照正点或野火的目录结构来建工程,在建工程之前还是介绍一下GD32F407的性能。

1、系统及存储器架构

GD32F4xx系列器件是基于ARM® Cortex™-M4处理器的32位通用微控制器。ARM® Cortex™-M4处理器包括三条AHB总线分别称为I-CODE总线、D-Code总线和系统总线。Cortex™-M4处理器的所有存储访问,根据不同的目的和目标存储空间,都会在这三条总线上执行。存储器的组织采用了哈佛结构,预先定义的存储器映射和高达4 GB的存储空间,充分保证了系统的灵活性和可扩展性。

2、ARM Cortex-M4处理器

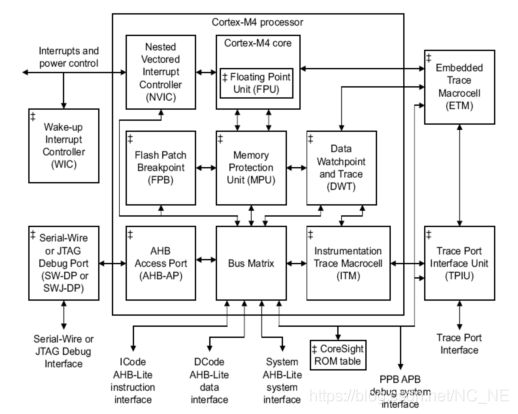

Cortex™-M4处理器是一个具有浮点运算功能、低中断延迟时间和低成本调试特性的32位处理器。高集成度和增强的特性使Cortex™-M4处理器适合于那些需要高性能和低功耗微控制器的市场领域。Cortex™-M4处理器基于ARMv7架构,并且支持一个强大且可扩展的指令集,包括通用数据处理I/O控制任务、增强的数据处理位域操作、DSP(数字信号处理)和浮点运算指令。下面列出由Cortex™-M4提供的一些系统外设:

- 内部总线矩阵,用于实现I-Code总线、D-Code总线、系统总线、专用总线(PPB)以及调试专用总线(AHB-AP)的互联;

- 嵌套式向量型中断控制器 (NVIC);

- 闪存地址重载及断点单元 (FPB);

- 数据观测点及跟踪单元(DWT);

- 指令跟踪宏单元 (ITM);

- 嵌入式跟踪宏单元 (ETM);

- 串行线和JTAG调试接口 (SWJ-DP);

- 跟踪端口接口单元 (TPIU);

- 内存保护单元 (MPU);

- 浮点运算单元 (FPU)。

个人感觉对于浮点运算感觉还是不太行,我在函数里面做浮点计算直接卡机,有待提高啊

Cortex™-M4结构框图

3、系统架构

GD32F4xx系列器件采用32位多层总线结构,该结构可使系统中的多个主机和从机之间的并行通信成为可能。多层总线结构包括一个AHB互联矩阵、两个AHB总线和两个APB总线。

GD32F4xx器件的系统架构示意图

非常重要的一张图,可以看到每个设备挂载在那个时钟下,这样配置时钟就一目了然了

4、片上SRAM存储器

GD32F4xx系列微控制器可以提供高密度片上FLASH存储器,按以下分类进行组织:

- 高达3072KB主FLASH存储器;(非常奢侈豪华啊)

- 高达30KB引导装载程序(boot loader)信息块存储器;

- 高达512B OTP(一次性可编程)存储器;

- 器件配置的选项字节。

5、引导配置

GD32F4xx系列微控制器提供了三种引导源,可以通过BOOT0和BOOT1引脚来进行选择,详细说明见表1-3. 引导模式。该两个引脚的电平状态会在复位后的第四个CK_SYS(系统时钟)的上升沿进行锁存。用户可自行选择所需要的引导源,通过设置上电复位和系统复位后的BOOT0和BOOT1的引脚电平。一旦这两个引脚电平被采样,它们可以被释放并用于其他用途。

引导模式表:

一定要注意这个上电引导选择,不然让你折腾半天都找不到,深坑预警

上电序列或系统复位后,ARM®Cortex™-M4处理器先从0x00000000地址获取栈顶值,再从0x00000004地址获得引导代码的基地址,然后从引导代码的基地址开始执行程序。所选引导源对应的存储空间会被映射到引导存储空间,即从0x0000 0000开始的地址空间。如果片上SRAM(开始于0x20000000的存储空间)被选为引导源,用户必须在应用程序初始化代码中通过修改NVIC异常向量表和偏移地址将向量表重置到SRAM中。当主FLASH存储器被选择作为引导源,从0x0800 0000开始的存储空间会被映射到引导存储空间。由于主FLASH存储器的Bank0或Bank1均可映射到地址0x0800 0000(通过配置SYSCFG_CFG0寄存器的FMC_SWP控制位),所以,微控制器可以使用该方法从Bank0或Bank1中启动。

引导装载程序在GigaDevice生产器件的过程中已经被编程,用于通过以下其中一个通信接口重新编程主FLASH存储器:USART0(PA9和PA10)、USART2 (PB10和PB11或PC10 and PC11)。

一般我们都是使用主FLASH,毕竟资源优势摆在那

6、搭建简易工程项目

目录结构如图:

代码下载路径:(开头)https://download.csdn.net/download/NC_NE/12398199