FPGA实现双线性插值任意比例的图像缩放,HLS封装IP,提供两套工程源码

目录

- 1.双线性插值算法简介

- 2.双线性插值算法的HLS实现与IP封装

- 3.vivado工程介绍

- 4.OV5640摄像头720P原分辨率输出实验

- 5.OV5640摄像头720P缩小到640X480输出实验

- 6.OV5640摄像头720P放大到1080P输出实验

- 6.福利:工程源码获取

1.双线性插值算法简介

已知的红色数据点与待插值得到的绿色点。

假如我们想得到未知函数 f 在点 P= (x,y) 的值,假设我们已知函数 f 在 Q11 = (x1,y1)、

Q12 = (x1,y2),Q21 = (x2,y1) 以及 Q22 = (x2,y2) 四个点的值。

首先在 x 方向进行线性插值,得到 R1 和 R2,然后在 y 方向进行线性插值,得到 P。

这样就得到所要的结果 f(x,y)。

其中红色点 Q11,Q12,Q21,Q22 为已知的 4 个像素点.

第一步:X 方向的线性插值,在 Q12,Q22 中插入蓝色点 R2,Q11,Q21 中插入蓝色点

R1;

第二步:Y 方向的线性插值,通过第一步计算出的 R1 与 R2 在 y 方向上插值计算出 P

点。

线性插值的结果与插值的顺序无关。首先进行 y 方向的插值,然后进行 x 方向的插值,

所得到的结果是一样的。双线性插值的结果与先进行哪个方向的插值无关。

如果选择一个坐标系统使得四个已知点坐标分别为 (0, 0)、(0, 1)、(1, 0) 和 (1, 1),那

么插值公式就可以化简为

f(x,y)=f(0,0)(1-x)(1-y)+f(1,0)x(1-y)+f(0,1)(1-x)y+f(1,1)xy

具体的双线性插值算法描述如下:

对于一个目标像素,通过反向变换得到的浮点坐标为(i+u,j+v) (其中 i、j 均为浮点坐标

的整数部分,u、v 为浮点坐标的小数部分,是取值[0,1)区间的浮点数),则这个像素值 f(i+u,

j+v) 可由原图像中坐标为 (i,j)、(i+1,j)、(i,j+1)、(i+1,j+1)所对应的周围四个像素的值决

定,即:

f(i+u,j+v) = (1-u)(1-v)f(i,j) + (1-u)vf(i,j+1) + u(1-v)f(i+1,j) + uvf(i+1,j+1)

其中 f(i,j)表示源图像(i,j)处的的像素值,以此类推。

比如,刚才的例子,现在假定目标图的像素坐标为(1,1),那么反推得到的对应于源

图的坐标是(0.75 , 0.75), 这其实只是一个概念上的虚拟像素,实际在源图中并不存在

这样一个像素,那么目标图的像素(1,1)的取值不能够由这个虚拟像素来决定,而只能由

源图的这四个像素共同决定:(0,0)(0,1)(1,0)(1,1),而由于(0.75,0.75)离(1,

1)要更近一些,那么(1,1)所起的决定作用更大一些,这从公式 1 中的系数 uv=0.75×0.75

就可以体现出来,而(0.75,0.75)离(0,0)最远,所以(0,0)所起的决定作用就要小

一些,公式中系数为(1-u)(1-v)=0.25×0.25 也体现出了这一特点。

2.双线性插值算法的HLS实现与IP封装

建立HLS工程,粘贴复制源码编译即可,然后封装IP,**“关注并私信我”**获得HLS源码。

封装后的IP如下图:

IP不需要点击配置,直接连线即可使用。

3.vivado工程介绍

FPGA型号:zynq7100,可移植到其他型号;

vivado版本:2019.1;

测试使用模块:OV5640 摄像头;

放大测试:将 720P 分辨率图像放大到 1080P。

缩小测试:将 720P 分辨率图像缩小到 640x480。

本章实现的缩放 IP 主要用于功能验证,可以在此基础上,对数据流进行进一步处理,

这里不在赘述。

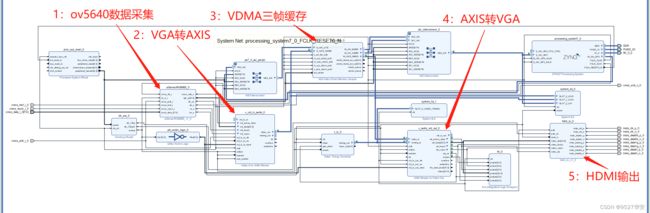

4.OV5640摄像头720P原分辨率输出实验

此工程的目的是为了对比缩放的效果;

输入:OV5640 摄像头,分辨率720P;

输出:HDMI显示背景1080P,有效图像区720P;

BD工程如下:

SDK配置:

#include "I2C_16bit.h"

#include "xiicps.h"

#include "xil_io.h"

#include "xparameters.h"

#include "color.h"

#define VDMA_BASEADDR XPAR_AXI_VDMA_0_BASEADDR

#define VIDEO_BASEADDR0 0x01000000

#define VIDEO_BASEADDR1 0x02000000

#define VIDEO_BASEADDR2 0x03000000

#define H_ACTIVE 1920

#define V_ACTIVE 1080

#define H_STRIDE 1920

XIicPs Iic;

u32 i=0;

//#define SUM 8294400 //背景写黑 1920*1080*4

#define SUM H_ACTIVE*V_ACTIVE*4 //背景写黑 1920*1080*4

void main()

{

// Initialize OV5640 regesiter

I2C_config_init();

//设置内存中的背景

for(i=0;i<SUM;i++){

Xil_Out16((VIDEO_BASEADDR0 + i), 0x00);

Xil_Out16((VIDEO_BASEADDR1 + i), 0x00);

Xil_Out16((VIDEO_BASEADDR2 + i), 0x00);

}

//VDMA_WRITE

Xil_Out32((VDMA_BASEADDR + 0x030), 0x108B);// enable circular mode

Xil_Out32((VDMA_BASEADDR + 0x0AC), VIDEO_BASEADDR0); // start address

Xil_Out32((VDMA_BASEADDR + 0x0B0), VIDEO_BASEADDR1); // start address

Xil_Out32((VDMA_BASEADDR + 0x0B4), VIDEO_BASEADDR2); // start address

Xil_Out32((VDMA_BASEADDR + 0x0A8), (H_STRIDE*3)); // h offset (H_STRIDE* 3) bytes

Xil_Out32((VDMA_BASEADDR + 0x0A4), (H_ACTIVE*3)); // h size (H_ACTIVE * 3) bytes

Xil_Out32((VDMA_BASEADDR + 0x0A0), V_ACTIVE); // v size (V_ACTIVE)

//VDMA_READ

Xil_Out32((VDMA_BASEADDR + 0x000), 0x8B); // enable circular mode

Xil_Out32((VDMA_BASEADDR + 0x05c), VIDEO_BASEADDR0); // start address

Xil_Out32((VDMA_BASEADDR + 0x060), VIDEO_BASEADDR1); // start address

Xil_Out32((VDMA_BASEADDR + 0x064), VIDEO_BASEADDR2); // start address

Xil_Out32((VDMA_BASEADDR + 0x058), (H_STRIDE*3)); // h offset (H_STRIDE * 3) bytes

Xil_Out32((VDMA_BASEADDR + 0x054), (H_ACTIVE*3)); // h size (H_ACTIVE * 3) bytes

Xil_Out32((VDMA_BASEADDR + 0x050), V_ACTIVE); // v size (V_ACTIVE)

while (1) ;

}

输出显示如下:

请注意看原图视野,以便和后面的缩放做对比;

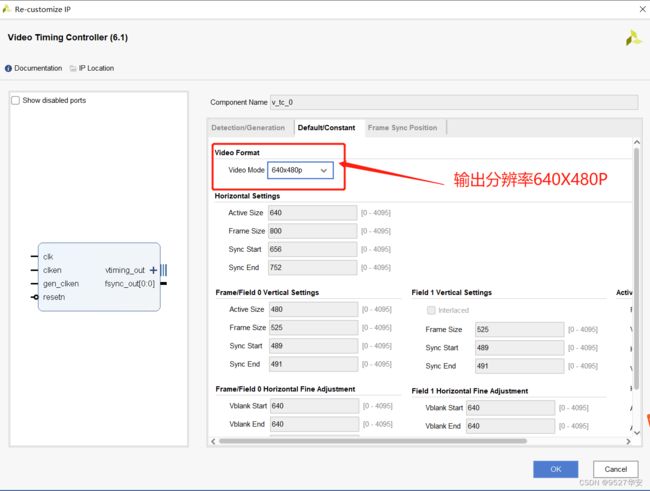

5.OV5640摄像头720P缩小到640X480输出实验

此工程的目的是为了对比缩小的效果;

输入:OV5640 摄像头,分辨率720P;

输出:HDMI显示640X480P分辨率;

BD工程如下:

其中输出分辨率为640X480P,如下:

SDK配置:

#include "I2C_16bit.h"

#include "xiicps.h"

#include "xil_io.h"

#include "xparameters.h"

#include "color.h"

#include "xhls_video_scaler_top.h"

#define VDMA_BASEADDR XPAR_AXI_VDMA_0_BASEADDR

#define XPAR_HLS_VIDEO_SCALER_TOP_DEVICE_ID XPAR_HLS_VIDEO_SCALER_TOP_0_DEVICE_ID

#define VIDEO_BASEADDR0 0x01000000

#define VIDEO_BASEADDR1 0x02000000

#define VIDEO_BASEADDR2 0x03000000

//输出分辨率640X480P

#define H_ACTIVE 640

#define V_ACTIVE 480

#define H_STRIDE 640

XHls_video_scaler_top XHls_video_scaler;

XIicPs Iic;

u32 i=0;

#define SUM H_ACTIVE*V_ACTIVE*4 //背景写黑 1920*1080*4

void main()

{

// Initialize OV5640 regesiter

I2C_config_init();

//设置内存中的背景

for(i=0;i<SUM;i++){

Xil_Out16((VIDEO_BASEADDR0 + i), 0x00);

Xil_Out16((VIDEO_BASEADDR1 + i), 0x00);

Xil_Out16((VIDEO_BASEADDR2 + i), 0x00);

}

//scaler720P-->480X640

XHls_video_scaler_top_Initialize(&XHls_video_scaler, XPAR_HLS_VIDEO_SCALER_TOP_DEVICE_ID);

XHls_video_scaler_setup(720,1280,480,640);

//VDMA_WRITE

Xil_Out32((VDMA_BASEADDR + 0x030), 0x108B);// enable circular mode

Xil_Out32((VDMA_BASEADDR + 0x0AC), VIDEO_BASEADDR0); // start address

Xil_Out32((VDMA_BASEADDR + 0x0B0), VIDEO_BASEADDR1); // start address

Xil_Out32((VDMA_BASEADDR + 0x0B4), VIDEO_BASEADDR2); // start address

Xil_Out32((VDMA_BASEADDR + 0x0A8), (H_STRIDE*3)); // h offset (H_STRIDE* 3) bytes

Xil_Out32((VDMA_BASEADDR + 0x0A4), (H_ACTIVE*3)); // h size (H_ACTIVE * 3) bytes

Xil_Out32((VDMA_BASEADDR + 0x0A0), V_ACTIVE); // v size (V_ACTIVE)

//VDMA_READ

Xil_Out32((VDMA_BASEADDR + 0x000), 0x8B); // enable circular mode

Xil_Out32((VDMA_BASEADDR + 0x05c), VIDEO_BASEADDR0); // start address

Xil_Out32((VDMA_BASEADDR + 0x060), VIDEO_BASEADDR1); // start address

Xil_Out32((VDMA_BASEADDR + 0x064), VIDEO_BASEADDR2); // start address

Xil_Out32((VDMA_BASEADDR + 0x058), (H_STRIDE*3)); // h offset (H_STRIDE * 3) bytes

Xil_Out32((VDMA_BASEADDR + 0x054), (H_ACTIVE*3)); // h size (H_ACTIVE * 3) bytes

Xil_Out32((VDMA_BASEADDR + 0x050), V_ACTIVE); // v size (V_ACTIVE)

while (1) ;

}

输出显示如下:

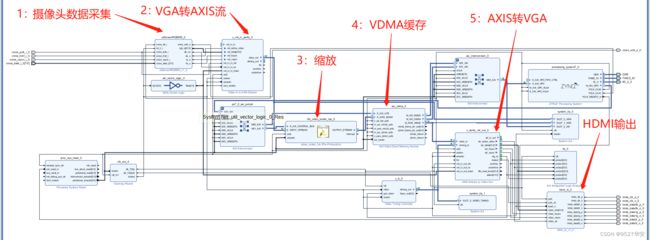

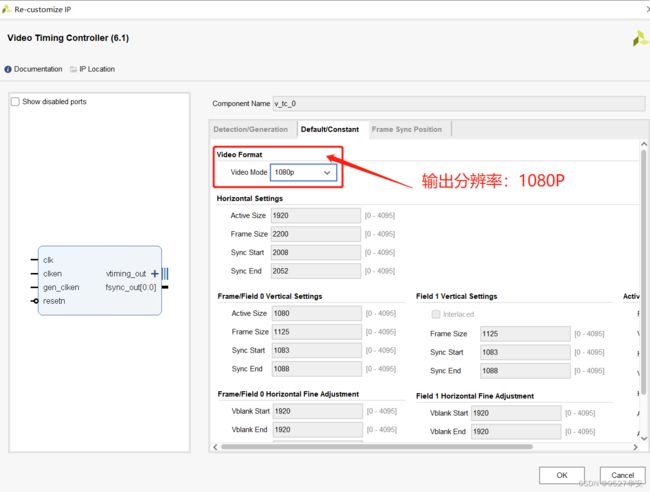

6.OV5640摄像头720P放大到1080P输出实验

此工程的目的是为了对比放大的效果;

输入:OV5640 摄像头,分辨率1080P;

输出:HDMI显示1080P分辨率;

BD工程如下:

其中输出分辨率为1080P,如下:

SDK配置:

#include "I2C_16bit.h"

#include "xiicps.h"

#include "xil_io.h"

#include "xparameters.h"

#include "color.h"

#include "xhls_video_scaler_top.h"

#define VDMA_BASEADDR XPAR_AXI_VDMA_0_BASEADDR

#define XPAR_HLS_VIDEO_SCALER_TOP_DEVICE_ID XPAR_HLS_VIDEO_SCALER_TOP_0_DEVICE_ID

#define VIDEO_BASEADDR0 0x01000000

#define VIDEO_BASEADDR1 0x02000000

#define VIDEO_BASEADDR2 0x03000000

//输出分辨率:1080P

#define H_ACTIVE 1920

#define V_ACTIVE 1080

#define H_STRIDE 1920

XHls_video_scaler_top XHls_video_scaler;

XIicPs Iic;

u32 i=0;

#define SUM H_ACTIVE*V_ACTIVE*4 //背景写黑 1920*1080*4

void main()

{

// Initialize OV5640 regesiter

I2C_config_init();

//设置内存中的背景

for(i=0;i<SUM;i++){

Xil_Out16((VIDEO_BASEADDR0 + i), 0x00);

Xil_Out16((VIDEO_BASEADDR1 + i), 0x00);

Xil_Out16((VIDEO_BASEADDR2 + i), 0x00);

}

scaler720P-->1080P

XHls_video_scaler_top_Initialize(&XHls_video_scaler, XPAR_HLS_VIDEO_SCALER_TOP_DEVICE_ID);

XHls_video_scaler_setup(720,1280,720,1280);

//VDMA_WRITE

Xil_Out32((VDMA_BASEADDR + 0x030), 0x108B);// enable circular mode

Xil_Out32((VDMA_BASEADDR + 0x0AC), VIDEO_BASEADDR0); // start address

Xil_Out32((VDMA_BASEADDR + 0x0B0), VIDEO_BASEADDR1); // start address

Xil_Out32((VDMA_BASEADDR + 0x0B4), VIDEO_BASEADDR2); // start address

Xil_Out32((VDMA_BASEADDR + 0x0A8), (H_STRIDE*3)); // h offset (H_STRIDE* 3) bytes

Xil_Out32((VDMA_BASEADDR + 0x0A4), (H_ACTIVE*3)); // h size (H_ACTIVE * 3) bytes

Xil_Out32((VDMA_BASEADDR + 0x0A0), V_ACTIVE); // v size (V_ACTIVE)

//VDMA_READ

Xil_Out32((VDMA_BASEADDR + 0x000), 0x8B); // enable circular mode

Xil_Out32((VDMA_BASEADDR + 0x05c), VIDEO_BASEADDR0); // start address

Xil_Out32((VDMA_BASEADDR + 0x060), VIDEO_BASEADDR1); // start address

Xil_Out32((VDMA_BASEADDR + 0x064), VIDEO_BASEADDR2); // start address

Xil_Out32((VDMA_BASEADDR + 0x058), (H_STRIDE*3)); // h offset (H_STRIDE * 3) bytes

Xil_Out32((VDMA_BASEADDR + 0x054), (H_ACTIVE*3)); // h size (H_ACTIVE * 3) bytes

Xil_Out32((VDMA_BASEADDR + 0x050), V_ACTIVE); // v size (V_ACTIVE)

while (1) ;

}

输出显示如下: