目录

一、存储器的校验概述

1、编码的最小距离

2、汉明码校验

(1)奇偶校验

(2)汉明码计算

(3)习题

(3)汉明码的纠错

(4)汉明码的纠错过程

二、提高访存速度的措施

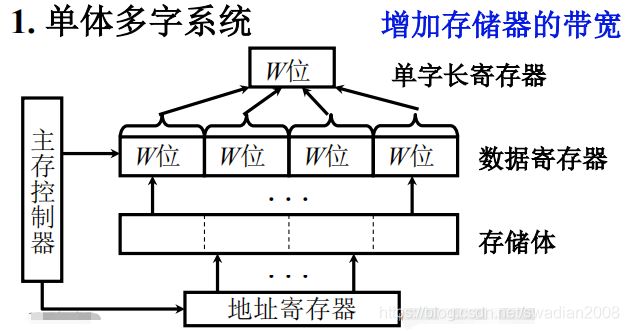

1、单字体系统

2、单体改进——>多体并行系统

(1)高位交叉——用于存储容量拓展

(2)低位交叉——用于带宽访问速度提高

3、高性能存储芯片

(1)SDRAM (同步 DRAM)

(2)RDRAM

(3)带 Cache 的 DRAM

一、存储器的校验概述

为什么要对存储器的信息进行校验?

以内存为例,内存是电子设备,信息保存在电容当中,若采用静态RAM,则是保存在四管的触发器当中。若内存所处的电磁环境比较复杂,或在空间环境下受到带电粒子的打击,可能造成电容的充放电或触发器的翻转,存在在存储器的信息可能会出错。

1、编码的最小距离

编码的检测能力和纠错能力与任意两组合法代码之间二进制位的最少差异数有关。

解释:

合法集合 {000 , 001 , 010 , 011 , 100 , 101 , 110 , 111} ,在此集合中,改变任意一个代码,比如改为001,001在合法集合中,所以不论改哪一个代码,总能在集合中找到对应的合法代码,因此这组合法代码,最少差异数为1,不能检测出错误,即 检0位错,纠0位错。

合法集合 {000 , 011 , 101 ,110},在此集合中,改变任意一个代码,比如改为001,001不在合法集合中,那么可以检测出错误,但是不能确定是集合中哪一个代码发生了错误,因为所有的合法代码改变一位后,都可以变成001,所有两组合法代码之间二进制位的最少差异数为2时, 检1位错,纠0位错。

合法集合 {000 , 111} ,在合法集合中,改变任意一个代码,比如改为001,001不在合法集合中,那么可以检测出错误,而且根据错误率错一位的机率为90%的统计,我们认为是代码000错误了一位,因此,两组合法代码之间二进制位的最少差异数为3时, 检1位错,纠1位错 。

检错纠错位数和码距之间的关系

L - 1 = D + C (D>=C,检测错误的位数总是大于等于纠正错误的位数)

- L ——> 编码的最小距离

- D ——> 检测错误的位数

- C ——> 纠正错误的位数

因此,我们可以知道,如果想要检1位错,纠1位错,编码的最小距离为3。

2、汉明码校验

(1)奇偶校验

所谓的奇偶校验,就是在原校验数据上添加一位1或者0,使数据中的1的个数为奇数个或者偶数个。为奇数个为奇校验,为偶数为偶校验。

以偶校验为例,上图,添加一位1后,使校验数据中的1的个数为偶数个,如果接收的结果1的位数不为偶数,那么可以检验出原数据出现了错误。

另外,为了更进一步细分错误校验,我们可以把原校验数据进行分组,如上,我们把校验数据划分为2组,分别添加校验位。

(2)汉明码计算

汉明码校验是一种非划分方式(组与组之间是有重叠的)

汉明码的目的是能够纠正一位误码( 汉明码默认一串数据只错一位)。假设信息码共有 n 位,汉明码共有 r 位,那么总共的码长为 n + r 位。为能检测出 n + r 位编码中其中一位的错误,汉明码必须能够表示至少 n + r + 1 种状态,其中 n + r 种表示 n + r 位编码中有一位错误,另外还需要一种来表示整个编码正确无误。则汉明码的长度需要满足下列关系:

2^r >= n + r + 1

信息码 n 位,汉明码 r 位,总共码长 n + r 位

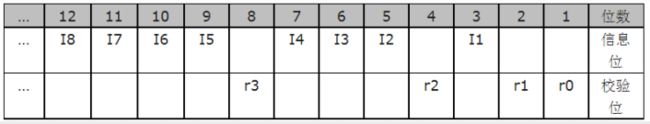

汉明码的位置

汉明码的校验码的位置必须是在2^n位置(n从0开始,分别代表从右边数起的第1,2,4,8,16...),信息码也就是在非2^n位置。

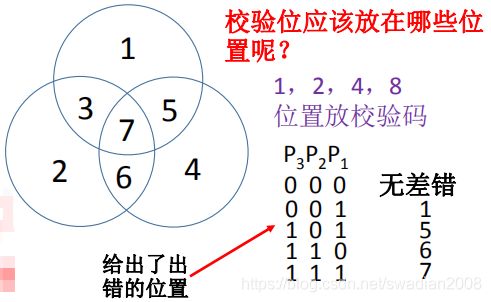

例如:对1,2,3,4,5,6,7进行汉明码校验,按照二进制编码,如果二进制码的第一位为1,分为第一组,二进制编码的第二位为1,分为第二组,以此类推...,

分完组后,校验码的位置必须是在 2^n的位置,我们知道最大数7的二进制码为111,因此,根据汉明码长度需要满足的关系式:2^r >= 3 + r + 1;可以求得校验码的最小长度为3位;

由此也可以知1,2,4位置为放置汉明码的位置。

(3)习题

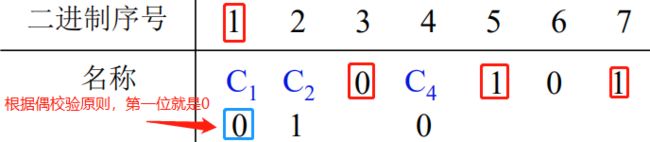

求 0101 按 “偶校验” 配置的汉明码

∵ n = 4

根据 2^r ≥ n + r + 1

得 r = 3

汉明码排序如下:

我们知道,校验码有3位,先在1,2,4位占据校验码的3个位置,空余的位置把需要校验的二进制码依次填充上去。先看第一个校验码,第一组校验1,3,5,7位,排序中,3,5,7的位置为011,根据偶校验原则,我们只需在前边补0就可以,那么0就是第一个校验码。根据此方法,可以得出后两个校验码为10;

因此,可以求得0101 的汉明码为

01 0 0 101

(3)汉明码的纠错

已知接收到的汉明码为 0100111 , (按配偶原则配置)试问要求传送的信息是什么 ?

纠错过程如下:

7位汉明码,根据公式:2^k>=n+k+1;可以得出k最小位3;也就是校验码的个数为3,分组为3;

根据偶校验的原则,我们分别对每一位的信息进行抑或运算:

校验码是011,也就是说,第二组和第三组存在错误,第二组和第三组共有的数据是第6位的数据, 可纠正为 01001 0 1;

故要传送的信息为 01 0 0 101 ;去除校验位,即为0101

(4)汉明码的纠错过程

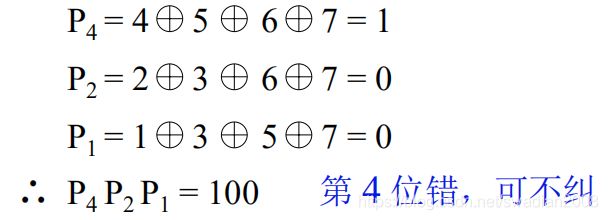

写出按偶校验配置的汉明码 0101101 的纠错过程

解题思路,根据收到的汉明码,对三个分组进行抑或运算,可以看出,错误的位数在第三组,也就是第4位,但是第4位是校验位,不是信息数据,所以纠不纠错都没有关系。

二、提高访存速度的措施

原因:CPU的运行效率提升比存储器的访问速度提升要快,发展趋势成剪刀差形式。

提高访存速度的措施主要有:

(1)采用高速器件

(2)采用层次结构 Cache-主存 ——>常用的指令放在Cache当中

(3)调整主存结构

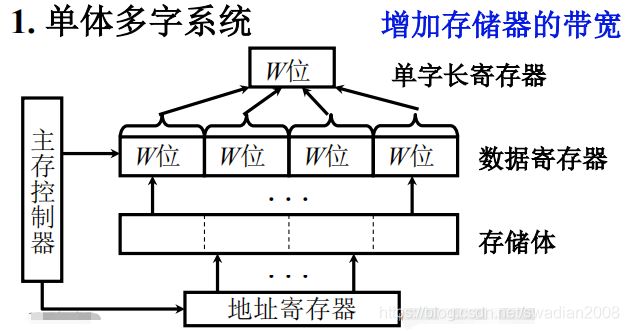

1、单字体系统

原假设存储字长等于机器字长,也就是说CPU一次从存储器当中只能取出一条指令(与机器字长相等的数据)

单体多字系统:把存储器的存储字长加长(增加存储器的带宽),比如,CPU为16位,存储字长我们可以设计成64位,CPU每一次访问存储器,都可以访问出4个机器字(4条指令),下一次再取指令时,就可以从数据寄存器当中读取指令。

单体多字系统的缺陷:

(1)CPU如果需要存储16位数据,需要先把数据放在单字长寄存器中,再放入数据寄存器中,然后再存储到存储体中,如果想要避免无关的48位数据被修改,还要设计更复杂的硬件逻辑。

(2)如果CPU读取的指令不是连续的存储的指令,那么取出的多余指令就是用不到的指令。

2、单体改进——>多体并行系统

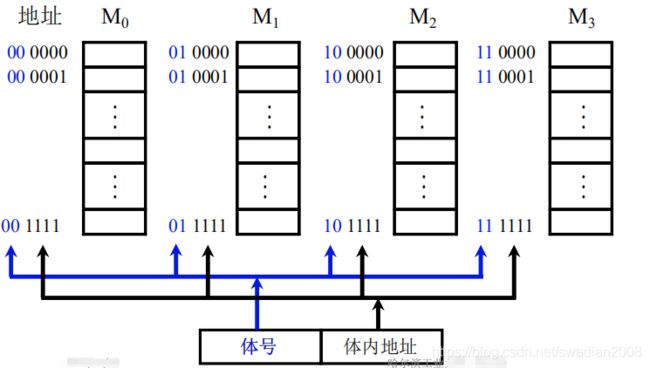

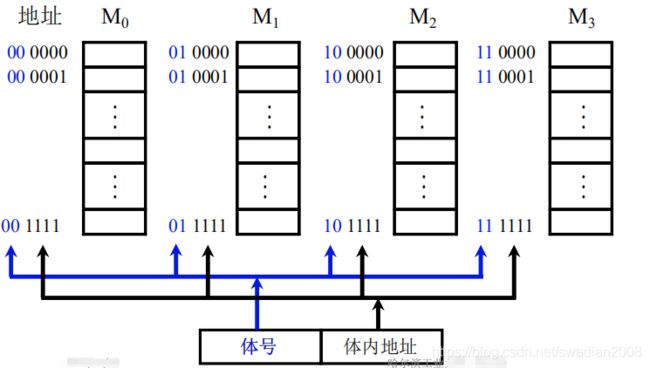

(1)高位交叉——用于存储容量拓展

顺序对存储体进行编码(编完第一个存储体,再编第二个存储体),前两位00为存储体的编号,后四位为存储体中的地址的编号,每一个存储体都有单独的数据寄存器和地址寄存器,能独立处理读写信号,从而达到4个存储体并行工作的效果。

不足:如果按序存储和按序读取,那么4个存储体中,可能存在有一个存储体非常繁忙,而其他几个存储体非常空闲的情况。

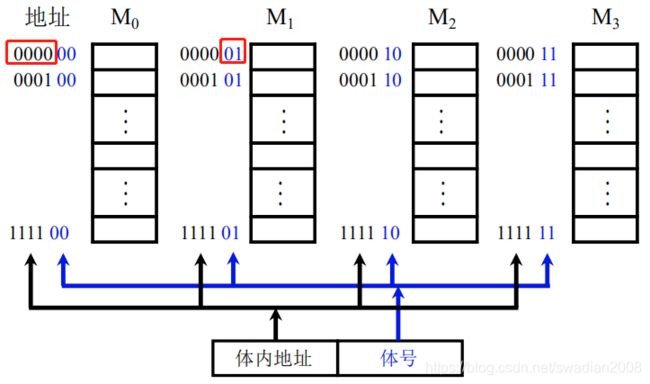

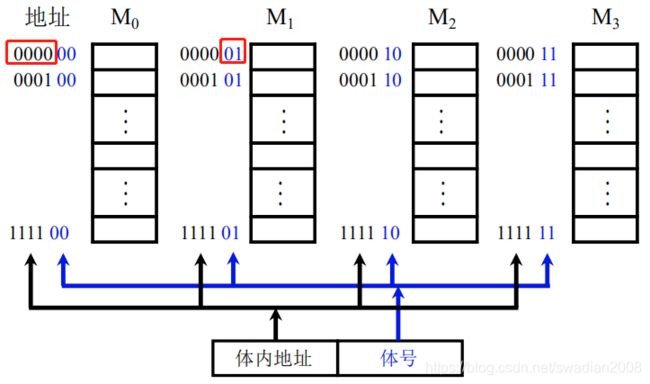

(2)低位交叉——用于带宽访问速度提高

对高位交叉进行改进,横向对存储体进行编码(第一个存储体和第二个存储体轮流进行编码),前四位为存储体中的地址的编号,后两位为存储体的地址。

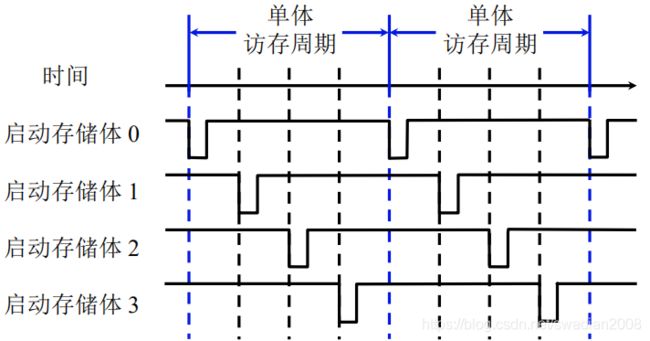

低位交叉的特点: 在不改变存取周期的前提下,增加存储器的带宽

上图显示了,在一个访存周期内,可分为4个小访存时间,每个小的访存时间可以分别控制一个存储体进行读写。

设四体低位交叉存储器,存取周期为 T,总线传输周期为 τ ,为实现流水线方式存取,应满足 T = 4 τ 。

连续读取 4 个字所需的时间为 T + (4 - 1) τ

总结:采用单体多字系统提高访存速度办法的前提是, 指令和数据在主存内必须是连续存放的,一旦遇到转移指令、或者操作数据不能连续存放,这种方法的效果就不明显。

3、高性能存储芯片

(1)SDRAM (同步 DRAM)

在系统时钟的控制下进行读出和写入—— CPU 无须等待

(2)RDRAM

由 Rambus 开发,主要解决 存储器带宽 问题

(3)带 Cache 的 DRAM

在 DRAM 的芯片内 集成 了一个由 SRAM 组成的 Cache ,有利于 猝发式读取 (连续的存储单元进行读取)