寄生感知共质心 FinFET 布局和布线以实现电流比匹配

摘要 2016

由于更有效的通道控制和更低的功耗,FinFET 技术被认为是现代高性能和低功耗集成电路设计的更好替代方案。 然而,与传统平面CMOS技术相比,基于FinFET技术的工艺变化导致的栅极错位问题和互连线产生的寄生电阻变得更加严重。 这种栅极未对准和不想要的寄生电阻可能会增加阈值电压并降低晶体管的漏极电流。 在将 FinFET 技术应用于模拟电路设计时,漏极电流的变化会破坏晶体管之间的电流比匹配并降低电路性能。 在本文中,我们介绍了第一个 FinFET 布局和布线算法,用于生成共质心 FinFET 阵列的布局,以精确匹配晶体管之间的电流比。 实验结果表明,与最先进的共质心布局器相比,所提出的匹配驱动的 FinFET 布局布线算法可以获得最佳的电流比匹配。

背景

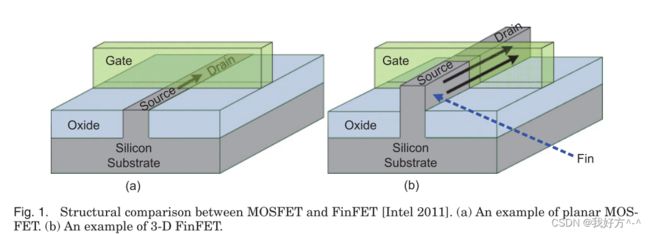

在现代片上系统 (SoC) 设计中,晶体管的电压已从传统的超阈值区域积极运行到亚/接近阈值区域,以有效降低集成电路的功耗 [Dreslinski 等人。. 当MOSFET工作在导通状态时,它在栅电极下方的硅区形成一个导电沟道,如图1(a)所示。 随着传统的平面 CMOS 技术缩小到 22nm 节点及以上,导电通道变得更短,更难以有效控制短通道效应 (SCE) [ITRS 2012]。 因此,高泄漏电流和阈值电压变化将显着影响电路性能、功耗和电路的可靠性。

为了克服平面 CMOS 微缩的困难,已经开发了几种新的器件技术作为体硅 MOSFET 结构的替代品,以提高可靠性。 在这些器件技术中,鳍式场效应晶体管 (FinFET) 的三维 (3-D) 方面被认为是最有希望替代体硅 MOSFET 以实现最终缩放的技术之一 [Chiarella 等人。 2010]。 当 FinFET 在导通状态下工作时,它会形成一个由垂直硅“鳍”包裹的导电通道,如图 1(b) 所示。 采用环绕式栅极结构,FinFET 可以更好地控制漏源沟道以减轻 SCE,并通过近本征沟道掺杂减少随机掺杂剂波动 [Rasouli 等人。 2009]; 因此,泄漏电流和阈值电压变化都可以显着降低 [Chiarella 等人。 2010]。 有了这些优点,有人建议设计带有 FinFET 的模拟集成电路,以更好地提高功率、性能和芯片面积 [Wambacq 等人。 2007]。 虽然 FinFET 技术可以有效地减少 SCE 的影响,并有利于集成电路的功率、性能和芯片面积,但一些光刻技术引起的工艺变化和布局引起的寄生效应变得更加严重。

1.1。 由于栅极失准导致的电流失配

由于栅极未对准,FinFET 的印刷栅极位置可能会在经过一组光刻工艺后偏离预期位置,这会增加阈值电压并降低 FinFET 的漏极电流 [Valin et al. 2012; 富尔德等人。 2007; 萨兰吉亚等人。 2013]。 图 2 显示了栅极未对准的示例。 理想情况下,FinFET 的栅极预计位于源极和漏极之间的中心,如图 2(a) 所示。 然而,由于工艺变化,印刷栅极通常会出现错位,如图 2(b) 所示。 根据 Valin 等人的说法。 [2012],对于 10nm 工艺技术,到源极侧或漏极侧的未对准距离可高达 5nm。 萨兰吉亚等人。 [2013] 报道说,FinFET 的阈值电压 Vth 对源极侧未对准比对漏极侧未对准更敏感。 在最坏的情况下,当栅极与 FinFET 的漏极错位 5nm 时,Vth 会增加 0.01V。 另一方面,当栅极与 FinFET 的源极侧错位 5nm 时,Vth 增加了 0.05V。 在电源电压为 1V 的情况下,该增量可以显着降低 FinFET 的漏极电流 40%。

由于大多数模拟构建模块(例如电流镜和差分对)都需要高度匹配的漏极电流,因此由于栅极未对准而导致的任何电流变化都可能破坏电流比匹配并降低电路性能。 因此,在这些构建块的布局设计过程中,必须考虑栅极错位的存在。 需要注意的是,在IC制造过程中,同一芯片上不同FinFET的栅极错位方向和距离通常是相同的。 设计人员需要做的是仔细安排电流镜或差分对中所有 FinFET 的方向,以使电流镜或差分对中不同晶体管之间的漏极电流比可以完美匹配 [Fulde et al. 2007]。

1.2. 寄生电阻导致的电流失配

除了栅极错位之外,基于 FinFET 技术,互连线的寄生电阻变得不可忽略 [Subramanian et al. 2006]。 它逐渐主导电路设计的性能、信号完整性和可靠性 [Baldi 等人。 2001]。 如果不仔细考虑模拟 IC 布局中的寄生电阻,晶体管的漏极电流可能会发生巨大变化。 如第 1.1 节所述,大多数模拟构建块,例如电流镜和差分对,对电流变化或电流失配非常敏感; 由于寄生电阻引起的任何电流变化也会破坏电流比匹配并降低电路性能。 因此,在对这些积木进行布局设计时,也需要考虑布线引起的寄生电阻的存在。

如图 3(a) 所示,具有一个参考晶体管 tRef 和 k 个缩放晶体管 t1, t2,…, tk 的电流镜将产生一组恒定的复制电流 I1, I2,… ., Ik, 流过 t1, t2,…, tk,不管其负载如何,通过复制流过 tRef 的参考电流 IRef。 如果按比例缩放的晶体管的尺寸或沟道宽度 ti 是 tRef 的 n 倍,则 Ii 相对于 IRef 被缩放 n 倍。 为了减少由于工艺变化引起的晶体管失配,每个晶体管被分解成几个单元晶体管,如图3(b)所示。 然后将单元晶体管相对于公共中心点对称放置,如图 3© 所示。

在图3 (a) 中,由于电流镜中不同晶体管的源极端子完全连接,因此连接不同晶体管的源极端子的布线足够短;因此,相应的寄生电阻是可忽略的。然而,当产生具有共同质心约束的大量单元晶体管的布局时,属于同一晶体管ti的一些单元晶体管可以彼此远离放置。存在不可忽略的寄生电阻Rutj,其对应于连接单元晶体管的漏极端子utj和其它单元晶体管的漏极端子的布线,如图3 (b) 所示。因此,在共心FinFET布局和布线期间匹配互连电缆长度对于更好的电流比匹配至关重要,从而减少由于寄生电阻的存在而导致的电流失配。

调研

为了在电流镜或差分对中生成匹配的晶体管布局,之前的所有工作 [Ma et al. 2011; 林等人。 2011; 肖和年轻 2009; 林等人。 2009、2007; 龙等人。 2005;马等。 2007; 严等人。 2006; 张等人。 2010] 提出了平面 MOSFET 的各种共质心布局和布线方法,同时考虑了重合性、对称性、分散性和紧凑性 [Hastings。 2006]。 之前的工作都没有考虑到由 FinFET 技术引起的栅极错位的影响以及在公共质心布局和布线过程中寄生电阻的匹配。 虽然 Long 等人。 [2005] 提到了共质心结构内晶体管的手性条件,这种手性条件无法达到与栅极失准影响匹配的最佳电流比。

其他近期作品 [Huang et al. 2013; 林等人。 2012b; 何等人。 2013; 李等人。 2014; 林等人。 2012a, 2013, 2014]专注于共质心电容布局布线的优化,但这些作品中的电容仍然与FinFET技术无关,也没有考虑到共质心布局布线过程中寄生电阻的影响。 因此,现有方法无法成功生成具有最佳电流比与存在栅极失准和寄生电阻匹配的共质心布局。

— 我们提出了第一个共质心 FinFET 布局和布线公式,该公式同时考虑了栅极未对准和寄生电阻的影响,以及所有传统的共质心规则,包括重合、对称、分散和紧凑性,用于下一代模拟设计 .

— 我们推导出一个新的质量指标来评估电流镜中晶体管之间的电流比匹配,以及共质心 FinFET 阵列中存在栅极未对准和寄生电阻。

— 基于导出的质量指标和空间相关模型,我们提出了新颖的寄生感知 FinFET 布局和布线算法,以优化电流比匹配,同时最大化共质心 FinFET 阵列的分散度。

——我们的实验结果表明,在存在栅极错位和寄生电阻的情况下,所提出的方法可以在电流镜中的晶体管之间实现更好的电流比匹配,同时保持较高的色散度。

数据集

我们在配备 Intel Core i7-2600 3.4GHz CPU 和 16GB 内存的个人计算机上使用 MATLAB 编程语言实现了建议的共质心 FinFET 放置方法。 我们创建了一组电流镜测试用例,CM1、CM2、…、CM8,具有不同的晶体管宽度比,如表 III 的第二列所示。 为了证明我们的方法的有效性,我们进行了两组实验:(1)将不同的布局方法与我们的寄生感知布线方法一起应用,以及(2)将我们的寄生感知布局与寄生不感知和寄生感知布线方法一起应用 .

实验指标

具体方法

使用空间相关模型评估离散度

在生成电流镜的公共质心位置时,有必要优化参考晶体管和所有其他缩放晶体管之间的匹配质量,以获得准确的缩放因子。 根据林等人的说法。 [2012b],由于工艺变化而发生的晶体管失配可分为两类:系统失配和随机失配。 为了减少系统失配,每个晶体管被分解成几个单元晶体管,这些单元晶体管相对于一个公共中心点对称放置,如图 3© 所示。 另一方面,随机失配主要与加工条件或材料特性的统计波动有关。 由于这些波动是随机机制,每个晶体管的所有单位晶体管应均匀分布在整个公共质心位置,以表现出最高程度的分散 [Razavi 2000]。 罗等人。 [2008] 提出了一个空间相关模型来测量公共质心放置的整体相关系数或分散度 ρ。 对于 n 个晶体管,ρ 等于一对晶体管的所有相关系数的总和,其定义在等式 (1) 中。

栅极失调和寄生电阻导致的电流失配

如第 1 节所述,基于 FinFET 技术的栅极错位和寄生电阻问题可能会对电流镜中不同晶体管的漏极电流产生很大影响。 除了基于空间相关模型评估共质心布局的分散度外,还需要研究如何评估存在栅极失准和寄生电阻的漏极电流匹配质量。 在第 3.1 节中,我们首先推导了用于评估共质心 FinFET 阵列中电流镜的电流失配的质量指标,其中存在栅极失准和寄生电阻。 在第 3.2 节中,我们提出了一个案例研究,以说明确定每个晶体管的方向并考虑在共质心 FinFET 布局和布线期间的寄生电阻匹配以最大限度地减少栅极失准和寄生电阻的影响的重要性。

电流失配评估

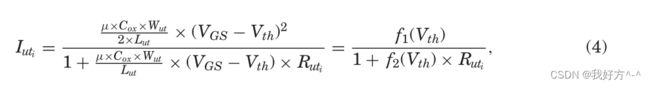

要将参考电流复制到其他缩放晶体管,缩放晶体管必须在饱和区运行 [Razavi 2000]。 根据 Subramanian 等人的说法。 [2006],在漏极端子存在寄生电阻的饱和区域中,单位晶体管的漏极电流uti由公式(4)定义。

R u t i R_{ut_i} Ruti表示对应于连接uti的漏极端子和属于同一晶体管的其他单元晶体管的漏极端子的导线的寄生电阻。 我们采用 1V 电源电压的 10nm FinFET 技术。 表 I 中列出的工艺参数可以从 ITRS [2012] 和 Liu 等人获得。 [1998]。

由于栅极未对准的影响可能会增加晶体管的 Vth,因此 Iuti 可以写成 Vth 的函数。 考虑到栅极错位,漏极侧错位的单元晶体管的阈值电压记为Vd th,源极侧错位的单元晶体管的阈值电压记为Vs th。 根据等式(4),如果晶体管 ti 包含具有漏极侧栅极失准的 nd 个单位晶体管和具有源极侧失准的 ns 个单位晶体管,其中 n = nd+ns,则漏极电流 Ii 存在 栅极失准和寄生电阻可以用公式 (5) 表示。

共质心FINFET布局和布线算法

基于等式(1)和(10)中色散度和电流失配的评估指标,我们提出了考虑栅极失准和寄生影响的优化共质心FinFET布局的生成 阻力,同时最大限度地分散程度。 我们的方法从确定单元晶体管的方向开始,同时最大限度地减少由栅极失准导致的电流失配(第 4.1 节)。 基于确定的单元晶体管的方向,我们通过最大化同一行中单元晶体管之间的扩散共享和分散度,同时限制布局范围(第 4.2 节),从而产生一个初始的共质心 FinFET 布局,使得由于寄生电阻的影响减小。 一旦获得了每一行的布局,我们通过最大化不同行中单元晶体管之间的分散度来进一步细化布局(第 4.3 节)。 最后,我们执行寄生感知路由以生成每个网络的路由拓扑,同时改善不同晶体管之间的电流比匹配(第 4.4 节)。

4.1。确定单元晶体管的方向

为了减少由于栅极未对准引起的电流失配,必须正确确定单元晶体管的方向。我们将问题表述为在无向图中找到最小权重集团 Minimum Weight Clique [Cormen等人2001],以同时确定单元晶体管的方向。图中的每个顶点表示晶体管ti的单元晶体管取向的一种配置,该晶体管ti分别具有具有源极侧未对准的ns i单元晶体管和具有漏极侧未对准的nd i单元晶体管。如果两个顶点对应于两个不同的晶体管ti和tj,则在两个顶点之间存在一条边。可以通过等式 (9) 计算的边缘权重gi_j表示基于由顶点表示的单位晶体管取向的配置,ti和tj之间的电流失配。

求解图中的最小权重团问题称为 NP 完全问题。 我们使用分支定界算法应用启发式[¨Osterg˚ard 2001]。 我们列举了图中每个晶体管的单位晶体管方向的所有可能配置(即,k 指 FinFET 具有 k+1 配置,其方向是源极侧未对准和漏极侧未对准的组合)。 图 5 显示了具有三个晶体管 A、B 和 C 的电流镜的最小权重团公式,其中每个晶体管分别具有 2、2 和 3 种可能的单位晶体管方向配置。 通过在无向图中找到最小权重团,可以确定每个晶体管的单元晶体管方向的最佳配置,从而可以实现由于栅极失准 G 引起的最小电流失配。

4.2. 考虑寄生电阻和色散的共质心 FinFET 放置算法

给定确定的单元晶体管的方向,我们希望生成 Nr 行和 Nc 列的共质心 FinFET 布局,同时保持单元晶体管的方向,最大限度地减少由于寄生电阻引起的电流不匹配 ,并最大化分散度。 由于所有单元晶体管的方向都已确定,因此共质心 FinFET 阵列的电流失配由 P 决定。我们需要找到最佳布局,从而在布线后产生匹配的寄生电阻。

为了实现这一目标,我们介绍每个晶体管的位置范围约束限制的放置区域对应的单元晶体管在一个允许距离,定义如下:

定义1.晶体管的布局范围约束,ti,isa2-tuple组合,记为{Di C, Di R},将ti的单位晶体管的位置限制在Di C (Di R)in x的距离内 - 方向(y 方向)从 Nr 行和 Nc 列单元晶体管阵列的中心。

值得跟进

- 电流比匹配和电流镜匹配?Current-ratio match. & Current mirror.

- 电流匹配 和 电流失配的计算 即 电流失配评估

- 如何确定电流方向?

- 实验评估方法