【FPGA】Verilog:组合电路 | 3—8译码器 | 编码器 | 74LS148

前言:本章内容主要是演示Vivado下利用Verilog语言进行电路设计、仿真、综合和下载

示例:编码/译码器的应用

- 功能特性: 采用 Xilinx Artix-7 XC7A35T芯片

- 配置方式:USB-JTAG/SPI Flash

- 高达100MHz 的内部时钟速度

- 存储器:2Mbit SRAM N25Q064A SPI Flash(样图旧款为N25Q032A)

- 通用IO:Switch :x8LED:x16Button:x5DIP:x8 通用扩展IO:32pin

- 音视频/显示: 7段数码管:x8 VGA视频输出接口 Audio音频接口

- 通信接口:UART:USB转UART Bluetooth:蓝牙模块

- 模拟接口: DAC:8-bit分辨率 XADC:2路12bit 1Msps ADC

目录

Ⅰ. 前置知识

0x00 3-8译码器74LS138的工作原理

0x01 优先编码器74148的工作原理

Ⅱ. Verilog实现

0x00 优先编码器74LS148

0x01 3—8译码器

0x02 结果数据

Ⅰ. 前置知识

0x00 3-8译码器74LS138的工作原理

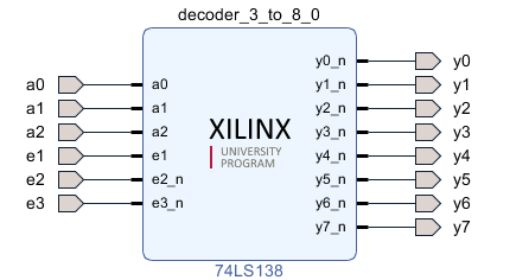

利用Vivado提供的IP包(如下图所示)

也可直接(见下列代码)搭建74LS138功能验证电路。

(1)当选通端e1为高电平,另两个选通端e2和e3为低电平时,芯片使能。将地址端(a2、a1、a0)的二进制编码在y0至y7对应的输出端以低电平译出。比如:a2a1a0=110时,则y6输出低电平信号。

(2)利用 e1、e2和e3可方便的级联扩展成16线译码器、32线译码器。

(3)若将选通端中的一个作为数据输入端时,74LS138还可用作数据分配器

测试74LS138逻辑关系接线图

用verilog编程实现译码功能,参考代码如下。参考程序中使能信号需要自行补全。

module converter(DB,SEG);

input[2:0] DB;

output[7:0] SEG;

reg[7:0] SEG;

always @(DB)

begin

case(DB)

4'b0000: SEG<=8'b11111110;

4'b0001: SEG<=8’b11111101;

4'b0010: SEG<=8’b11111011;

4'b0011: SEG<=8’b11110111;

4'b0100: SEG<=8’b11101111;

4'b0101: SEG<=8’b11011111;

4'b0110: SEG<=8’b10111111;

4'b0111: SEG<=8’b01111111;

default: SEG<=8'b11111111;

endcase

end

endmodule 0x01 优先编码器74148的工作原理

在优先编码器电路中,允许同时输入两个以上编码信号。

不过在设计优先编码器时,已经将所有的输入信号按优先顺序排了队。在同时存在两个或两个以上输入信号时,优先编码器只按优先级高的输入信号编码,优先级低的信号则不起作用。

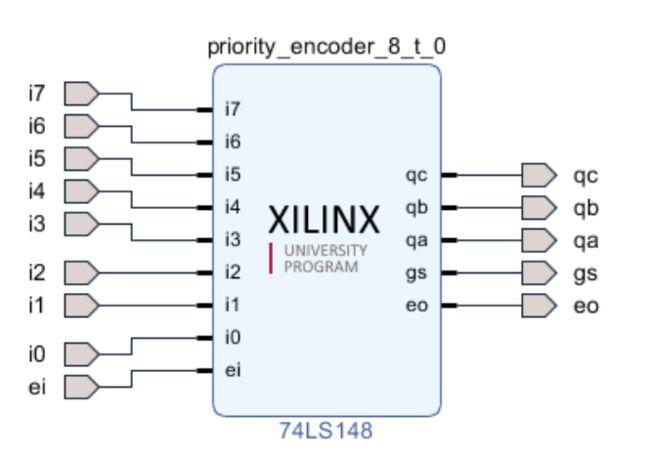

74148是一个8-3线优先级编码器。74148优先编码器为16脚的集成芯片,除电源脚 VCC(16)和GND(8)外,其余输入、输出脚的作用和脚号如图中所标。

其中 i0~i7为输入信号(i7优先权最高),qc、qb、qa为三位二进制编码输出信号,ei是使能输入端,eo使能输出端,gs为片优先编码输出端。

电路接线如下图所示:

编码器接线

用verilog编程实现优先编码功能,参考代码如下:

module encoder_83 (din, EI, GS, EO, dout);

input [7:0] din; //编码输入端data_in,低电平有效

input EI; //使能输入端EI(选通输入端),EI为 0 时芯片工作,即允许编码

output [2:0] dout; //编码输出端data_out

output GS; //片优先编码输出端,优先编码器工作工作状态标志GS,低电平有效

output EO; //使能输出端EO(选通输出端)

reg [2:0] dout;

reg GS, EO;

always @(din or EI)

if(EI) begin dout <= 3'b111; GS <= 1; EO <= 1; end //所有输出端被锁存在高电平

else if (din[7] == 0) begin dout <= 3'b000; GS <= 0; EO <= 1; end

else if (din[6] == 0) begin dout <= 3'b001; GS <= 0; EO <= 1; end

else if (din[5] == 0) begin dout <= 3'b010; GS <= 0; EO <= 1; end

else if (din[4] == 0) begin dout <= 3'b011; GS <= 0; EO <= 1; end

else if (din[3] == 0) begin dout <= 3'b100; GS <= 0; EO <= 1; end

else if (din[2] == 0) begin dout <= 3'b101; GS <= 0; EO <= 1; end

else if (din[1] == 0) begin dout <= 3'b110; GS <= 0; EO <= 1; end

else if (din[0] == 0) begin dout <= 3'b111; GS <= 0; EO <= 1; end

else if (din == 8'b11111111) begin dout <= 3'b111; GS <= 1; EO <= 0; end //芯片工作,但无编码输入

else begin dout <= 3'b111; GS <= 1; EO <= 1; end //消除锁存器(latch)

endmodule

//EI = 0 表示允许编码,否则所有输出端被封锁在高电平(控制芯片工作)

//EO = 0 表示电路工作,但无编码输入(用于级联)

//GS = 0 表示电路工作,且有编码输入(判断输入端是否有输入)Ⅱ. Verilog实现

0x00 优先编码器74LS148

设计代码:

module encoder1(n_EI,n_I,n_Y,n_CS,n_E0);

input n_EI;

input [7:0] n_I;

output [2:0] n_Y;

output n_CS,n_E0;

reg [2:0] n_Y;

reg n_CS,n_E0;

always @(n_EI or n_I)

if(n_EI==0)

if(n_I[7]==0){n_CS,n_E0,n_Y}=5'b0_1_000;

else if(n_I[6]==0){n_CS,n_E0,n_Y}=5'b0_1_001;

else if(n_I[5]==0){n_CS,n_E0,n_Y}=5'b0_1_010;

else if(n_I[4]==0){n_CS,n_E0,n_Y}=5'b0_1_011;

else if(n_I[3]==0){n_CS,n_E0,n_Y}=5'b0_1_100;

else if(n_I[2]==0){n_CS,n_E0,n_Y}=5'b0_1_101;

else if(n_I[1]==0){n_CS,n_E0,n_Y}=5'b0_1_110;

else if(n_I[0]==0){n_CS,n_E0,n_Y}=5'b0_1_111;

else{n_CS,n_E0,n_Y}=5'b1_0_111;

else{n_CS,n_E0,n_Y}=5'b1_1_111;

endmodule

仿真测试代码:

module sim_encoder1();

reg n_EI;

reg [7:0] n_I;

wire [2:0] n_Y;

wire n_CS,n_E0;

encoder1 test(.n_EI(n_EI),.n_I(n_I),.n_Y(n_Y),.n_CS(n_CS),.n_E0(n_E0));

always begin

n_EI=1'b0;n_I=8'b01111111;#100;

n_EI=1'b0;n_I=8'b10111111;#100;

n_EI=1'b0;n_I=8'b11011111;#100;

n_EI=1'b0;n_I=8'b11101111;#100;

n_EI=1'b0;n_I=8'b11110111;#100;

n_EI=1'b0;n_I=8'b11111011;#100;

n_EI=1'b0;n_I=8'b11111101;#100;

n_EI=1'b0;n_I=8'b11111110;#100;

end

endmodule

波形图:

0x01 3—8译码器

设计代码:

module encoder(B,SEG,en);

input[2:0] B;

input[2:0] en;

output[7:0] SEG;

reg[7:0] SEG;

always @(B or en)

if(en[2]&(~en[1])&(~en[0]))

case(B)

3'b000: SEG=8'b11111110;

3'b001: SEG=8'b11111101;

3'b010: SEG=8'b11111011;

3'b011: SEG=8'b11110111;

3'b100: SEG=8'b11101111;

3'b101: SEG=8'b11011111;

3'b110: SEG=8'b10111111;

3'b111: SEG=8'b01111111;

default: SEG=8'b11111111;

endcase

else SEG=8'b11111111;

endmodule

仿真测试代码:

module sim_encoder();

reg [2:0]B;

reg [2:0]en;

wire [7:0]SEG;

encoder test(.B(B),.SEG(SEG),.en(en));

always begin

en=3'b100;B=3'b000;#100;

en=3'b100;B=3'b001;#100;

en=3'b100;B=3'b010;#100;

en=3'b100;B=3'b011;#100;

en=3'b100;B=3'b100;#100;

en=3'b100;B=3'b101;#100;

en=3'b100;B=3'b110;#100;

en=3'b100;B=3'b111;#100;

end

endmodule波形图:

0x02 结果数据

74LS138功能表

| 输入 |

输出 |

||||||||||||

| 使能 |

选择 |

||||||||||||

| e1(G1) |

e2(G2B) |

e3(G2A) |

a2(C) |

a1(B) |

a0(A) |

y7 |

y6 |

y5 |

y4 |

y3 |

y2 |

y1 |

y0 |

| 0 |

× |

× |

× |

× |

× |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

| 1 |

× |

1 |

× |

× |

× |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

| 1 |

1 |

× |

× |

× |

× |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

| 1 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

| 1 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

| 1 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

| 1 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

| 1 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

| 1 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

| 1 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

| 1 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

优先编码器74LS148功能表

| 输入 |

输出 |

||||||||||||

| ei使能 |

i7 |

i6 |

i5 |

i4 |

i3 |

i2 |

i1 |

i0 |

qc |

qb |

qa |

eo 选通 |

gs 扩展 |

| 1 |

× |

× |

× |

× |

× |

× |

× |

× |

1 |

1 |

1 |

1 |

1 |

| 0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

| 0 |

0 |

× |

× |

× |

× |

× |

× |

× |

0 |

0 |

0 |

1 |

0 |

| 0 |

1 |

0 |

× |

× |

× |

× |

× |

× |

0 |

0 |

1 |

1 |

0 |

| 0 |

1 |

1 |

0 |

× |

× |

× |

× |

× |

0 |

1 |

0 |

1 |

0 |

| 0 |

1 |

1 |

1 |

0 |

× |

× |

× |

× |

0 |

1 |

1 |

1 |

0 |

| 0 |

1 |

1 |

1 |

1 |

0 |

× |

× |

× |

1 |

0 |

0 |

1 |

0 |

| 0 |

1 |

1 |

1 |

1 |

1 |

0 |

× |

× |

1 |

0 |

1 |

1 |

0 |

| 0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

× |

1 |

1 |

0 |

1 |

0 |

| 0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

、