【正点原子FPGA连载】第七章程序固化实验摘自【正点原子】DFZU2EG_4EV MPSoC之嵌入式Vitis开发指南

第七章程序固化实验

在前面的几个实验中,我们都是通过JTAG接口将FPGA配置文件和应用程序下载到MPSOC器件中。接下来我们将尝试把程序存储在非易失性存储器中,在上电或者复位时让程序自动运行,这个过程需要启动引导程序(Boot Loader)的参与。Boot Loader会加载FPGA配置文件,以及运行在ARM中的软件应用。

本章包括以下几个部分:

77.1简介

7.2实验任务

7.3硬件设计

7.4软件设计

7.5下载验证

7.1简介

MPSOC的系统启动过程由平台管理单元(PMU)和配置安全单元(CSU)管理和执行。启动过程包括三个功能阶段:预配置阶段、配置阶段和后配置阶段。

预配置阶段由平台管理单元控制。平台管理单元运行PMU ROM代码以设置系统。PMU处理所有复位和唤醒过程。

在配置阶段,BootROM(CSU ROM代码的一部分)解释引导头以配置系统,并在安全或非安全引导模式下将处理系统(PS)的第一阶段引导加载程序(FSBL)代码加载到片上RAM(OCM)中。引导头定义了许多引导参数,包括安全模式和执行FSBL的处理器MPCore。在引导期间,CSU还将PMU用户固件(PMU FW)加载到PMU RAM中,以与PMU ROM一起提供平台管理服务。对于基于Xilinx的FSBL和系统软件,PMU FW必须存在于大多数系统中。

FSBL执行开始后,CSU ROM代码进入后配置阶段,该阶段负责系统干预响应。CSU硬件提供持续的硬件支持,以验证文件,通过PCAP配置PL,存储和管理安全密钥,解密文件。

启动流程(Boot Flow)

PMU执行许多强制性和可选的安全操作,包括:

1、可选功能:将低功耗域(LPD)寄存器归零。当LPD_SC eFUSEs编程时,PMU将LPD中所有寄存器归零。

2、可选功能:将全功率域(FPD)寄存器归零。当FPD_SC eFUSEs编程时,PMU将FPD中所有寄存器归零。

3、将PMU RAM归零:PMU RAM中写零并读回以确认写成功。

4、将PMU处理器的TLB内存归零。

5、电压检查:PMU检查LPD、AUX和专用IO的电源电压,以确认电压在规格范围内。

6、将内存归零:PMU将位于LPD、FPD和CSU中的内存归零。

一旦这些安全操作完成,PMU通过SHA-3/384引擎发送CSU不可变ROM代码,并将计算出的加密校验和与存储在设备中的黄金拷贝(golden copy)进行比较,如果校验和匹配,则验证CSU ROM完整性并释放对CSU的复位。

PMU负责处理主要的预引导任务和PS的管理,以确保系统资源的可靠通电断电。启动PMU的上电复位(POR)操作,直接或间接的释放了预期上电模块的复位。在这种情况下,PMU需要ROM代码来保持初始化上电顺序。即使在启动过程之后,PMU仍在运行,并且负责处理各种系统复位。在更改系统电源状态时也会使用它(例如上电、睡眠和唤醒)。

在初始化启动期间,POR将PMU从复位中释放,然后执行PMU ROM。下面描述了PMU处理器在POR复位后,通过运行PMU ROM预启动代码完成的操作序列:

1、初始化PS SYSMON和引导单元所需的PLL。

2、清除PMU RAM和CSU RAM(仅外部POR)。

3、验证PLL锁。

4、通过PS SYSMON单元验证LPD、AUX和IO电源范围。

5、清除低功耗和全功耗域。

6、如果前面的步骤没有错,PMU将释放CSU复位并进入PMU服务模式。如果有错,将产生一个启动错误标志。

当CSU 复位被释放,CSU将按照下面序列运行:

1、初始化OCM。

2、通过读取引导模式寄存器来确定启动模式。

3、CSU继续在OCM中加载FSBL,以供RPU或APU执行。然后,CSU将PMU用户固件加载到PMU RAM中,以供PMU固件执行。

启动模式(Boot Modes)

BootROM可以通过Quad-SPI,SD,eMMC,USB2.0控制器0或NAND等外部设备启动系统。

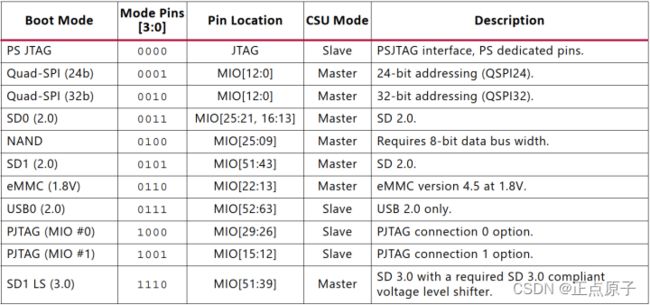

MPSOC使用多个模式引脚来决定配置器件的类型,软件的存储位置以及其他的系统设置,这些引脚共享PS端的MIO引脚。总共有7个模式引脚,分别为MIO[8:2]。其中,前四个引脚定义启动模式,第五个引脚定义是否使用PLL,第六个和第七个引脚定义上电过程中MIO bank0和bank1的bank电压。如下图所示:

图 7.1.1 启动模式引脚

整个系统的启动过程如下图所示:

图 7.1.2 MPSOC系统启动过程

7.2实验任务

本章的实验任务是在“AXI GPIO按键控制LED实验”的基础上创建FSBL,实现程序上电自启动,包括从SD卡启动,QSPI Flash和eMMC启动三种方式。

7.3硬件设计

本次实验在“AXI GPIO按键控制LED实验”的基础上进行。打开《AXI GPIO按键控制LED》实验的Vivado工程,另存为本次实验工程,工程名为axi_gpio_fsbl,具体过程参考前面的实验。

接下来对系统的硬件设计进行修改。在Vivado界面左侧选择Open Block Design,然后在右侧的Diagram界面中双击Zynq UltraScale+ MPSOC模块修改其配置。

首先使能QSPI外设。在左侧的导航栏中选择I/O Configuration,在打开的右侧页面中,依次展开Low Speed > Memory Interfaces,然后勾选QSPI并在后面的下拉菜单中选择Single,QSPI Data Mode选择x4,QSPI IO默认为MIO0…5,勾选Feedback Clk并选择MIO6,如下图所示。

图 7.3.1 使能QSPI Flash控制器

然后打开SD卡外设。在上一步的页面中,展开SD外设,勾选SD1,在后面的菜单栏中选择MIO46…51,Slot Type选择SD2.0,Data Transfer Mode选择4Bit,勾选CD用于检测SD卡插入并选择MIO45,如下图所示:

图 7.3.2 使能SD卡控制器

最后打开eMMC外设。在同样的页面中,勾选SD0并选择MIO13…22,Slot Type设置成eMMC,Data Transfer Mode选择8bit,勾选Reset并选择MIO23,如下图所示:

图7.3.3 使能eMMC控制器

上面两幅图中具体每个外设所连接的MIO引脚可以通过查看开发板原理图得知,设置完成后点击“OK”。然后在Diagram窗口空白处右击,然后选择“Validate Design”验证设计。验证完成后弹出对话框提示“Validation Successful”表明设计无误,点击“OK”确认。最后按快捷键“Ctrl + S”保存设计。

接下来在Source窗口中右键点击Block Design设计文件“design_1.bd”,执行“Generate Output Products”。最后在左侧Flow Navigator导航栏中找到PROGRAM AND DEBUG,点击该选项中的“Generate Bitstream”,对设计进行综合、实现、并生成Bitstream文件。

在菜单栏中选择 File > Export > Export hardware导出硬件,并在弹出的对话框中,勾选“Include bitstream”。

新建vitis文件夹,将生成的xsa文件放入其中。

然后在菜单栏选择Tools > Launch Vitis,启动Vitis开发环境。在弹出的对话框中,将路径指定到新建的vitis文件夹下,点击Launch启动Vitis。

到这里我们的硬件设计部分已经结束,接下来的软件设计部分需要在Vitis软件中进行。

7.4软件设计

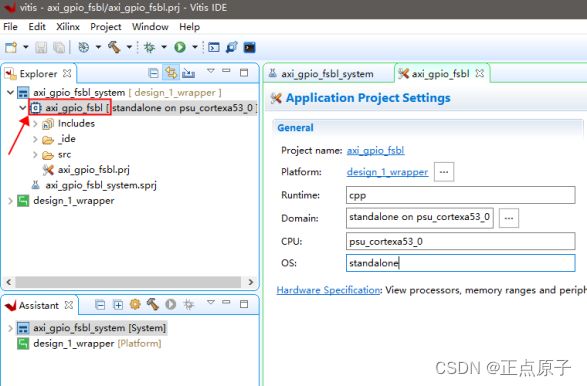

新建工程。参考前面实验的步骤,新建一个名为axi_gpio_fsbl的应用工程,如下图所示:

图 7.4.1 新建应用工程

新建源文件。在axi_gpio_fsbl/src目录上右击,新建一个名为main.c的源文件,然后把《AXI GPIO按键控制LED》实验中main.c的代码拷贝到本实验的main.c中,如图7.4.2所示,按“Ctrl+S”保存,然后编译工程。

图7.4.2 将代码拷贝到main.c中

创建启动镜像。选中应用工程,右键选择Create Boot Image,如图7.4.3所示。接下来,在弹出的界面中添加生成boot.bin所需的文件,然后点击“Create Image”,如图7.4.4所示。

图7.4.4 添加文件生成Boot.bin

从上图中可以看到,软件已经给我们自动添加所需的文件。首先是Bootloader启动文件,也就是序号4处的fsbl.elf。其次是FPGA的配置文件design_1_wrapper.bit,在上图中序号5处。最后是应用程序axi_gpio_fsbl.elf文件,上图中序号6处。注意这三个文件的顺序不能错。

图7.4.4中,序号2处的bif文件是生成BOOT的配置文件,序号3处的BOOT.bin就是我们需要的启动文件,可以烧录到QSPI Flash或eMMC中,也可以放到SD中来启动ZYNQ MOPSOC。

创建完成后,在指定的路径下可以看到生成的两个文件,如下图所示:

图7.4.5 生成的BOOT.bin文件

到这里,我们创建启动镜像文件的过程就结束了。

7.5下载验证

我们首先来验证如何从SD卡中启动程序。将Micro SD卡插入读卡器,然后在电脑上将其格式化为FAT32格式,如下图所示:

图 7.5.1 格式化SD卡

然后将生成的BOOT.bin文件拷贝到SD卡根目录下,最后将SD卡从读卡器中取出,并插入开发板背面的Micro SD卡的卡槽中。

接下来将开发板上的启动模式开关设置为ON _OFF_ON_OFF,即设置为从SD卡启动(也就是开发板上丝印标注的0101 SD1)。不同的启动方式与四个拨码开关的状态对应关系如下图所示,其中0代表ON,1代表OFF。

图 7.5.2 启动模式设置

最后连接开发板的电源线,给开发板上电。

上电后,开发板上PL配置完成的绿色指示灯点亮。然后每次按下PL_KEY1,可以改变PS_LED1灯的显示状态,说明程序能够实现从SD卡中自启动。开发板实物如下图所示:

图 7.5.3 SD卡启动

SD卡启动验证完成后拔下Micro SD卡。接下来我们来介绍如何将程序固化到QSPI Flash中。

将程序固化到QSPI Flash需要使用JTAG下载器。首先我们将下载器与开发板上的JTAG接口连接,下载器另外一端与电脑连接。接下来将开发板上的启动模式开关设置为ON_ON_ON_ON,即设置为JTAG模式(也就是开发板上丝印标注的0000 JTAG)。最后连接开发板的电源,给开发板上电。

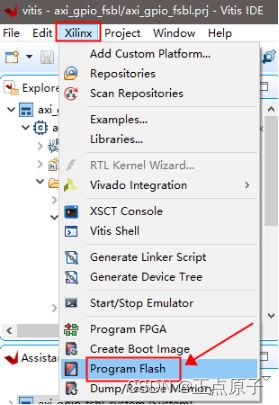

在Vitis软件的菜单栏中点击“Xilinx->Program Flash”,如下图所示:

图 7.5.4 打开Program Flash

在弹出的对话框中指定前面所生成的镜像文件BOOT.bin以及FSBL.elf文件,如下图中1和2处所示。Flash Type选择qspi-x4-single,并勾选Verify after flash,如下图中3和4处所示。

图 7.5.5 Program Flash 界面

在图 7.5.5中点击“Program”,开始对Flash进行编程,这个过程需要花费一段时间。

FLASH编程结束后,控制台提示信息如下图所示:

图 7.5.6 QSPI Flash下载成功

接下来断开开发板电源,然后将开发板上的启动模式开关设置为ON_ON_OFF_ON,即设置为32bit QSPI Flash启动(也就是开发板上丝印标注的0010 SPI_32),然后再次连接电源。

连接电源后,开发板上PL配置完成的指示灯点亮。然后每次按下开发板上PL_KEY0,可以改变PS_LED1的显示状态,说明程序能够实现从QSPI Flash中自启动。实物图如下所示:

图 7.5.7 QSPI Flash启动

最后我们来介绍如何将程序固化到eMMC中。

将程序固化到eMMC需要使用JTAG下载器。首先我们将下载器与开发板上的JTAG接口连接,下载器另外一端与电脑连接。接下来将开发板上的启动模式开关设置为ON_ON_ON_ON(也就是开发板上丝印标注的0000 JTAG),即设置为JTAG模式。最后连接开发板的电源,给开发板上电。

在Vitis软件的菜单栏中点击“Xilinx->Program Flash”,这一步和固化到Flash是一样的。

在弹出的对话框中指定前面所生成的镜像文件BOOT.bin以及FSBL.elf文件。Flash Type选择emmc,并勾选Verify after flash,然后点击Program,如下图所示。

图7.5.8 编程eMMC界面

eMMC编程结束后,控制台提示信息如下图所示:

图7.5.9 eMMC下载成功

接下来断开开发板电源,然后将开发板上的启动模式开关设置为ON_OFF_OFF_ON,即设置为eMMC启动(也就是开发板上丝印标注的0110 eMMC),然后再次连接电源。

连接电源后,开发板上PL配置完成的指示灯点亮。然后每次按下开发板上PL_KEY0,可以改变PS_LED1的显示状态,说明程序能够实现从eMMC中自启动。实物图如下所示:

图7.5.10 eMMC启动