【低功耗】CMOS基础,功耗分类,低功耗方法

学习资料

百度网盘 密码:csdn

学习路线,以Synopsys Flow举例:

中文文档,建立低功耗相关概念

IEEE Std 1801™ UPF3.0协议,根据标准协议查缺补漏。EDA工具还没有完全支持。

Low Power Methodology Manual, Synopsys 和 ARM 的低功耗设计书籍

Multivoltage Flow User Guide, Synopsys的低功耗(多电压)设计验证flow,从前端到后端涉及的工具

VCS Native Low Power (NLP) User Guide,带UPF的VCS仿真,含UPF协议的精简内容。

Verdi® Power-Aware Debug User Guide, Verdi对低功耗仿真debug的支持

电路基础

NMOS:P型衬底,高压导通,载流子为电子;传输低电平时,电流从D端到S端。

PMOS:N型衬底,低压导通,载流子为空穴;传输高电平时,电流从S端到D端。

在MOS中,源为提供载流子的端,而漏为接收载流子的端。NMOS中导电的载流子是电子,因此接到电路的最低电位以提供电子的是源极;而PMOS中导电的载流子是空穴,因此接到电路最高电位以提供空穴的是源极。电子的迁移速率高于空穴,所以 P 管的宽长比要比 N 管的宽长比大。如下图所示:

一般将MOS的衬底B与源S连接到一起,使其电位相等。

NMOS一般用于传输低电平,传输高电平时,有阈值损。

PMOS一般用于传输高电平,传输低电平时,有阈值损。CMOS基础

由NMOS,PMOS并联组成complementary互补型CMOS传输门没有阈值损。

NMOS, PMOS的S端,D端在同一侧,C与C'互为相反电压。C=1, C'=0时导通,双向流通,vi=vo。

双向开关tran,tranif0,tranif1。

常见的inverter反相器单元,也就是NOT非门,由NMOS,PMOS串联互补组成,NMOS下拉sink current灌电流负责传输低电平,PMOS上拉sourcing current拉电流负责传输高电平。

驱动能力:一般可以理解为在不显著影响电路性能的情况下能带的最大负载,传输高电平时提供拉电流的能力,传输低电平时灌电流的能力。

负载有阻性负载和容性(感性)负载,依据不同的电路有不同的需求。

带电容一般有两个要求:slew rate和系统的相位裕度;带电阻一般指的是较强的电流供给能力。

对于电阻:

驱动cell自身电阻越小,驱动能力越大。沟道宽度越大的cell(相应的面积也越大),其等效的电阻R越小(电阻R代表着PMOS导通,或者NMOS导通时的等效电阻),相应的驱动能力越大。因为在下级电路电压固定的情况下,内阻R越小,可以提供的电流越大。

负载cell的电阻越小,意味着驱动cell的负载越重。因为负载cell电阻越小,则电流越大,此时驱动cell内阻上的压降也越大,分摊到负载cell上的电压越小,导致负载cell无法维持高电平,以致出现逻辑混乱,不能实现预期的效果。

高阻态:

高阻态Z,也就是线网net float悬空时,对GND或者VCC的电阻R都很大,外面任何弱驱动都能改变该点的电位。同理,高阻态也是没有任何驱动能力的。一般对于I/O PAD,需要pulldown,pullup做上下拉处理。pulldown低电平,pullup高电平。上拉下拉可以通过加入上拉电阻,下拉电阻实现,采用大电阻,一方面功耗消耗低,另一方面驱动能力弱,但是足以将信号线强制箝位至某个电平,以防止信号线因悬空而出现不确定的状态。上拉(Pull Up )或下拉(Pull Down)电阻详解

对于电容:

MOS管的输入端口存在寄生电容,要驱动MOS必须在它的开启(关断)的时候提供瞬时大电流推拉,控制电容快速充放电,保证满足时序要求的transition。此时驱动能力也可以指Fanout扇出能力。常见的CLK时钟驱动多个DFF。

增加驱动能力

插入buffer增加驱动能力。buffer由两级inverter组成,第一级P/N MOS管的沟道宽度小,电阻大,容易被驱动;第二级P/N MOS管的沟道宽度大,电阻小,驱动能力强。为什么插入buffer能够增加驱动能力?

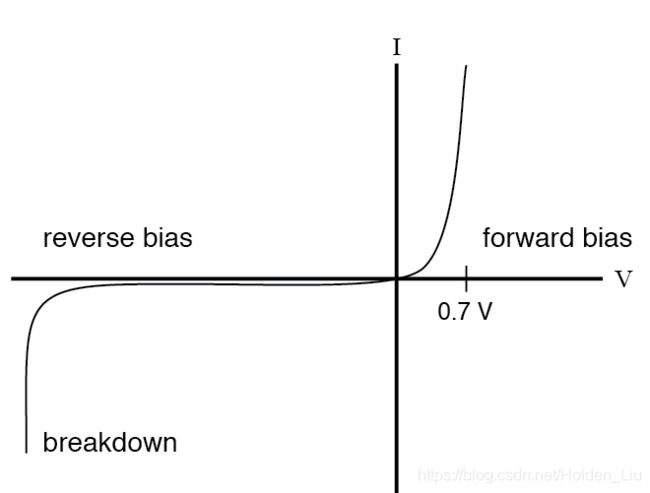

PN结

实际CMOS电路在P-diffusion&N-well,N-diffusion&P-well间存在P-N节。

反向偏置时,存在漏电流。

在Body Bias时,N-well和P-diffustion来自不同power rail,应先对N-well PIN上电/下电,再对P-diffustion PIN上电/下电,避免产生正向偏置。

VDD与VCC

VCC: C=circuit 表示电路的意思, 即接入电路的电压

VDD: D=device 表示器件的意思, 即器件内部的工作电压

对于数字电路来说,VCC是电路的供电电压, VDD是芯片的工作电压。有的器件既有VDD引脚又有VCC引脚,说明这种器件自身带有电压转换功能,此时VCC=模拟电源,VDD=数字电源。

在场效应管(或COMS器件)中,VDD为漏极,VSS为源极,VDD和VSS指的是元件引脚,而不表示供电电压。

Vcc 来源于集电极电源电压, Collector Voltage, 一般用于双极型晶体管。

Vdd 来源于漏极电源电压, Drain Voltage, 用于 MOS 晶体管电路。

标准单元参数特性

不同逻辑单元库对应不同PVT条件或者工艺角,standard cell一般加上编译指令 `celldefine, `endcelldefine定义为cell modules。

Input Pin Capacitance: cell的输入电容负载,充放电的能力。

Pin-to-Pin Delays: 0→1,1→0电平转换时,Pin-to-Pin传播路径的延迟。

Dynamic power dissipation: cell的动态功耗。不同电平转换时Pin-to-Pin的功耗。

Static Power: cell的静态功耗。

Timing Constraints: 时序约束,如setup,hold,MPW(min pulse width),recovery,removal。

功耗分类

Dynamic Power

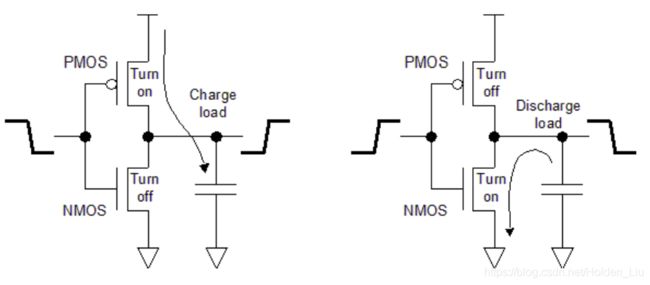

dynamic power包括switching power和internal power。

switching power来在MOS管的ON/OFF切换,和供电电压,负载等效电容,翻转率

有关。

PMOS打开,传输高电平,拉电流,负载charge充电。

NMOS打开,传输低电平,灌电流,负载discharge放电。

internal power:当inverter的input处于中间电位时,PMOS和NMOS同时导通,VDD与VSS间存在短路电流。低阈值器件更容易发生短路功耗。深入理解Internal Power

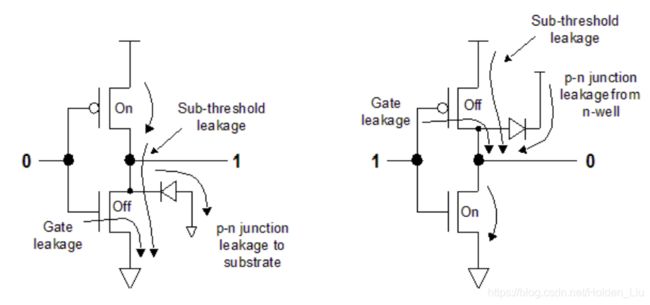

Static(Leakage) Power

随着工艺节点的缩小和阈值电压的降低,leakage power的问题越来越凸显。

Sub-threshold leakage: 晶体管逻辑关断时,但沟道并没完全截止。提高Vt可以降低,但会导致器件翻转速度就降低。

Reverse-biased p-n diode leakage:反向偏置P-N结,存在于NMOS的漏端N-diffusion(高电平)和P-well(低电平)之间,PMOS的漏端P-diffusion(低电平)和N-well(高电平)之间。损耗很小。

Gate leakage:由于热载流子注入和电子隧穿效应,在栅极和源端/漏端间存在漏电流。

VCD FSDB格式的波形文件中包含确切的信号翻转和占空比数据,根据std cell中的功耗数据和电源网络的IR-drop,通过专门工具,如Synopsys PrimeTime PX,Cadence Voltus,进行功耗评估。

降低功耗的方法

Clock Gating: 减少不必要的时钟反转,简单有效地降低动态功耗。

Multiple-Vt Library Cells :多阈值cell;对翻转频率要求不高的路径,采用高Vt cell,降低漏电流。如果速度要求很高,这个方法是不可行的。

Multivoltage Design: 多电压域,对速度要求高的部分,如CPU/RAM,采用高供电电压。速度要求低的部分,如外设,采用低供电电压。对于跨不同电压的信号需要插入Level-Shifer Cells。

Power Switching:电源关断,通过PMU模块控制Power-Switch Cells或者模拟部分的LDO, DC-DC,关断不工作的电源域。需要Isolation cells做钳位处理,以免下电区的输出影响上电区。插入Retention Register Cells保存下电前的数据,供再次上电使用。也可以采用

Dynamic Voltage and Frequency Scaling:动态电压频率调节,根据工作条件,动态调节芯片的电压和频率。

Body Bias:一般衬底BULK的电压和源端电压相同。可以单独调节背偏压,对衬底节点施加反向偏压来增加阈值电压,从而减少漏电。

Low Power Cells

Clock-Gating cell

ICG(Integrated clock gating cell) , 由一个latch(低电平有效)和一个与门(gating cell,也可以是或门)组成,glitch free。

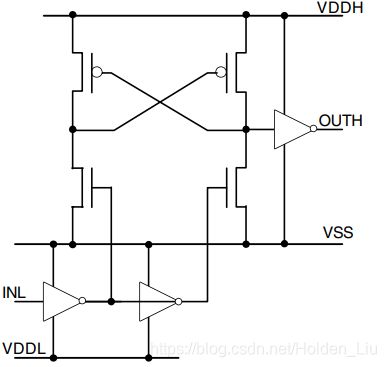

Level-Shifter Cell

High to Low Voltage Translation:由两个inverter串联而成,VDD来自低电压域。仅引入一个buffer的延迟,对时序的影响较小。

Low-to-High Voltage Translation:用低电压区域的信号invert和buffer之后得到的一对信号来驱动工作在高电压区域的交叉耦合晶体管结构。有明显的延迟。

Isolation Cell

X是输出信号,ISOLN和ISOL分别是开关控制信号。使用AND门钳位到0,OR门钳位到1。

Power-Switch Cells

MTCMOS分为两种,一种通过PMONS开关VDD,一种通过NMOS开关VSS。

MTCMOS不同于强电电路中的接触开关来实现连接和断开,而是通过CMOS电路构造来实现的。一个MOS管所能通过的电流极其有限,而当需要关断一个或者多个模块的时候,需要大量cell协同工作。

通过power ctrl信号将各个MTCMOS连接起来,形成一条daisy chain菊花链,减少in-rush current浪涌电流的影响。

数字电路外,采用LDO或者DC-DC作为电源开关。

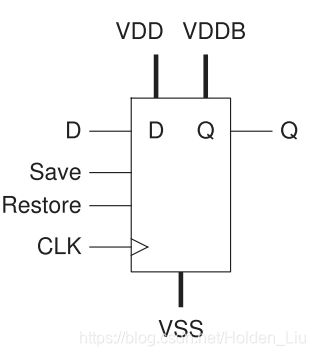

Retention Register Cells

下电前,控制Save信号采样,将数据锁存到寄存器;上电后,控制Restore信号读出下电前锁存的数据。

Memory Power Gating

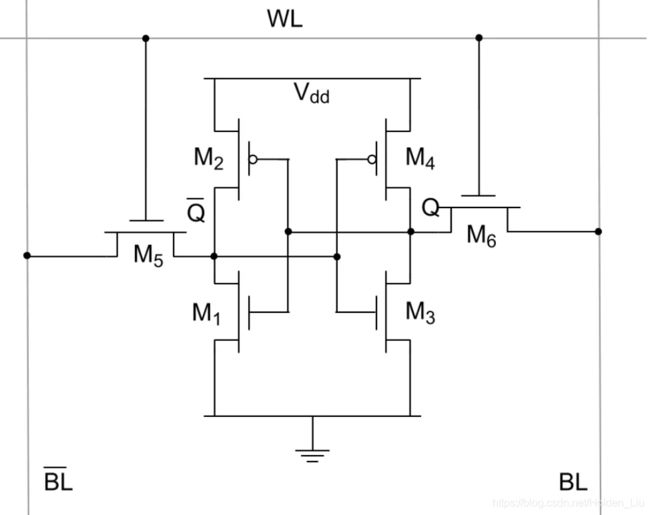

6T SRAM由6个管子组成,inverter1(M1与M2)和inverter2(M3与M4)交叉耦合,锁存住存储的电平信号。

Standby

Word Line没有被选中,M5,M6截断,数据保持不变。

Reading

先将BL和BL'拉到等电位,这个电位通常为pre-charge voltage电压,一般为VDD(或VDD-Vth),当BL及BL' 两端电位相等之后可以将之浮接(floating)或通过阻抗接至pre-charge voltage电压源,然后将WL打开,利用Q及Q' 的寄生电容通过M6、M5与BL、BL' 产生charge sharing及分压的效果从而让BL与BL' 产生电压差,最后利用外部的sense amplifier将差异信号放大从而读出0或1。

Writing

当bit-cell存储的内容为1而要写入0,即Q的电压值为VDD,此时只需要将WL电压值提高到VDD且BL为0,那么Q电压值将通过M6被拉低,Q' 的电压值将通过M5被拉高,再由M1/M2,M3/M4两个反相器推挽,bit-cell存储的内容就从1变成0了。此时WL电压拉低即可完成数据锁存。 SRAM工作原理

以ARM 40nm RAM为例:

RET1N:控制power mode,低有效。

VDDCE: mem core供电

VDDPE: mem外围逻辑供电

Standy mode: chip enable CEN=1, test chip enable TCEN=1

Normal mode: RET1N=1

Selective Bit Line Precharge mode:

RET1N=0,WL=0,VDDPE VDDCE保持不变,此时BL悬空减少漏电。

Retention mode:

RET1N=0,WL=0,VDDPE下电,VDDCE可以降低到只能维持存储器的内容不至于丢失的程度。BL悬空减少漏电。

Selective Bit Line Precharge mode和Retention mode不同之处在于,Selective Precharge可以快速进入工作状态,而 Retention需要重新上电到稳定状态。Selective Precharge的outputs维持不变,Retention的outputs悬空。

Power-down mode:

VDDCE 和VDDPE下电,存储数据丢失。

RAM的macro不包含power gating cells,需要在外部插入。ROM则不需要。

RTL层面上的低功耗

以上提到的是UPF层面的低功耗策略,一般RTL层面的低功耗设计,偏向于一种良好的coding stype;粗略总结如下

1. 时序逻辑中的DFF,通过直接例化标准的DFF单元实现;load-enable的DFF,综合工具自动插入ICG单元。

2. 数据通路的payload,增加load-enable信号,减少不必要的反转。

3. 数据通路不需要复位信号,节省面积,如通用寄存器组。

4. 锁存器比寄存器面积小,功耗低,在特定场合可以使用。但是注意锁存器对时序分析的影响,谨慎使用。

5. 在sram选型上,选择面积压缩比高的sram;尽量避免使用双端口sram。

6.减少读取sram的次数;在连续地址的读中,可以利用sram输出保持不变的特性,例如取指宽度是32bit,sram宽度是64bit;第二次取指时,可以不使能sram的CS信号;在cache中,增加predict机制,减少对sram的读取;在cache中,串行操作,先读Tag_mem确定way,再读Data_mem,节省功耗(因为已确定是哪条way,不用把所有way的数据都读出)。串行操作相比并行操作多了一个cycle latency,但是频率和功耗都更佳。

7. 对sram进行合理的bank划分,平衡时序和功耗。

8. 对sram做clock gating处理;sram漏电功耗大,或者直接做power gating处理。

9. 从代码逻辑上出发,复用组合逻辑,节省面积和功耗;避免使用乘/除大面积运算单元,转为使用加减法。

10.对于大量组合逻辑的单元,在时序允许的情况下,增加一级与门,在空闲为0,避免组合逻辑的不必要反转,节省动态功耗。

————————————————

版权声明:本文为CSDN博主「Holden_Liu」的原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接及本声明。

原文链接:https://blog.csdn.net/Holden_Liu/article/details/118250226